- •Введение

- •Расшифровка и анализ задания

- •2.2 Генератор тактовых импульсов

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.8 Программируемый таймер кр580ви53

- •3.3 Подключение устройств памяти и ввода-вывода к магистралям

- •4.3 Разработка контроллера прямого доступа к памяти

- •4.4 Расширенная структурная схема микропроцессорной системы

- •5 Разработка алгоритма работы микропроцессорной

- •6 Реализация ес1834 – ппэвм комбината "Роботрон" на

- •Заключение

- •Список используемых источников

- •67 Изм. Лист № Докум. Подпись Дата Уитс.161ххх.122 пз Лист.

3.3 Подключение устройств памяти и ввода-вывода к магистралям

микроЭВМ

В микропроцессорных системах, построенных на основе МП БИС К1810ВМ86, могут быть использованы 8-и 16-разрядные устройства ввода—вывода и 16-разрядные устройства памяти. С МП К1810ВМ88 используются только 8-разрядные устройства или 16-разрядные с применением специальной схемы преобразования разрядности магистрали.

Вариант подключения устройств памяти и ввода—вывода к магистралям МП К1810ВМ86 показаны на рисунок 22.

При подключении 8-разрядных

УВВ к старшему или младшему байту

магистрали данных на дешифратор адреса

подаются также сигналы АО и

![]() ,

указывающие на обращение процессора

соответственно к младшему и старшему

байтам.

,

указывающие на обращение процессора

соответственно к младшему и старшему

байтам.

Рисунок 22 — Подключение к магистралям микроЭВМ устройств памяти и

ввода-вывода

Если МП БИС работает в

минимальном режиме и для обращения

к устройствам используются управляющие

сигналы

![]() и

и

![]() ,

то дешифратор адреса памяти и УВВ должен

распознавать сигнал

,

то дешифратор адреса памяти и УВВ должен

распознавать сигнал

![]() и в зависимости от его состояния

формировать сигналы выбора устройств

памяти или ввода—вывода.

и в зависимости от его состояния

формировать сигналы выбора устройств

памяти или ввода—вывода.

Для упрощения в дальнейших схемах сигналы, участвующие в выборке устройств, не будут показываться.

4 РАЗРАБОТКА ПОДСИСТЕМ ВВОДА/ВЫВОДА, ПРЕРЫВАНИЙ, ПДП

4.1 Программируемый параллельный интерфейс подсистемы ввода/

вывода КР580ВВ55

Ммкропроцессорная БИС программируемого параллельного интерфейса КР58ОВВ55 предназначена для организации ввода/вывода параллельной информации различного формата и позволяет реализовать большинство известных протоколов обмена по параллельным каналам. БИС программируемого параллельного интерфейса (ППИ) может использоваться для сопряжения микропроцессора со стандартным периферийным оборудованием (дисплеем, телетайпом, накопителем).

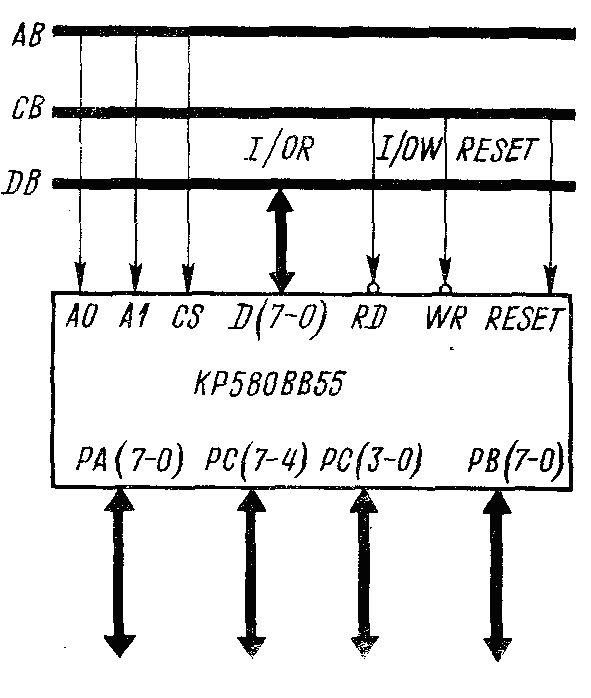

Структурная схема ППИ приведена на рисунке 23.

Рисунок 23 — Структурная схема программируемого параллельного

интерфейса КР580ВВ55

В состав БИС входят: двунаправленный 8-разрядный буфер данных (ВD), связывающий ППИ с системной шиной данных; блок управления записью/чтением (RWCU), обеспечивающий управление внешними и внутренними передачами данных, управляющих слов и информации о состоянии ППИ; три 8-разрядных канала ввода/вывода (РОRТ А, В и С) для обмена информацией с внешними устройствами; схема управления группой А (СUA), вырабатывающая сигналы управления каналом А и старшими разрядами канала С[РС(7-4)]; схема управления группой В (СUВ), вырабатывающая сигналы управления каналом В и младшими разрядами канала С[РС(3-0)].

Таблица 10 — Описание выводов программируемого параллельного

интерфейса КР580ВВ55.

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

D(7-0) |

27; 28; 29; 30; 31; 32; 33; 34 |

Вход/выход данных |

|

RD |

5 |

Чтение; L-уровень сигнала разрешает считывание информации из регистра, адресуемого по входам А0, А1 на шину D(7-0) |

|

WR |

36 |

Запись; L-уровень сигнала разрешает запись информации с шипы D(7—0) в регистр ППИ, адресуемый по входам А0, А1 |

|

АО, А1 |

9; 8 |

Входы для адресации внутренних регистров ППИ |

|

RESET |

35 |

Сброс; H-уровень сигнала обнуляет регистр управляющего слова и уста-навливает все порты в режим ввода |

|

CS |

6 |

Выбор микросхемы; L-уровень сигнала подключает ППИ к системной шине |

|

РА(7-0) |

37; 38; 39; 40; 1; 2; 3; 4 |

Вход/выход канала А |

|

РВ(7-0) |

15; 24; 23; 22; 21; 20;19; 18 |

Вход/выход канала В |

|

РС(7-0) |

10; 11; 12; 13; 17; 16; 15; 14 |

Вход/выход канала С |

|

Ucc |

26 |

Напряжение питания ( + 5 В) |

|

GND |

7 |

Напряжение питания (0 В) |

Назначения входных, выходных и управляющих сигналов ППИ приведены при описании выводов микросхемы в таблице 9. Сопряжение БИС КР580ВВ55 со стандартной системной шиной показано на рисунке 10. Сигналы управления работой ППИ подаются на блок К\УС11 и вместе с адресными входами АО, А1 задают вид операции, выполняемой БИС.

Рисунок 24 — Схема сопряжения программируемого параллельного

интерфейса КР580ВВ55 со стандартной системной шиной

Основные электрические параметры микросхемы КР580ВВ55 следующие:

Выходное напряжение логического нуля UOL, В 0,4.

Выходное напряжение логической единицы UOH, В 2,4.

Ток потребления от источника питания ICC, мА 60.

Ток утечки каналов А, В, С, D

при невыбранном режиме IIOZ, мкА 100,...,100;

Ток утечки на управляющих входах IIL, мкА —10,...,10.

4.2 Подсистема прерываний

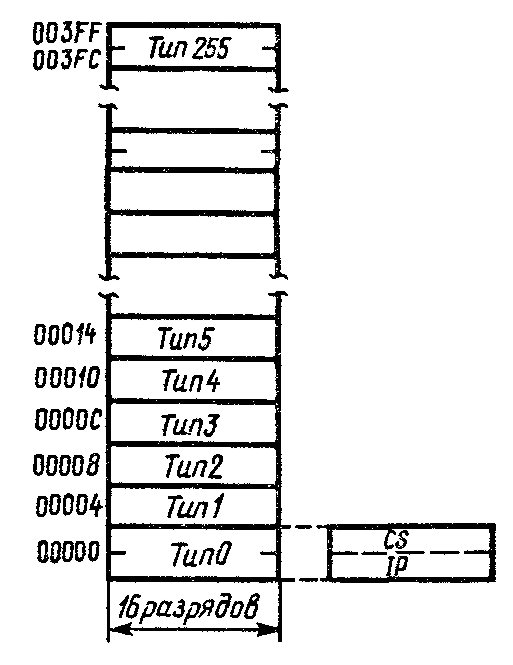

Микропроцессорная БИС имеет простую и изменяющуюся систему прерываний. Прерывания могут быть вызваны внешними устройствами, выполнением соответствующих команд, а также инициированы самой МП БИС (внутренние прерывания). Существует 256 различных типов прерываний.

Для подачи прерываний в МП БИС имеются два входа:

INTR – Interrupt Reguest и NMI – Non Masking Interrupt (рисунок 25).

Рисунок 25 – Возможные способы формирования прерываний в МП

К1810ВМ6

Вход INT обычно используется для подключения программируемого блока приоритетных прерываний (БПП). По функциональному назначению микросхема БПП аналогична схеме КР580ИК59 и является дальнейшей ее модификацией. Режимы работы БПП могут быть заданы программно. Основные задачи БПП – получение запросов прерывания от различных внешних устройств, определение сигнала с высшим приоритетом, формирование запроса прерывания на входе МП БИС и сообщение номера текущего обслуживаемого внешнего устройства. Прерывания по входу INT могут быть маскированы путем записи «0» или «1» в разряд 1 флагового регистра МП БИС.

Микропроцессорная БИС реагирует на поступление запроса прерывания по входу INTR последовательным выполнением двух машинных циклов обслуживания прерывания: первый указывает БПП, что запрос прерывания был воспринят, и начинает обслуживаться; на втором БПП выдает на МД байт данных, указывающий тип прерывания (0–255). При работе МП БИС с максимальной конфигурацией системы на интервале двух циклов INTA на выходе LOCK формируется сигнал, запрещающий другим процессорам системы пользоваться магистралями.

Внешние устройства могут подавать запросы прерывания на второй вход NMI МП БИС. На этом входе запрос воспринимается и записывается в МП БИС по фронту поступающего импульса, не может быть маскирован и имеет высший приоритет по отношению к запросам, поступающим на вход INTR. Обычно вход NMI используют для указания МП БИС о каких-либо сбоях в системе (сбоях в источнике питания, ошибках в памяти). При определении наличия сигнала на входе NMl МП БИС нет необходимости получать код для инициализации процесса обслуживания прерывания и соответственно она не формирует два машинных цикла INTA в ответ на запрос по входу NMI.

Внутренние прерывания формируются за счет выполнения МП БИС команды прерывания (тип команды зависит от источника прерывания).

При установке флага переполнения О=1 в результате выполнения какой-либо команды программы формируется команда прерывания – INTO (прерывание по переполнению).

Микропроцессорная БИС формирует прерывание сразу же после выполнения команд DIV или IDIV, если частное от деления больше, чем разрядность используемых регистров.

При установке флага Т=1 МП БИС автоматически формирует прерывание, которое воздействует сразу после выполнения любой текущей команды. Этот тип прерывания называют одношаговым или первым типом, и он является мощным средством при отладке программ. При выполнении одношагового типа прерывания МП БИС производит обычную последовательность операций, а именно записывает в стек флаги МП БИС, содержимое регистров CS и IP. В дополнение к этому очищаются флаги I и Т. В регистры CS и IP записываются соответственно из адресов 00006, 00007 и 00004, 00005 новые значения базового адреса сегмента и смещения для передачи управления на соответствующую подпрограмму обслуживания прерывания. В качестве такой подпрограммы может быть использована подпрограмма выдачи результата выполнения программы на печать, дисплей и т. д. По окончании выполнения подпрограммы после получения команды IRET (возврат из подпрограммы) из стека извлекаются и записываются в МП БИС флаги и содержимое регистров IP и СР. Из приведенных пояснений ясно, что при выполнении одношагового типа прерывания МП БИС обслуживает прерывания обычным способом. Однако обеспечение вывода результатов выполнения отдельных блоков в программе или даже отдельных команд с целью их последующего анализа путем задания в нужном месте программ режима одношаговых прерываний является удобным средством при исследовании работы программ.

Типы внутренних прерываний имеют ряд общих свойств:

1) код прерывания сообщается МП БИС перед командой или включен в команду прерывания;

2) на выходе МП БИС не формируются сигналы INTA;

3) за исключением одношагового типа, внутренние прерывания не могут быть программно отключены;

4) за исключением одношагового типа, любой из внутренних прерываний имеет более высокий приоритет по отношению к внешним прерываниям.

Любой из 256 возможных типов прерывания характеризуется вектором прерывания. Векторы прерывания занимают 1К байт адресного пространства. На рисунке 25 показано распределение начал векторов прерывания по адресам памяти. Как видно из рисунка, каждый вектор занимает четыре ячейки памяти, при этом два младших адреса в векторе используются для записи смещения в сегменте, а два старших — для записи базового адреса сегмента.

Рисунок 26 – Распределение векторов прерываний в памяти микроЭВМ

Формирование адреса передачи управления на соответствующую подпрограмму обслуживания прерывания в BIU происходит так же, как и при обращении к любой ячейке памяти, а именно: содержимое двух младших адресов вектора прерывания записывается в регистр IP, coдержимое старших двух адресов записывается в регистр CS. После этого содержимое CS смещается на четыре разряда влево и откладывается с содержимым IP. Полученное 20-разрядное число определяет адрес начала подпрограммы прерывания.

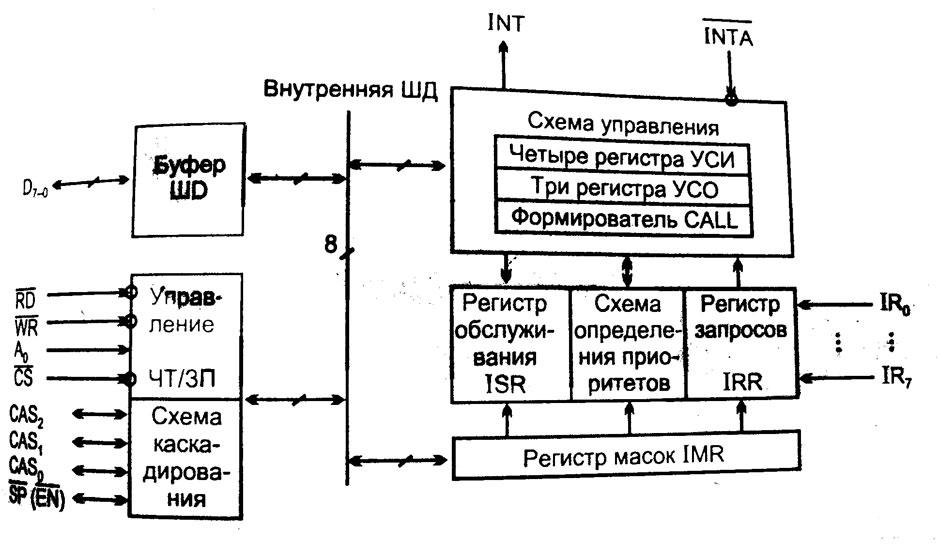

В данной микропроцессорной системе используется контроллер прерываний К1810ВН59А. Структурная схема изображена на рисунке 26.

Рисунок 27 – Структурная схема контроллера прерываний К1810ВН59А

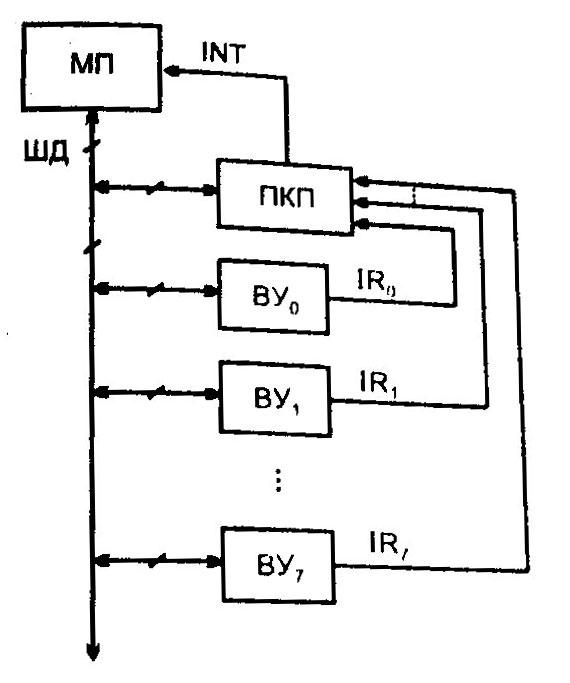

Включение контроллера прерываний в систему показано на рисунке 27.

Рисунок 28 – Включение контроллера прерываний в МПС

Контроллер принимает запросы от внешних устройств, определяет, какой из незамаскированных запросов имеет наивысший приоритет, сравнивает его с приоритетом текущей программы и при соответствующих условиях выдает запрос прерывания INT для МП. После подтверждения запроса МП должен получить от котроллера информацию, которая укажет на подпрограмму, соответствующую данному ВУ.