- •Введение

- •Расшифровка и анализ задания

- •2.2 Генератор тактовых импульсов

- •2.3 Буферный регистр кр580ир82

- •2.4 Шинный формирователь кр580ва86

- •2.5 Контроллер шин к1810вг88

- •2.6 Арбитр шин к1810вб89

- •2.8 Программируемый таймер кр580ви53

- •3.3 Подключение устройств памяти и ввода-вывода к магистралям

- •4.3 Разработка контроллера прямого доступа к памяти

- •4.4 Расширенная структурная схема микропроцессорной системы

- •5 Разработка алгоритма работы микропроцессорной

- •6 Реализация ес1834 – ппэвм комбината "Роботрон" на

- •Заключение

- •Список используемых источников

- •67 Изм. Лист № Докум. Подпись Дата Уитс.161ххх.122 пз Лист.

2.2 Генератор тактовых импульсов

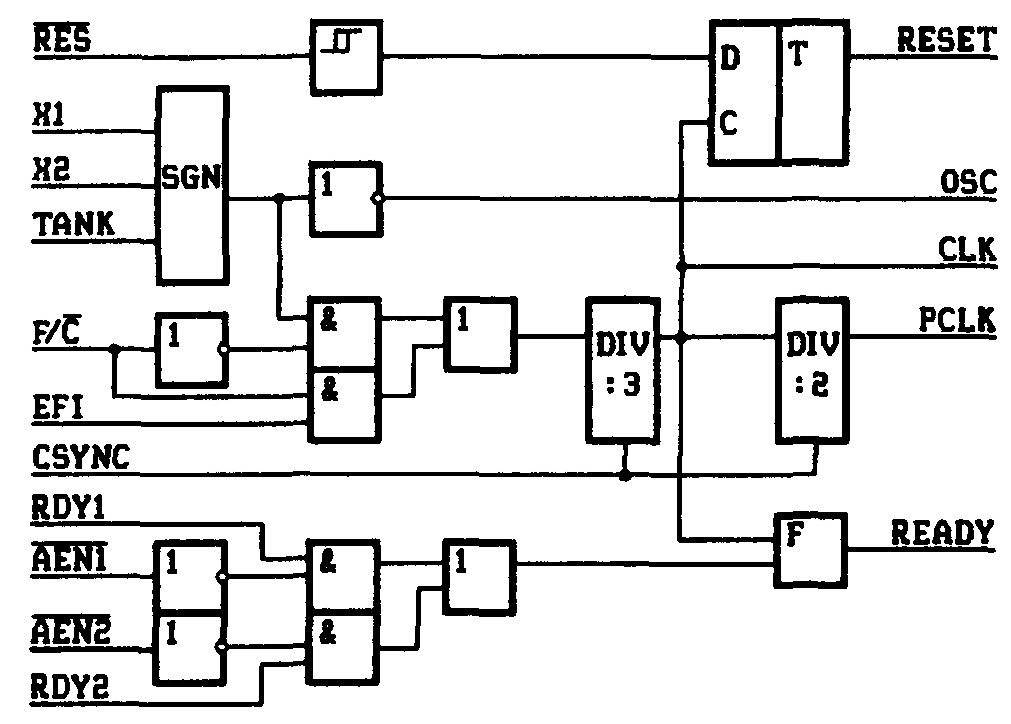

Генератор тактовых импульсов (ГТИ) К1810ГФ84 предназначен для управления ЦП К1810ВМ86 и периферийными устройствами, а также для синхронизации сигналов READY с тактовыми сигналами ЦП и сигналов интерфейсной шины Multibus. Генератор тактовых импульсов (рисунок 4) включает схемы формирования тактовых импульсов (OSC, CLK, PCLK), сигнала сброса (RESET) и сигнала готовности (READY).

Рисунок 3 - Структурная схема ГТИ К1810ГФ84

Схема формирования тактовых импульсов вырабатывает сигналы: CLK – тактовой частоты для ЦП К1810ВМ86, PCLK – тактовой частоты для управления периферийными БИС, OSC – тактовой частоты задающего генератора, необходимые для управления устройствами, входящими в систему, и для синхронизации. Сигналы синхронны, их частоты связаны соотношением: FOSC=3Fclk=6Fpclk режиме внутреннего генератора и FEFI=3Fclk=6Fpclk в режиме внешнего генератора.

Сигналы могут формироваться из колебаний основной частоты кварцевого резонатора, подключаемого к входам X1, Х2, или третьей гармоники кварцевого резонатора, выделяемой LC-фильтром или от внешнего генератора, подключаемого ко входу EFI.

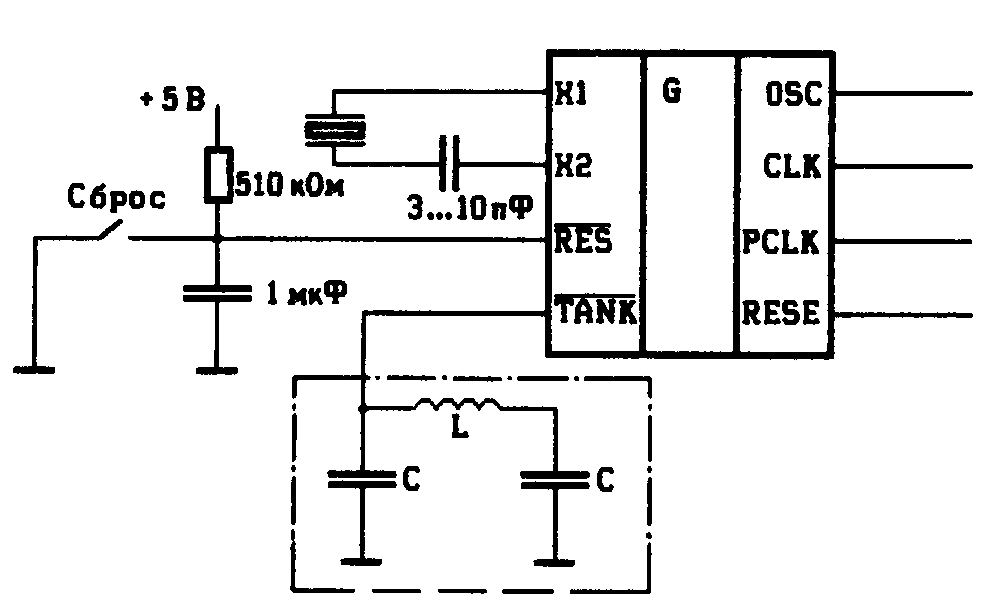

Выбор режима функционирования определяется потенциалом на входе F/C. Если этот вход подключен к «земле», то ГТИ работает в режиме формирования сигналов от внутреннего генератора (SGN), если на F/C подается высокий потенциал – то в режиме формирования сигналов от внешнего генератора. Схема формирования сигнала сброса RESET имеет на входе триггер Шмидта, а на выходе – триггер, формирующий фронт сигнала RESET по срезу CLK. Обычно ко входу RES подключается RC-цепь, обеспечивающая автоматическое формирование сигнала при включении источника питания (рисунок 4).

Рисунок 4 - Схема подключения к ГТИ кварцевого резонатора

Входной сигнал READY ЦП К1810ВМ86 используется для подтверждения готовности к обмену. Высокий уровень напряжения на входе указывает на наличие данных на ШД. Схема формирования этого сигнала в ГТИ построена так, чтобы упростить включение системы в интерфейсную шину стандарта Multibus, и имеет две пары идентичных сигналов RDY1, AEN1 и RDY2, AEN2, объединенных схемой ИЛИ. Сигналы RDY формируются элементами, входящими в систему, и свидетельствуют об их готовности к обмену.

Основные электрические параметры микросхемы К1810ГФ84:

Входное напряжение логического

нуля UIL

В

![]() 0,8

0,8

Входное напряжение логической

единицы UIH

, В

![]() 2,0

2,0

Напряжение логической

единицы для входа сброса UIH

, В

![]() 2,6

2,6

Выходное напряжение

логического нуля UOL,

В

![]() 0,45

0,45

Выходное напряжение логической единицы UOH, В:

на выходе CLK

![]() 4

4

на всех других выходах

![]() 2,4

2,4

Напряжение входного

гистерезиса UIH

-UIL,

В

![]() 0,25

0,25

Ток потребления источника

питания ICC,

мА

![]() 140

140

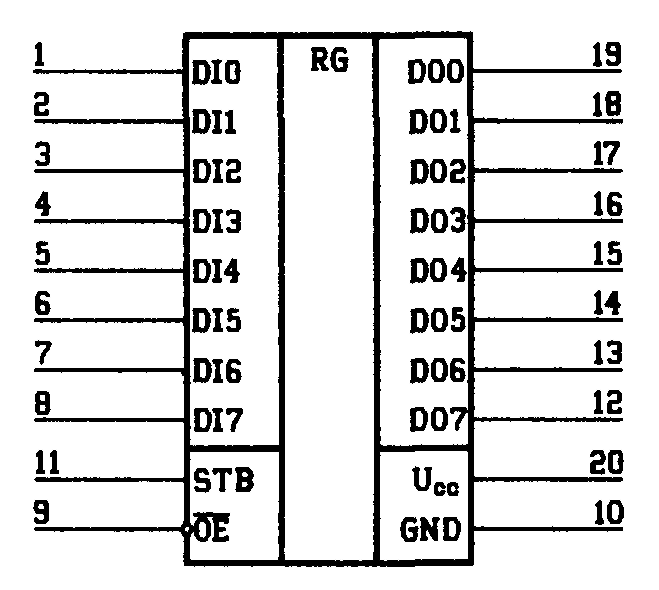

2.3 Буферный регистр кр580ир82

Буферный регистр КР580ИР82 представляет собой 8-разрядные парал-лельные регистр с тристабильными выходами. Он используется для реализации схем фиксации, буферизации и мультиплексирования в микропроцессорных системах на базе МП К580ИК80А и К1810ВМ86. На выходах микросхемы КР580ИР82 генерируются неинвертированные входные данные.

Структурная схема буферного регистра приведена на рисунке 4, а назначение входных и выходных сигналов указано при описании выводов микросхем в таблице 5.

Запись входных данных в буферные регистры производится при переходе сигнала уровне сигнала ОЕ, выходы буферных регистров находятся в высокоимпедансном состоянии.

Рисунок 5 — Структурная схема буферного регистра КР580ИР82

Основные электрические параметры микросхемы КР580ИР82 следующие:

Выходное напряжение логического нуля UOL, В < 0,5

Выходное напряжение логической единицы UOH, В > 2,4

Входное напряжение логического нуля UIL, В < 0,8

Входное напряжение логической единицы UIH, В > 2,0

Ток потребления от источника питания IСС, мА < 160

Выходной ток утечки IOZ, мкА < 50

Время задержки tIO, не:

с инвертированием < 40

без инвертирования < 45

Рисунок 6 - Условно-графическое обозначение К580ИР82

Таблица 4 — Описание выводов буферного регистра КР580ИР82

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

DI(7 - 0) |

8; 7; 6; 5; 4; 3; 2; 1 |

Входы данных |

|

STB |

11 |

Вход сигнала стробирования |

|

ОЕ |

9 |

Вход сигнала разрешения ввода |

|

DO(7 - 0) |

12; 13; 14; 15; 16; 17; 18; 19 |

Выходы данных |

|

UСС |

20 |

Напряжение питания ( + 5 В) |

|

GND |

10 |

Напряжение питания (0 В) |

D17-D10 – линии входных данных;

D07-D00 – линии выходных данных;

STB – стробирующий сигнал;

![]() –

разрешение выдачи данных.

–

разрешение выдачи данных.

При сигнале высокого уровня

на входе STB

состояние входных линий D17-D10

передается на выходные линии D07-D00.

Запоминание (защелкивание) в

информационных триггерах осуществляется

при переходе сигнала STB

от высокого уровня к низкому (по срезу

сигнала STB).

Сигнал

![]() управляет выходными буферами: при

управляет выходными буферами: при

![]() =0

буфер отпирается, при

=0

буфер отпирается, при

![]() =1

он устанавливается в

z-состояние.

Сигнал

=1

он устанавливается в

z-состояние.

Сигнал

![]() не влияет ни на состояния информационных

триггеров, ни на функцию записи.

не влияет ни на состояния информационных

триггеров, ни на функцию записи.