- •1 Расшифровка и анализ задания

- •1.2 Реакция системы на внешние события

- •2.1.1 Организация архитектуры к1816ве51.

- •2.1.2 Набор регистров мк51

- •2.1.3 Организация памяти мк51

- •2.1.5 Последовательный канал связи

- •2.1.6 Таймеры/счетчики

- •2.1.7 Система прерываний

- •2.1.8 Система команд мк ве51

- •2.2 Функциональное описание ве51

- •2.2.1 Интерфейс расширения

- •2.2.2 Работа таймеров/счетчиков

- •2.2.3 Работа последовательного канала связи

- •2.2.4 Работа с внешней памятью программ и памятью данных

- •2.2.5 Работа с портами

- •3 Разработка подсистемы памяти

- •3.1 Описание микросхемы кр537ру8

- •3.3 Подключение озу и пзу к системной шине

- •4 Разработка подсистем ввода/вывода, прерываний и пдп

- •4.1 Аналогово-цифровой преобразователь

- •4.2 Цифроаналоговый преобразователь

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5 Контроллер клавиатуры/дисплея кр580вд79

- •4.5.1 Общие сведения о мс кр580вд79

- •4.5.2 Управление ккд с помощью сигналов на внешних выводах

- •4.5.3 Режимы работы клавиатуры

- •4.5.4 Режимы работы дисплея

- •4.5.5 Байт состояния памяти клавиатуры/датчиков

- •5 Разработка программного обеспечения

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе микропроцессора к1816ве51

- •6.1 Основные технические данные и характеристики

- •6.1.1 Параметры назначения:

- •6.2 Устройство

- •6.2.1 Общие сведения

- •6.2.2 Принцип действия

2.1.5 Последовательный канал связи

В состав ВЕ51 входит дуплексный канал последовательной связи с буферизацией, который может быть запрограммирован для работы в одном из четырех режимов:

режим 0 - синхронный последовательный ВВ со скоростью OSC/12;

режим 1- асинхронный с 10-битовым кадром и переменной скоростью передачи;

режим 2 - асинхронный с 11-битовым кадром и фиксированной скоростью передачи OSC/32 или OSC/64;

режим 3 - асинхронный с 11-битовым кадром и переменной скоростью передачи.

Входные и выходные данные хранятся в буферном регистре SBUF с адресом 99Н. Управление работой приемопередатчиков осуществляется через слово управления и состояния SCON, расположенное в регистре по адресу 98Н.

2.1.6 Таймеры/счетчики

Предназначены для подсчета внешних событий, для получения программно управляемых временных задержек, выполнения времязадающих функций ОМЭВМ.

В состав блока входят:

- два 16-ти разрядных регистра Т/С 0, Т/С 1;

- 8-ми разрядный регистр режимов Т/С (ТМ0D);

- 8-ми разрядный регистр управления (ТСОN);

- схема инкремента;

- схема фиксации INT0, INT1, Т0, Т1;

- схема управления флагами;

- логика управления Т/С.

Два 16-разрядных регистра Т/С 0 и Т/С 1 выполняют функцию хранения содержимого счета. Каждый из них состоит из пары 8-ми разрядных регистров, соответственно ТH0, ТL0 и ТH1, ТL1. Причем регистры ТН0, ТH1 - старшие, регистры ТL0, ТL1 - младшие 8 разрядов. Каждый из 8-ми разрядных регистров может быть использован, как РОН, если Т/С не используются (бит TR0 для Т/С 0 и бит TR1 для Т/С 1 в регистре управления TCON равен "0").

Регистр режимов Т/С (TMOD) предназначен для приема и хранения кода, определяющего:

- один из 4-х возможных режимов работы каждого Т/С;

- работу в качестве таймеров или счетчиков;

- управление Т/С от внешнего вывода.

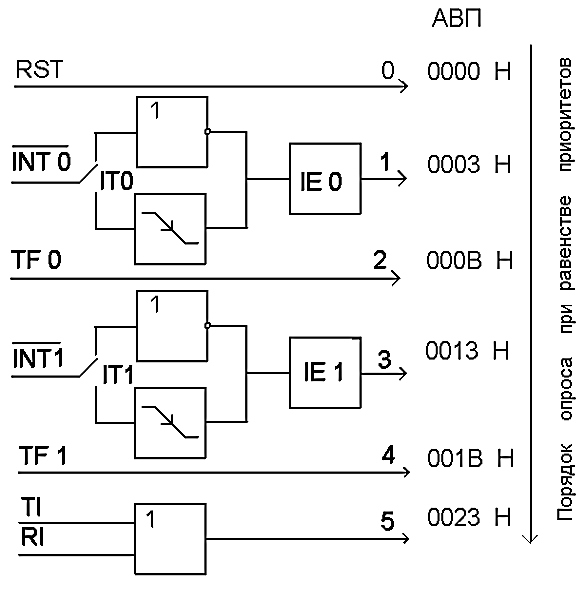

2.1.7 Система прерываний

Упрощенная схема прерываний МК51 приведена на рисунке 6.

Рисунок 6 - Упрощенная схема реализации прерываний МК ВЕ51

Внешние прерывания INT0 и INT1 могут быть вызваны либо низким логическим уровнем, либо переходом из 1 в 0 на входах МК51 в зависимости от значений IT0 и IT1 - управляющих бит, представленных в регистре TCON (timer control register - регистр управления таймерами) разрядами TCON.0 и TCON.2. При появлении запросов от внешних источников прерываний устанавливаются флаги IE0 и IE1 в разрядах TCON.1 и TCON.3. При переполнении таймеров устанавливаются флаги запроса прерываний от таймеров TF0 и TF1 (TCON.5 и TCON.7), которые сбрасываются автоматически при передаче управления программе обслуживания прерываний. Флаги запросов на прерывания от приемника и передатчика RI и TI устанавливаются универсальным приемопередатчиком и должны сбрасываться программно.

Два регистра специальных функций IE и IP позволяют управлять режимами прерываний и уровнями приоритета. Каждому запросу соответствует адрес вектора прерывания в поле адресов памяти программ (рисунок 5). По адресу вектора прерывания должна быть записана команда безусловного перехода (JMP) к подпрограмме обслуживания прерывания. Возврат в основную программу осуществляется по команде RETI.