- •1 Расшифровка и анализ задания

- •1.2 Реакция системы на внешние события

- •2.1.1 Организация архитектуры к1816ве51.

- •2.1.2 Набор регистров мк51

- •2.1.3 Организация памяти мк51

- •2.1.5 Последовательный канал связи

- •2.1.6 Таймеры/счетчики

- •2.1.7 Система прерываний

- •2.1.8 Система команд мк ве51

- •2.2 Функциональное описание ве51

- •2.2.1 Интерфейс расширения

- •2.2.2 Работа таймеров/счетчиков

- •2.2.3 Работа последовательного канала связи

- •2.2.4 Работа с внешней памятью программ и памятью данных

- •2.2.5 Работа с портами

- •3 Разработка подсистемы памяти

- •3.1 Описание микросхемы кр537ру8

- •3.3 Подключение озу и пзу к системной шине

- •4 Разработка подсистем ввода/вывода, прерываний и пдп

- •4.1 Аналогово-цифровой преобразователь

- •4.2 Цифроаналоговый преобразователь

- •4.3 Контроллер прямого доступа к памяти кр580вт57

- •4.4 Многорежимный буферный регистр к589ир12

- •4.5 Контроллер клавиатуры/дисплея кр580вд79

- •4.5.1 Общие сведения о мс кр580вд79

- •4.5.2 Управление ккд с помощью сигналов на внешних выводах

- •4.5.3 Режимы работы клавиатуры

- •4.5.4 Режимы работы дисплея

- •4.5.5 Байт состояния памяти клавиатуры/датчиков

- •5 Разработка программного обеспечения

- •5.2 Разработка блок-схемы управляющей системы

- •6 Реализация устройства на базе микропроцессора к1816ве51

- •6.1 Основные технические данные и характеристики

- •6.1.1 Параметры назначения:

- •6.2 Устройство

- •6.2.1 Общие сведения

- •6.2.2 Принцип действия

3.3 Подключение озу и пзу к системной шине

Внешняя оперативная память доступна МК по командам пересылки МОVХ А, @R и МOVX @R,А , которые по косвенному адресу (регистры R0 и R1) выполняют операции передачи байта между ВПД и аккумулятором. Сигналом ALE косвенный адрес, выводимый по шине BUS, фиксируется в многорежимном буферном регистре МБР. Сигналы WR и RD определяют режим работы БИС ОЗУ. Так как косвенный адрес имеет формат байта, то схема на рисунке 8 обеспечивает адресацию 256 ячеек ОЗУ в дополнение к 64 ячейкам резидентной памяти данных МК48.

Внешняя постоянная память подключаются к шине BUS своими информационными выходами. Младший байт адреса по сигналу ALE фиксируется на внешнем буферном регистре.

Схема подключения внешней памяти данных и команд представлена на рисунке 13. Для обращения к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных вырабатывается сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. То есть память программ доступна только для чтения, а память данных доступна и для чтения и для записи любой информации, записанной в двоичном коде.

Рисунок 13 - Подключение внешней памяти данных и программ к ОМЭВМ

4 Разработка подсистем ввода/вывода, прерываний и пдп

В разрабатываемой микропроцессорной системе предусматривается следующая номенклатура устройств:

1) АЦП – для ввода информации с цифровых датчиков x1, x2, x3, а также для ввода информации с аналоговых датчиков NU1,NU2,NU3.

2) ЦАП – для вывода цифровых управляющих сигналов y1,y2,y3.

3) КПДП - для организации высокоскоростного обмена данными между памятью системы и периферийными устройствами.

4) Контроллер клавиатуры/дисплея (ККД) – для сопряжения с клавиатурой и дисплеем. Клавиатура предназначена для ввода константы К с пульта оператора; с дисплея осуществляется вывод 8 – разрядного кода Y4 на ЦАП, вывод значений x1, x2, x3, y1, y2, y3, NU1, Y4 а так же вывод аварийной сигнализации на пульт оператора.

4.1 Аналогово-цифровой преобразователь

Аналого-цифровой преобразователь обеспечивает сопряжение источников аналоговых сигналов с микропроцессорными устройствами обработки, а ЦАП предназначены, в основном, для вывода из процессора результатов обработки информации на управляемые объекты.

В качестве устройство ввода информации выбран аналогово-цифровой преобразователь К1113ПВ1.

Полупроводниковая БИС функционально завершенного АЦП типа К111ЗПВ1 предназначена для применения в электронной аппаратуре в составе блоков аналогового ввода. МС выполняет функцию аналого-цифрового преобразования однополярного или биполярного входного сигнала с представлением результатов преобразования в параллельном двоичном коде. Она содержит все функциональные узлы АЦП. Выходные каскады позволяют считывать результат преобразования непосредственно на шину данных МП. По уровням входных и выходных сигналов АЦП сопрягается с цифровыми ТТЛ ИС.

МС представляет собой функционально законченный 10-разрядный АЦП, сопрягаемый с микропроцессором. Обеспечивает преобразование как однополярного напряжения (вывод 15 соединяется с выводом 16) в диапазоне 0...9,95 В, так и биполярного напряжения в диапазоне -4,975...+4,975 В в параллельный двоичный код. В состав ИС входят ЦАП, компаратор напряжения регистр последовательного приближения (РПП), источник опорного напряжения (ИОН), генератор тактовых импульсов (ГТИ), выходной буферный регистр с тремя состояниями, схемы управления. Выходные каскады с тремя состояниями позволяют считывать результат преобразования непосредственно на шину данных микропроцессора. По уровням входных и выходных логических сигналов сопрягаются с ТТЛ схемами. В ИС выходной ток ЦАП сравнивается с током входного резистора от источника сигнала и формируется логический сигнал РПП. Стабилизация разрядных токов ЦАП осуществляется встроенным ИОН. Тактирование РПП обеспечивается импульсами встроенного ГТИ с частотой следования 300...400 кГц. Установка РПП в исходное состояние и запуск его в режим преобразования производится по внешнему сигналу "гашение и преобразование". По окончанию преобразования АЦП вырабатывает сигнал "готовность данных" и информация из РПП поступает на цифровые входы через каскады с тремя состояниями. Корпус К1113ПВ1(A-B) типа 2104.18-1, масса не более 2,5 г.

Электрические параметры БИС К1113ПВ1.

Номинальное

напряжение питания Uп1, В 5

![]() 5

%.

5

%.

Номинальное

напряжение питания Uп2, В -15

![]() 5

%.

5

%.

Выходное напряжение низкого уровня, В не более 0,4.

Выходное

напряжение высокого уровня, %

![]() 0,3.

0,3.

Ток потребления, мА не более 10.

Входной

ток высокого (низкого) уровня, мкА ![]() 40.

40.

Ток

утечки на выходе, мкА ![]() 40.

40.

Время преобразования, мкс не более 30.

Нелинейность

от полной шкалы, % ![]() 0,075.

0,075.

Абсолютная погрешность преобразования в

конечной

точке шкалы от полной шкалы, % ![]() 0,4.

0,4.

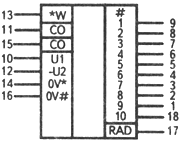

Условное графическое изображение МС представлено на рисунке 14.

1 – 9 – разряды с первого по девятый; 10 - напряжение питания Uп1; 11 - гашение и преобразование; 12 - напряжение питания -Uп2; 13 - вход аналоговый; 14 - аналоговая "земля"; 15 - управление сдвигом нуля; 16 - цифровая "земля"; 17 - готовность данных;18 - десятый разряд (младший).

Рисунок 14 – Цоколевка микросхемы К1113ПВ1

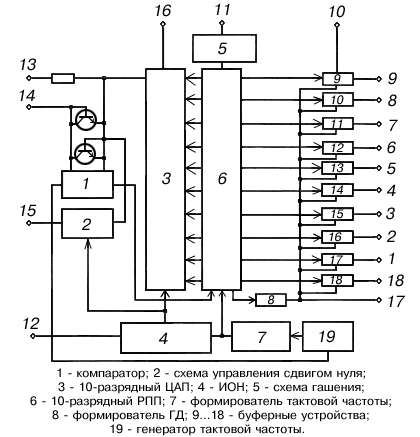

Функциональная схема АЦП приведена на рисунке 15.

1 - компаратор; 2 - схема управления сдвигом нуля; 3 - 10-разрядный ЦАП; 4 - ИОН; 5 - схема гашения; 6 - 10-разрядный РПП; 7 - формирователь тактовой частоты; 8 - формирователь; 9 - 18 – буферные устройства; 19 - генератор тактовой частоты.

Рисунок 15 – Структурная схема микросхемы К1113ПВ1