23. Машинный цикл выборка (чтение памяти)

Первым машинным циклом всегда является цикл выборка, на протяжении которого осуществляется выборка из памяти байта кода команды по адресу, определяемому содержимым указателя команд (IP).

Содержимое IP в цикле увеличивается на 1.

Для выполнения однобайтных команд с регистровой адресацией требуется 1 цикл – выборка. Для выборки 2-х или 3-х байтных команд кроме цикла «выборка» нужны 1 или 2 МЦ для чтения второго или 2 и 3 байтов команды (циклы чтение памяти).

Этот цикл чтение памяти необходим также при выполнении команд с косвенной или прямой адресацией.

Для записи операндов или сохранения адресов при выполнении команд пересылок необходимы МЦ «запись в память».

В командах с обращением к стеку необходимы циклы «чтение стека» и «запись в стек».

Адрес памяти определяется указателем стека (SP). Для выполнения команд ввода/вывода выполняется МЦ «ввод и вывод».

Для организации прерываний и остановки проца циклы 8, 9, 10.

Каждый МЦ проца идентифицируется байтом, называемым байтом состояния (слово состояния процессора).

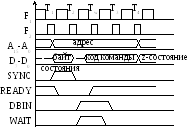

Байт состояния выдается на ШД в начале каждого МЦ и сопровождается одновременной выдачей сигнала SYNC синхронизации на одноименный контакт МП.

Байт состояния несет информацию о последующих действиях МП. Его можно заполнить по сигналу SYNC (синхронизации) и сформировать определенные управляющие сигналы.

Такты отсчитываются по передним фронтам последовательности F1, а микрооперации в каждом такте определяются передним фронтом последовательности F2.

При тактовой частоте 2 МГц продолжительность такта составляет 0.5 мс. Сигналы на линиях А15-А0 Д7-Д0 изображены в виде линий L и H-уровней. На этих линиях указывается тип информации (присутствие адреса или данных) z-состояние – высокоимпедансное состояние.