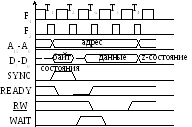

24. Машинный цикл Запись в память

В первом машинном такте Т1 на шину адреса А15-А0 выдается адрес (содержимое указателя команд IP, если выполняется цикл выборка, или содержимое указателя адреса, если выполняется цикл чтение памяти).

На ШД линии Д7-Д0 выдается байт состояния, а также формируется сигнал синхронизации на одноименном выводе МП.

Во втором такте Т2 заканчивается поступление байта состояния и сигнал синхронизации SYNC, продолжительность которых равна 1 такту.

В МЦ «выборка» содержимое указателя команд увеличив на 1 для адресации следующего байта команды или следующей команды.

В этом же такте УУ МП производит анализ сигналов на выходах READY - готов, и HOLD – запрет захвата, а также контроль выполнения команды HLT – останова.

Если память или внешнее устройство не готов к обмену (READY=0) в следствии того, что поступил сигнал запрос ПДП (HOLD=1) или выполняется команда останова HLT, то обмен данными производиться не может и проц переходит в режим ожидания.

Кроме того может выполняться один из особых режимов захват шин или останов.

В этих режимах осуществляется ожидание сигнала на протяжении нескольких тактов ожидания (Tw), количество которых определяется внешними сигналами.

В такте Т2 READY=0, а в такте Тw-“1”.

В такте Т3 в зависимости от типа машинного цикла осуществляется обращение к памяти, стеку или входному устройству. В результате в МП вводится 1 временная диаграмма или из него выводится 2 временная диаграмма, байт команды, адреса или данных.

В зависимости от типа команды МЦ может содержать такты Т4 и Т5 (не обязательны, например: если для выполнения команды необходима обработка операндов).

В последнем такте команды (Т3, Т4 или Т5) анализируется наличие сигнала INT – запрос прерывания. Если прерывание разрешено (INTE=1), тогда проц переходит к выполнению МЦ «прерывания».