- •Анализ усилительных каскадов на биполярных транзисторах графическим методом

- •1. Цель работы

- •2. Теоретическое введение

- •3. Задание к лабораторной работе

- •4. Содержание отчета

- •5. Контрольные вопросы

- •Схемы смещения в усилителях на биполярных транзисторах. Стабилизация режима

- •1. Цель работы

- •2. Теоретическое введение

- •3. Задание к лабораторной работе

- •4. Контрольные вопросы

- •Исследование свойств усилительных каскадов на биполярных транзисторах

- •1. Цель работы

- •2. Теоретическое введение

- •3. Описание установки

- •4. Задание к лабораторной работе

- •5. Содержание отчета

- •6. Контрольные вопросы

- •Исследование полупроводниковых стабилизаторов напряжения

- •1. Цель работы

- •2. Теоретическое введение

- •2.1. Основные характеристики стабилизаторов

- •2.2. Классификация стабилизаторов напряжения

- •2.3. Стабилизаторы параллельного типа

- •2.3.1. Диодный стабилизатор

- •2.3.2. Транзисторный стабилизатор

- •2.4. Последовательные стабилизаторы напряжения

- •3. Описание установки

- •4. Задание к лабораторной работе

- •5. Содержание отчета

- •6. Контрольные вопросы

- •Рекомендуемая литература

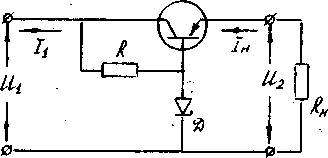

2.3.2. Транзисторный стабилизатор

Максимальная

выходная мощность диодного стабилизатора

зависит от значений

![]() и

и

![]() стабилитрона. Область применения

таких стабилизаторов по мощности можно

расширить, если использовать усилитель

тока на транзисторе (рис.4). Эта схема

работает следующим образом. При

возрастании по какой-либо причине

напряжения

стабилитрона. Область применения

таких стабилизаторов по мощности можно

расширить, если использовать усилитель

тока на транзисторе (рис.4). Эта схема

работает следующим образом. При

возрастании по какой-либо причине

напряжения

![]() происходит увеличение напряжения

происходит увеличение напряжения

![]() и напряжения

и напряжения

![]() ,так

как

,так

как

![]() ,

а

,

а

![]() .

Возрастание

.

Возрастание

![]() вызывает рост

коллекторного тока

вызывает рост

коллекторного тока

![]() ,

что приводит к увеличению падения

напряжения на балластном резисторе,

а это компенсирует начальное возрастание

,

что приводит к увеличению падения

напряжения на балластном резисторе,

а это компенсирует начальное возрастание

![]() .

Так как при работе транзистора в активной

области ток коллектора

.

Так как при работе транзистора в активной

области ток коллектора

![]() экспоненциально зависит от напряжения

экспоненциально зависит от напряжения

![]() ,

то изменение

,

то изменение

![]() ,

необходимое для компенсации

,

необходимое для компенсации

![]() ,

будет сопровождаться

малым изменением напряжения

,

будет сопровождаться

малым изменением напряжения

![]() .Таким

образом, и

.Таким

образом, и

![]() будет небольшим.

будет небольшим.

Рис. 14

Поскольку ток нагрузки диодного стабилизатора Д-R (рис.14) является базовым током управляющего транзистора, то ток нагрузки транзисторного стабилизатора.

Рассматривая схему как линейную, можно показать, что

![]() .

(39)

.

(39)

Выходное сопротивление

![]() ,

(40)

,

(40)

где

![]() и

и

![]() - соответственно сопротивление эмиттера

и базы транзистора.

- соответственно сопротивление эмиттера

и базы транзистора.

Сопротивление

эмиттера транзистора существенно

зависит от эмиттерного тока, который,

в свою очередь, определяется ток-ом

нагрузки. С уменьшением эмиттерного

тока выходное сопротивление стабилизатора

увеличивается, что приводит к ухудшению

стабилизирующих свойств схемы..

Уменьшать

![]() можно, применяя более мощный транзистор

и увеличивая ток эмиттера. Заметим,

что последнее приводит к ухудшению

КПД схемы..

можно, применяя более мощный транзистор

и увеличивая ток эмиттера. Заметим,

что последнее приводит к ухудшению

КПД схемы..

2.4. Последовательные стабилизаторы напряжения

На рис. 15 показана схема стабилизатора последовательного типа (регулирующий транзистор включен последовательно с нагруз-кой), который представляет собой эмиттерный повторитель. Источником опорного напряжения в этой схеме является стаби-литрон Д.

Рис. 15

Выходное

напряжение стабилизатора

![]() .

.

Схема работает

следующим образом. При возрастании по

какой-либо причине выходного напряжения

(возрастает

![]() или увели-чится

или увели-чится

![]() ),

происходит уменьшение отпирающего

напряжения и

),

происходит уменьшение отпирающего

напряжения и

![]() транзистора (считаем, что падение

напряжения на стабилит-роне изменяется

мало), что уменьшает ток эмиттера, в

результате выходное напряжение

транзистора (считаем, что падение

напряжения на стабилит-роне изменяется

мало), что уменьшает ток эмиттера, в

результате выходное напряжение

![]() изменяется мало. Коэффициент стабилизации

схемы в линейном приближении равен

изменяется мало. Коэффициент стабилизации

схемы в линейном приближении равен

![]() .

(41)

.

(41)

Выходное сопротивление такой схемы определяется выражением (40).

Таким образом, у

этой схемы и

![]() и

и

![]() 6ыл с увеличе-нием тока эмиттера или,

что то же, с увеличением тока нагрузки

уменьшается.. Схема такого стабилизатора

на практике применяется чаще, чем

схема с параллельным включением

регулирующего транзистора, так как

она имеет больший КПД и позволяет

использовать менее мощный транзистор.

К недостаткам однокаскадных транзисторных

схем следует отнести сравнительно

высокое выходное сопротивление.

6ыл с увеличе-нием тока эмиттера или,

что то же, с увеличением тока нагрузки

уменьшается.. Схема такого стабилизатора

на практике применяется чаще, чем

схема с параллельным включением

регулирующего транзистора, так как

она имеет больший КПД и позволяет

использовать менее мощный транзистор.

К недостаткам однокаскадных транзисторных

схем следует отнести сравнительно

высокое выходное сопротивление.