Контрольные вопросы

1. Перечислите функциональные возможности, укажите назначение кнопок панели инструментов менеджера проектов, графического редактора, сигнального редактора системы MAX+PLUS.

2. Укажите назначение кнопок панели рисования графического редактора, сигнального редактора.

3. Как выполняется ввод и редактирование цепей, примитивов Input и Output, элементов схемы.

4. Каким образом создаются тестовые сигналы и файл временных диаграмм.

5. Из каких этапов состоит синтез комбинационных схем.

6. Опишите порядок выполнения проекта в системе MAX+PLUS II.

7. Сумматор. Функциональное назначение, область применения, назначение выводов, схема.

8. Полусумматор. Функциональное назначение, область применения, назначение выводов, схема.

9. Инкрементор. Функциональное назначение, область применения, назначение выводов, схема.

10. Какие функции выполняют команды «File/Open» и «Set Project To Current File»?

11. Создайте проект по заданию преподавателя.

12. По материалам работы составьте тестовую задачу, не похожую на задачи соседних бригад.

Работа 2. Описание комбинационных схем на языке Verilog

Специфика языков описания аппаратуры - HDL (Hardware Description Language) состоит в отображении процессов, протекающих в реальной электронной схеме параллельно и непрерывно. Рассмотрим основные средства языка Verilog, принадлежащие к подмножеству, поддерживаемому системой проектирования MaxPlus 2.

Алфавит языка — набор символов для построения конструкций языка, воспринимаемых компилятором — содержит: латинские буквы (регистр имеет значение !); цифры и специальные символы.

Идентификатор должен начинаться с буквы, или символа подчеркивания, может содержать цифры, знаки подчеркивания и доллара. Допускаются идентификаторы расширенного типа (escaped), они начинаются с символа «\» и заканчивающиеся пробелом. В качестве идентификатора нельзя использовать ключевые слова и обозначения элементов языка Verilog (см. Help).

Комментарий - строка, начинающаяся с двух символов косая черта «//». Фрагмент в скобках

/* */ - также комментарий, его используют при отладке для «закомментирования» - временного исключения фрагментов программы из компиляции.

Запись констант содержит: число (это количество разрядов), одинарную кавычку, основание системы счисления (буква b, o, d, h для 2-, 8-, 10-, 16-ричной систем счисления) и цифры в указанной системе. Число без указания разрядности и системы счисления принимается как десятичное. Отрицательные числа задаются знаком «минус» перед разрядностью числа в самом начале записи.

Сигналы в схеме бывают двух типов - цепи (wire) и регистры (reg), разрядность по умолчанию - 1 бит. Сигналы могут принимать одно из четырех значений: 0, 1, z, х. Значение «z» означает, что источник сигнала отключен, а «х» - что выход не определен, и может принимать любое значение 0 или 1.

Цепь wire моделирует провод, к которому непрерывно прилагается воздействие от источника сигнала, называемого драйвер (driver). Все сигналы описываемых устройств по умолчанию устанавливаются типа «wire». Все входные сигналы устройств должны иметь тип «wire».

Регистр reg способен хранить присвоенное значение, это элемент памяти, подобен переменной в программировании. Тип «reg» указывают для выходных сигналов схем с элементами памяти.

Вектор (шина) описывается указанием диапазона (Range). В квадратных скобках через двоеточие указывают индексы в убывающем порядке, первый индекс соответствует старшему разряду вектора. По умолчанию вектор - беззнаковое скалярное (scalared) целое, в котором по умолчанию разрешен доступ к отдельным битам. Для запрещения доступа к битам необходимо записать «vectored». Если перед указанием диапазона записать «signed», то будем иметь число в дополнительном коде со знаком.

Операторы в языке Verilog существуют двух типов: параллельные и последовательные. Разделитель всех операторов – точка с запятой. Символы пробела, табуляции, возврата каретки транслятор игнорирует, если они не нарушают целостность ключевых слов. Операторы бывают с одним, двумя и тремя операндами. В унарных операторах символ операции записывают слева от операнда, а в бинарных и в тернарном – между операндами.

Параллельные операторы используют для описания комбинационных схем без элементов памяти, Они выполняют непрерывное присваивание. Изменение выходного сигнала происходит при изменении любого из входных сигналов. Выходные сигналы имеют тип «wire».

Запись параллельного оператора начинаются с ключевого слова «assign» (назначить), затем записывается имя выходного сигнала, знак равенства, а затем непосредственно операторы, формирующие выходной сигнал (арифметические, логические, или условного назначения).

Операция Символ Арифметические

операторы Умножение Деление Сложение Вычитание Остаток

от деления * / + - % Операторы

сравнения Равно

? Не

равно ? Идентично

? Не

идентично ? == != === !== Операторы

отношения Больше

? Меньше

? Больше

или равно ? Меньше

или равно ? > < >= <= Поразрядные

операторы

и операторы свертки И И-НЕ ИЛИ ИЛИ-НЕ НЕ Искл.ИЛИ Искл.ИЛИ-НЕ & ~& | ~| ~ ^ ~^(^~) Логические

операторы И ИЛИ НЕ && || ~ Объединение {a,b,c}

Операторы отношения и сравнения сравнивают два операнда и выдают значение в виде однобитовой логической переменной, которая обычно используется в условных операторах и при поведенческом описании. При выполнении условия выдается «1». Если хотя бы один операнд не определен, то и результат примет неопределенное значение «х». В случае неодинаковой разрядности операндов, более короткий из них дополняется слева нулями.

Логические преобразования сигнала в языке Verilog выполняют три типа операторов с названиями: поразрядные, свертки, логические.

Поразрядные операторы – бинарные, содержат два операнда. Сигналы могут быть векторами, тогда логическая операция выполняется поразрядно. Векторы могут иметь различную разрядность, если разрядность одного операнда меньше, чем другого, то недостающие разряды заполняются нулями.

Операторы свертки, называют также операторами приведения. Это унарные операторы, использующие те же символы, что и поразрядные операторы (кроме оператора инверсии «~»). Они выполняются над единственным, многоразрядным операндом побитно, шаг за шагом, формируя на выходе одноразрядный результат. Этот тип операторов позволяет формировать признаки данных. Так, например, для многоразрядного вектора d, признак p1 = &d будет равен единице, если все биты вектора равны единице, признак p2 = |d будет равен нулю, если все биты вектора равны нулю, а p3 = ^d примет значение «1», если количество единиц в векторе d нечетно.

Третий тип называют именно «логические операторы» Это бинарные операторы И, ИЛИ, а также унарный оператор НЕ. Результат операции – однобитная переменная, равная нулю, если результат операции есть ноль. Эти операции используют для формирования условий в условных переходах.

Оператор объединения, позволяет из исходных векторов сформировать вектор суммарной разрядности. Исходные векторы записываются в фигурных скобках через запятую. Объединенный вектор будет иметь суммарную разрядность, он может быть записан справа и слева от знака равенства в операторе присваивания.

Оператор непрерывного условного присваивания имеет форму записи: «assign q = s ? a : b», читается так: if s is true then q = a , else q = b. В качестве условия «s» в данном операторе может использоваться выражение, формирующее одноразрядный логический сигнал «1» или «0», а вместо переменных «а» и «b» могут быть операторы, в том числе и условный оператор, заключенные в скобки.

|

assign |

Переменная |

= |

Условие |

? |

Ветвь ДА |

: |

Ветвь НЕТ |

; |

В списке чувствительности можно указать срабатывание по фронту, или спаду сигнала. Фронт сигнала обозначается «posedge», спад - «negedge», от слов «positive», «negative», и «edge» - край.

Блокирующее (blocking) последовательное присваивание обозначатся символом «=», запрещает исполнение других присваиваний до своего завершения. Неблокирующее процедурное присваивание (unblocking procedural) обозначается символами «=>» разрешает выполнение других присваиваний до своего выполнения, используется для описания регистровых структур с обратными связями.

Оператор условного перехода «if» относится к последовательным операторам, используется совместно с ключевым словом «always». Условие - переменная, или выражение, записывается в круглых скобках. При записи условия равенства в операции сравнения следует использовать два знака равенства «==». Ветвь ДА, выполняется, если условие истинно, и в результате его вычисления получено некоторое число (например, 1). Ветвь НЕТ, выполняется, если результат вычисления условия равен 0, или содержит значения x, z. Заметим, в записи оператора слово «then» отсутствует.

|

always |

if |

( |

Условие |

) |

Ветвь ДА |

; |

else |

Ветвь НЕТ |

; |

Переменная, которой присваивается значения, должна быть определена как регистр.

|

always |

case |

( |

Селектор |

) |

1 вариант селектора |

: |

Первое присваивание |

; |

|

|

2 вариант селектора |

: |

Второе присваивание |

; |

||||

|

default |

: |

Присваивание по умолчанию |

; |

|||||

|

endcase |

|

|||||||

Модуль описания на языке Verilog содержит элементы: заголовок, описание портов, описание устройства, завершение. Описание устройства может быть структурным, в виде набора модулей, или поведенческим.

Структурное описание выполняется по логическим уравнениям, полученным в результате синтеза комбинационной схемы. В уравнениях используются параллельные операторы, начинающиеся с ключевого слова «assign». Порядок операций задается применением круглых скобок.

Описание системы как набора модулей выполняется - по схеме, которая должна быть предварительно составлена из базовых логических элементов, принятых в языке Verilog: and, nand, or, nor, xor, xnor, buf, not (И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ, исключающее ИЛИ-НЕ, буферный элемент, отрицание НЕ). Строка описания каждого элемента содержит тип элемента, затем его обозначение на принципиальной схеме (не обязательно), затем в скобках через запятую имена всех выводов: вначале имя выхода, а затем – имена входов. Формат описания элементов имеет вид:

|

Тип |

Обозначение |

( |

Выход |

, |

Вход 1 |

, |

Вход 2 |

, |

вход N |

) |

; |

Проект

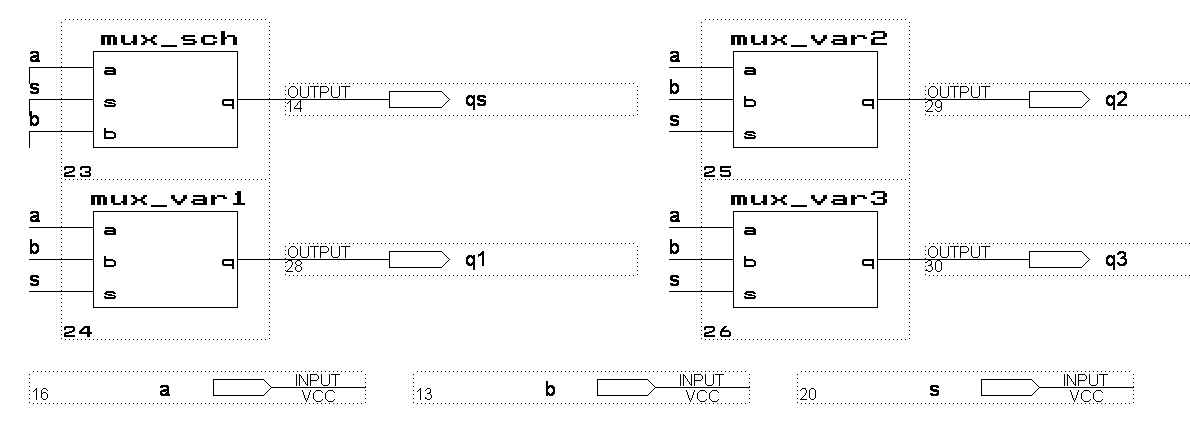

мультиплексора 2 в 1 (Рис.2.1).

Проект

мультиплексора 2 в 1 (Рис.2.1).

1) Проект мультиплексора в виде схемы. Схема (Рис.2.2) вводится в графическом редакторе, как описано в работе 1.

2) Описание мультиплексора по логическому уравнению (Пример 2.1). Первая строка описания - комментарий, признак начала комментария – две косые черты. Номера строк указаны как комментарий.

Заголовок описания - строка 2, содержит ключевое слово «module», затем имя модуля и список всех портов в круглых скобках. Конец данной, и всех последующих строк и операторов - точкой с запятой. Имя модуля должно совпадать с именем файла, расширение которого *.v.

Описание портов – строки 3,4. После ключевого слова «input», через запятую, перечисляются входные порты, а после слова «output» - все выходные порты. Перечисления заканчиваются точкой с запятой. Двунаправленные порты (если есть) перечисляются после слова «inout».

В примере типы сигналов не указаны, все

сигналы по умолчанию будут назначены

как однобитовые типа «wire».

Входы и двунаправленные сигналы всегда

должны иметь тип wire.

Выходы комбинационных схем обычно

принимают как тип wire.

Если сигналы должны иметь другие

параметры (тип и разрядность), то после

описания портов приводится дополнительное

описание типов сигналов.

примере типы сигналов не указаны, все

сигналы по умолчанию будут назначены

как однобитовые типа «wire».

Входы и двунаправленные сигналы всегда

должны иметь тип wire.

Выходы комбинационных схем обычно

принимают как тип wire.

Если сигналы должны иметь другие

параметры (тип и разрядность), то после

описания портов приводится дополнительное

описание типов сигналов.

Описание схемы - строка 5. Ключевое слово «assign» означает непрерывное назначение сигнала. Значение сигнала q заново вычисляется каждый раз, когда изменяется хотя бы один из сигналов (a,b,s). Для записи логических уравнений использованы поразрядные операторы И, ИЛИ, НЕ. Завершение описания – строка 6, ключевое слово «endmodule», после которого не должно быть никаких знаков препинания.

3) Описание мультиплексора как набора модулей (пример 2.2). Описание составлено по схеме (Рис. 1). Элементы схемы имеют обозначения dd1 – dd4, а внутренние узлы y1 – y3. Строки 1 - 4 повторяют пример 2.1. В строке 5 описаны внутренние сигналы схемы типа «wire», которые потребовалось ввести, чтобы впоследствии описать функции всех логических элементов. Строка 6 описывает инвертор, обозначенный на схеме как «dd1», его выходной сигнал «у1», а входной - «s». В строках 7-9 описаны остальные элементы схемы.

4) Поведенческое описание мультиплексора – это алгоритм функционирования (Пример 2.3), описывается оператором непрерывного условного присваивания (Строка 5).

//Пример

2.1.

1 module

mux_var1 (a, b, s, q); //2 input

a, b, s; //3 output

q; //4 assign

q = a & s | b & ~s;

//5 endmodule //6

//Пример

2.2

1 module

mux_var2 (a, b, s, q); //2 input

a, b, s; //3 output

q; //4

wire

y1, y2, y3; //5 not

dd1 (y1, s); //6 and

dd2 (y2, a, s);

//7 and

dd3 (y3, b, y1); //8 or

dd4 (q, y2, y3); //9 endmodule //10

//Пример

2.3.

1 module

mux_var3 (a, b, s, q); //2 input

a, b, s; //3 output

q; //4 assign

q=s?a:b; //5 endmodule //6

1) Создайте проект мультиплексора, в котором ввод проекта (как в работе 1) выполнен в виде схемы (Рис.2.2), файл которой имеет имя «mux_sch.gdf». После компиляции создайте символ.

2) Создайте проект для структурного описания мультиплексора по логическому уравнению. Для этого командой «File/New» создайте новый текстовый файл, а командой «Save As» запишите его с именем «mux_var1» и расширением «.v». Расширение файла определяет вызов транслятора с языка Verilog. Проект, описанный на языке Verilog, компилируется подобно проекту в виде схемы. Введите описание, приведенное в примере 2.1, укажите данный файл как ведущий командой «File/Project/Set Project To Current File». Выполните компиляцию, выбирая из пункта меню «Processing» временное моделирование «Timing SNF Extractor». Создайте символ командой «File/Create Default Symbol».

3) Создайте проект и символ с именем «mux_var2», используя пример 2.2.

4) Создайте проект и символ с именем «mux_var3», используя пример 2.3.

Рис.2.3.

Схема иерархического проекта

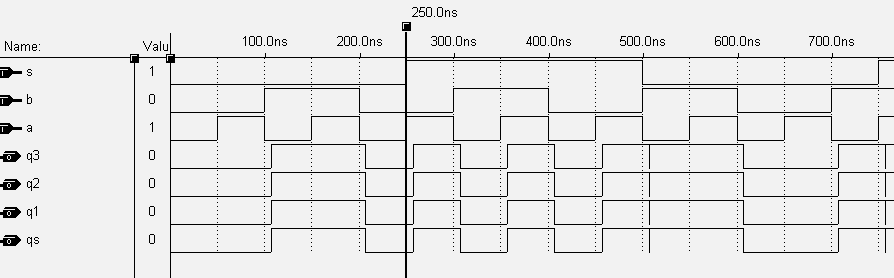

6) Для моделирования разработанной схемы запустите сигнальный редактор командой «MAX+plus II / Waveform Editor» (Рис. 2.4), сохраните открывшийся файл с именем проекта командой «Save As».

7) Для выбора контрольных точек установите курсор в столбец «Name» и сделайте щелчок правой кнопкой. В открывшемся меню выберите «Enter Nodes from SNF», а в окне нажмите кнопку «List»,кнопку «=>», и кнопку «OK». В результате все терминалы схем будут выбраны в качестве контрольных точек, для которых будут изображены временные диаграммы.

8) Создайте входные тестовые сигналы, для которых несложно предсказать выходные сигналы и однозначно определить правильность функционирования устройства. Для мультиплексора следует подать на входы «a» и «b» различные сигналы, а на адресный вход «s» - переключающий сигнал, частота коммутации которого ниже, чем у сигналов «a» и «b».

Рис.

2.4. Результат моделирования

мультиплексоров

Выберите сигнал «b», нажмите кнопку 12-Clock, установите множитель «Multiplied By» равным 2, нажмите «ОК». На вход «b» будут поданы импульсы, период повторения которых в 2 раза больше, чем период сигнала «Clock».

Для сигнала «s» можно выбрать множитель 4, или более, например 5.

8) Запустите имитатор командой «MAX+plus II / Simulator», или кнопкой на панели инструментов. Время моделирования в программе «Waveform Editor» устанавливается из меню «File/End Time» и составляет по умолчанию 1 мкс.

А нализ

результатов. Моделирование подтвердило

правильность функционирования всех

моделей мультиплексора: при s=1

имеем q = а, а при s=0

выход q = b.

Анализ временных задержек сигналов для

различных моделей выполнен при

увеличенном масштабе по временной оси

(кнопка 4 на рис. 1.6) позволяет сравнить

модели по быстродействию. Начало

измеряемого интервала отмечается

перемещаемым маркером, а конец - указателем

мыши..

нализ

результатов. Моделирование подтвердило

правильность функционирования всех

моделей мультиплексора: при s=1

имеем q = а, а при s=0

выход q = b.

Анализ временных задержек сигналов для

различных моделей выполнен при

увеличенном масштабе по временной оси

(кнопка 4 на рис. 1.6) позволяет сравнить

модели по быстродействию. Начало

измеряемого интервала отмечается

перемещаемым маркером, а конец - указателем

мыши..

Задание 2.2. Мультиплексор для коммутации шин. Создайте проект мультиплексора для коммутации сигналов, передаваемых по 4-разрядным шинам (Рис. 2.5) в виде поведенческого описания на основе примера 2.3. Сигналы «a,b,q» необходимо описать как шины:

input [3:0] a, b;

input s;

output [3:0] q;

Р азработайте

тестовые сигналы, оцените результаты

моделирования. Выполните синтез схемы

мультиплексора для шин.

азработайте

тестовые сигналы, оцените результаты

моделирования. Выполните синтез схемы

мультиплексора для шин.

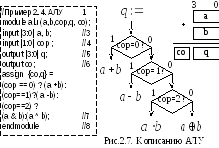

Задание 2.3. АЛУ комбинационного типа. Создайте описание АЛУ для заданных операций (Таблица 2.1), разработайте тестовые сигналы, приведите анализ результатов моделирования. АЛУ имеет 4-разрядные входы (a,b) и выход (q); двухразрядный код операции (cop); выход переноса (co - Carry Out) (Рис. 2. 6).

Рассмотрим пример. Заданы коды операций: 0 – суммирование, 1 – вычитание, 2 – поразрядная логическая операция «исключающее ИЛИ», 3 – поразрядная логическая операция «И».

В описании АЛУ (Пример 2.4) строка 2 – заголовок- имя описания и перечисление всех входов и выходов. В строке 3 описаны 4-разряднее входные векторы a,b, в строке 4 - 2-разрядный вектор кода операции (cop), а в строке 5 – выходной вектор (q) В строке 6 указан сигнал переноса (c_o), описание диапазона отсутствует, значит, этот сигнал – одноразрядный. Также отсутствует описание типов сигналов, следовательно, все сигналы по умолчанию имеют тип «wire», с которыми можно использовать только оператор непрерывного назначения с ключевым словом «assign», а также арифметические, логические операторы и оператор условного присваивания.

Таблица

2.1 Бригада 1 2 3 4 5 6 7 8 9 10 11 12 00 add add add add add add add add add add add

add 01 nand xor or and xor nand and or xor and or nand 10 sub or xor or and or or nor nxor nxor xor xor 11 xor nor nand nor or xor nor xor or or and or Флаги co,z co,n co,p co,z co,n co,p co,z co,n co,p co,z co,n co,p

В

В

assign {p,c_o} = (cop < 2) ? (cop==0 ? (a +b):( a -b)): (cop==2 ? (a & b):(a ^ b));

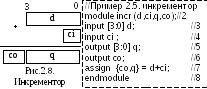

З адание

2. 4. Инкрементор. Создайте иерархический

проект инкрементора для сравнения

варианта, введенного в виде схемы в

примере 1.4, содержащей в каждом разряде

полусумматор, и в виде описания (Пример

2.5).

адание

2. 4. Инкрементор. Создайте иерархический

проект инкрементора для сравнения

варианта, введенного в виде схемы в

примере 1.4, содержащей в каждом разряде

полусумматор, и в виде описания (Пример

2.5).

В операторе объединения, исходные векторы записываются в фигурных скобках через запятую. Объединенный вектор может быть записан справа и слева от знака равенства в операторе присваивания. Поведение схемы описывает всего одна строка 7, структура данных показана на рис. 2.8.

Задание 2.5. Составьте орисание 4-разрядного сумматора ,используя исходные данные задания 1.5. После успешной компиляции создайте символ. Создайте иерархический проект сумматора, используя символ, созданный в задании 1.5.

Здание 2.6. Составьте иерархический проект формирователя признаков данных, используя данные задания 1.6.