- •Методичні вказівки

- •6.050102 "Комп’ютерна інженерія"

- •Лабораторна робота №1

- •Тема: Визначення конфігурації персонального комп’ютера (пк) засобами post і стандартними засобами операційної системи Windows

- •Теоретичні відомості

- •Хід роботи

- •Контрольні питання:

- •Лабораторна робота №2

- •Тема: Визначення конфігурації персонального комп’ютера (пк) за допомогою програми Еверест та SisoftSandra, та виконання порівняльного аналізу.

- •Теоретична частина

- •Хід роботи

- •Контрольні питання:

- •Лабораторна робота №3

- •Тема: Визначення конфігурації та ефективності процесора за допомогою SisoftSandra.

- •Теоретична частина

- •Хід роботи

- •Контрольні питання:

- •Лабораторна робота №4

- •Тема: Визначення продуктивності пам’яті персонального комп’ютера (пк) за допомогою програми Еверест та виконання порівняльного аналізу з теоретичними значеннями.

- •Теоретичні відомості

- •Контрольні питання:

- •Лабораторна робота №5

- •Тема: Тестування відеокарти пк засобами програми gpuz.

- •Теоретичні відомості

- •Завдання до роботи:

- •Контрольні питання

- •Лабораторна робота №6

- •Тема: Визначення технічних характеристики обчислювальної системи у пакеті SiSoftSandra.

- •Теоретичні відомості

- •Хід роботи

- •Контрольні питання:

- •Лабораторна робота №7

- •Тема: Розрахунок потужності блоку живлення

- •Теоретичні відомості

- •Хід роботи:

- •Контрольні питання:

-

Лабораторна робота №2

-

Тема: Визначення конфігурації персонального комп’ютера (пк) за допомогою програми Еверест та SisoftSandra, та виконання порівняльного аналізу.

-

Мета: Визначити якомога краще конфігурацію ПК використовуючи спеціальні програмні засоби.

Теоретична частина

SisoftSandra надає нам інформацію про систему, діагностику і тестування.

SiSoftware Sandra - це системний аналізатор для 32-х і 64-бітових версій Windows, що включає в себе тестові і інформаційний модулі. Завдяки цій програмі ми можемо отримати відомості про процесор, чипсет, відеоадаптер, порта, принтера, звукової карти, пам'яті, мережі і т.д.

EVEREST- це теж діагностика обладнання і тестування практично будь-яких компонентів пам’яті для користувачів ПК. Ця програма пропонує найбільш точної інформації та можливості діагностики, включаючи он-лайнові функції, пам’ять критеріїв, апаратний моніторинг, і низького рівня апаратних інформації.

Архітектура центрального процесора

Центральний процесор (Central processing unit) — функціональна частина ЕОМ, що призначена для інтерпретації команд. Функції — обробка даних по заданій програмі шляхом виконання арифметичних і логічних операцій; програмне керування роботою пристроїв комп’ютера.

З погляду програмістів, під архітектурою процесора мається на увазі його здатність виконувати певний набір машинних кодів. Більшість сучасних десктопних процесорів відносяться до сімейства x86, або Intel-сумісних процесорів архітектури IA32 (архітектура 32-бітових процесорів Intel). Її основа була закладена компанією Intel в процесорі i80386, проте в подальших поколіннях процесорів вона була доповнена і розширена як самою Intel (введені нові набори команд MMX, SSE, SSE2 і SSE3), так і сторонніми виробниками (набори команд EMMX, 3Dnow! І Extended 3Dnow!, розроблені компанією AMD).

Проте розробники комп'ютерного устаткування вкладають в поняття «Архітектура процесора» (іноді, щоб остаточно не заплутатися, використовується термін «мікроархітектура») дещо інший смисл. Із їхньої точки зору, архітектура процесора відображає основні принципи внутрішньої організації конкретних сімейств процесорів. Наприклад, архітектура процесорів Intel Pentium позначалася як Р5, процесорів Pentium II і Pentium III — Р6, а популярні в недавньому минулому Pentium 4 відносилися до архітектури NetBurst.

Ядро

«Процесорний ядро» (як правило, для стислості його називають просто «ядро») – це конкретне втілення [мікро] архітектури (тобто «архітектури в апаратному сенсі цього слова»), що є стандартом для цілої серії процесорів. Наприклад, NetBurst – це мікроархітектура, яка лежить в основі багатьох сьогоднішніх процесорів Intel: Celeron, Pentium 4, Xeon.

«Таким чином, можна сказати що« ядро »- це конкретне втілення певної мікроархітектури« в кремнії », що володіє (на відміну від самої мікроархітектури) певним набором строго обумовлених характеристик. Мікроархітектура – аморфна, вона описує загальні принципи побудови процесора. Ядро – конкретно, це мікроархітектура, «обросла» всілякими параметрами і характеристиками.

Кеш

У всіх сучасних процесорах є кеш (по-англійськи – cache). Кеш – це якась особлива різновид пам'яті (основна особливість, що відрізняє кардинально кеш від ОЗУ – швидкість роботи), яка є свого роду «буфером» між контролером пам'яті і процесором. Служить цей буфер для збільшення швидкості роботи з ОЗУ.

Специфіка конструювання сучасних процесорних ядер призвела до того, що систему хешування в переважній більшості CPU доводиться робити багаторівневою. Кеш першого рівня (самий «близький» до ядра) традиційно поділяється на дві (як правило, рівні) половини: кеш інструкцій (L1I) і кеш даних (L1D). Це розділення передбачається так званої «гарвардської архітектурою» процесора, яка станом на сьогодні є найпопулярнішою теоретичної розробкою для побудови сучасних CPU. У L1I, відповідно, акумулюються тільки команди (з ним працює декодер, див. Нижче), а в L1D – тільки дані (вони згодом, як правило, потрапляють у внутрішні регістри процесора).

Декодер

Саме для того, щоб процесор «зовні виглядав» як x86 CPU, і існує такий блок як декодер: він відповідає за перетворення «зовнішнього» x86-коду у «внутрішні» команди, що виконуються ядром (при цьому досить часто одна команда x86-коду перетворюється в кілька більш простих «внутрішніх»). Декодер є дуже важливою частиною сучасного процесора: від його швидкодії залежить те, наскільки постійним буде потік команд, що надходять на виконуючі блоки.

Виконуючі (функціональні) пристрою

У найпершому наближенні вони традиційно діляться на дві великі групи: арифметико-логічні пристрої (ALU) і блок обчислень з плаваючою крапкою (FPU).

1. арифметико-логічні пристрої

ALU традиційно відповідають за два типи операцій: арифметичні дії (додавання, віднімання, множення, ділення) з цілими числами, логічні операції із знову-таки цілими числами (логічне «і», логічне «або», «що виключає або», і тому подібні ).

2. блок обчислень з плаваючою комою *

FPU займається виконанням команд, що працюють з числами з плаваючою комою, крім того, традиційно на нього «вішають усіх собак» у вигляді всіляких додаткових наборів команд (MMX, 3Dnow!, SSE, SSE2, SSE3 …) – незалежно від того, працюють вони з числами з плаваючою комою, або з цілими.

Регістри процесора

Регістри – по суті, ті ж комірки пам’яті, але «територіально» вони розташовані прямо в процесорному ядрі. Регістри — це внутрішня пам’ять процесора. Являють собою ряд спеціалізованих додаткових комірок пам’яті, а також внутрішні носії інформації мікропроцесора. Регістр є пристроєм тимчасового збереження даних, числа або команди і використовується з метою полегшення арифметичних, логічних і пересильних операцій. Основним елементом регістра є електронна схема, називана тригером, що здатна зберігати одну двійкову цифру (розряд).

Шина — це канал пересилання даних, який використовується спільно різними блоками системи. Шина може являти собою набір провідних ліній у друкованій платі, проводу, припаяні до виводів роз'ємів, у які вставляються друковані плати, або плоский кабель. Інформація передається по шині у виді груп бітів. До складу шини для кожного біта слова може бути передбачена окрема лінія (паралельна шина), або всі біти слова можуть послідовно в часі використовувати одну лінію (послідовна шина).

-

Шина даних. Служить для пересилання даних між процесором і пам'яттю або процесором і пристроями введення-виведення. Ці дані можуть являти собою як команди мікропроцесора, так і інформацію, що він посилає в порти введення-виведення або приймає звідти.

-

Шина адрес. Використовується ЦП для вибору необхідної комірки пам'яті або пристрою введення-виведення шляхом установки на шині конкретної адреси, що відповідає одній з комірок пам'яті або одному з елементів введення-виведення, що входять у систему.

-

Шина керування. По ній передаються керуючі сигнали, призначені пам'яті і пристроям введення-виведення. Ці сигнали вказують напрямок передачі даних (у процесор або з нього).

Структура базового мікропроцесора

У персональних ЕОМ знайшли застосування не тільки мікропроцесори фірми Intel. Найбільшими виробниками аналогів мікропроцесорах Intel (клонів) є фірми Cyrix і AMD.

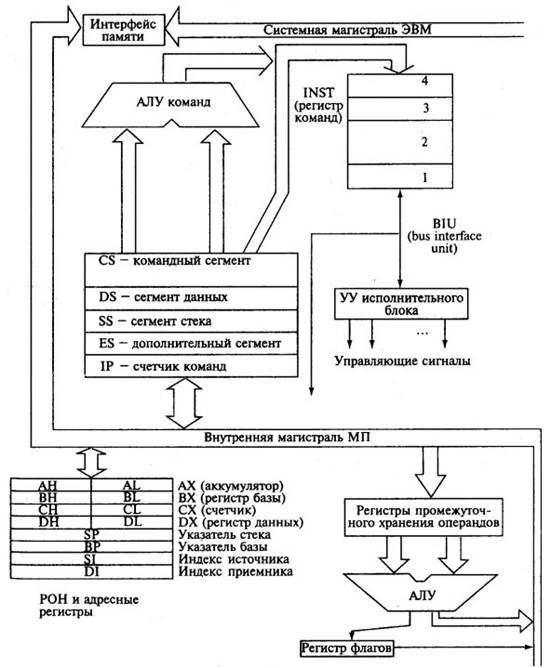

Структурна схема базової моделі МП фірми Intel наведена на малюнку 1.

Рис. 2.1. Структурна схема базової моделі мікропроцесора Intel

Умовно мікропроцесор можна розділити на дві частини: виконавчий блок (Execution Unit – EU) і пристрій сполучення з системною магістраллю (Bus Interface Unit – ВШ).

У виконавчому блоці знаходяться: арифметичний блок і регістри загального призначення (РОН). Арифметичний блок включає арифметико-логічний пристрій, допоміжні регістри для зберігання операндів і регістр прапорів.

Вісім регістрів виконавчого блоку МП (АХ, ВХ, СХ, DX, SP, ВР, SI, DI), що мають довжину, рівну машинному слову, діляться на дві групи. Першу групу складають регістри загального призначення: АХ, ВХ, СХ і DX, кожен з яких представляє собою реєстрову пару, складену з двох регістрів завдовжки в 0.5 машинного слова: аккумулятор, або регістр АХ складається з регістрів АН та AL. Регістр бази (Base Register) ВХ складається з регістрів ВН і BL. Лічильник (Count Register) СГ включає регістри СН і CL. Регістр даних (Data Register) DX містить регістри DH і DL. Кожен з коротких регістрів може використовуватися самостійно або у складі регістровий пари. Умовні назви (аккумулятор, регістр бази, лічильник, реєстр даних) не обмежують застосування цих регістрів – ці назви говорять про найбільш частому використанні їх або про особливості використання того або іншого регістра в тій йди іншої команді.

Другу групу складають адресні регістри SP, BP, SI і DI (в старших моделях кількість адресних регістрів збільшено). Ці регістри активно використовуються за функціональним призначенням і в інших цілях їх застосовувати не рекомендується. Як адресного регістра часто використовується РОН ВХ. Програмно допускається використання регістрів BP, DI і SI в якості регістрів для зберігання операндів, але окремі байти в цих регістрах недоступні. Основне їх призначення – зберігати числові значення, що реалізуються при формуванні адрес операндів.

Пристрій сполучення з системною магістраллю містить керуючі регістри, конвеєр команд, АЛУ команд, пристрій управління виконавчим блоком МП і інтерфейс пам'яті (що з'єднує внутрішню магістраль МП з системною магістраллю ПЕОМ).

Керуючі регістри BIU: CS (покажчик командного сегмента), DS покажчик сегмента даних), SS (покажчик сегмента стека), ES (покажчик додаткового сегмента) та ін. служать для визначення фізичних адрес ВП – операндів і команд.

Регістр IP (Instruction Pointer) є покажчиком адреси команди, яка буде вибиратися в конвеєр команд як чергову команди (у вітчизняній літературі такий пристрій називається лічильник команд). Конвеєр команд МП зберігає декілька команд, що дозволяє при виконанні лінійних програм поєднати підготовку чергової команди з виконанням поточної.

До керуючим регістрів МП відноситься і регістр прапорів, кожен розряд якого має строго певне призначення. Зазвичай розряди регістра прапорів встановлюються апаратно при виконанні чергової операції залежно від отримуваного в АЛУ результату. При цьому фіксуються такі властивості одержуваного результату, як нульовий результат, від'ємне число, переповнення розрядної сітки АЛУ і т.д. Але деякі розряди регістра прапорів можуть встановлюватися за спеціальними командам. Деякі розряди мають чисто службове призначення (наприклад, зберігають розряд, «що випав» з АЛУ під час зсуву) або є резервними (тобто не використовуються).

Усі прапори молодшого байта регістра встановлюються арифметичними або логічними операціями МП. Усі прапори старших байтів, за винятком прапора переповнення, встановлюються програмним шляхом, для цього в МП є команди установки прапорів (STC, STD, STI), скидання (CLC CLD, CLI), інвертування (CMC).