- •1. Системы счисления

- •Десятичная система счисления

- •Двоичная система счисления

- •Восьмеричная и шестнадцатеричная системы счисления

- •Перевод чисел из любой системы счисления в десятичную

- •Перевод чисел из десятичной системы счисления в любую другую

- •2. Алгебра логики

- •2.1. Логические операции

- •Инверсия

- •Конъюнкция

- •Дизъюнкция

- •Эквиваленция (равнозначность)

- •Импликация

- •Антиконъюнкция

- •Антидизъюнкция

- •2.2. Нормальные формы

- •Конъюнктивная нормальная форма

- •Дизъюнктивная нормальная форма

- •3. Классические основы построения ЭВМ

- •3.1. Машина Тьюринга

- •Основные положения машины Тьюринга

- •3.2. Автомат Неймана

- •3.3 Архитектура классической ЭВМ

- •4. Применение средств алгебры логики для описания функционирования устройств компьютера

- •Логические схемы

- •Построение логических схем

- •5. Введение в алгоритмизацию

- •6. Знакомство со средой Турбо Паскаль

- •6.1. Общие сведения

- •6.2. Запуск Турбо-Паскаля на выполнение

- •6.3. Назначение функциональных клавиш системы Турбо-Паскаль

- •6.4. Работа с текстовым редактором Турбо-Паскаля

- •Клавиши перемещения курсора

- •Работа с блоками текста

- •7. Основы алгоритмизации

- •7.1. Алгоритм

- •7.2. Алгоритмические структуры

- •8. Программирование на языке Pascal

- •8.1. Алфавит языка

- •8.2. Арифметические выражения и правила их записи

- •Знаки операций

- •Операции div и mod

- •8.3. Типы данных

- •Целые типы

- •Логический тип

- •Символьный тип

- •Строковый тип

- •Вещественный тип

- •8.4. Стандартные функции

- •8.5. Структура программы на языке Паскаль

- •8.6. Описательная часть программы

- •8.7. Исполнительная часть программы

- •8.8. Оператор присваивания

- •8.9. Операторы ввода-вывода

- •Оператор ввода

- •Оператор вывода

- •8.10. Комментарии в программе

- •9. Ветвления

- •9.1. Операторы условия и перехода

- •Логический оператор

- •Операции отношения

- •Логические операции

- •9.2. Оператор выбора

- •10. Циклические вычислительные процессы

- •10.1. Оператор цикла с параметром

- •10.2. Оператор цикла с постусловием

- •10.3. Оператор цикла с предусловием

- •10.4. Вложенные циклы

- •10.5. Оператор прерывания цикла

- •11. Операции с индексированными переменными

- •11.1. Массивы одномерные

- •11.2. Описание массивов

- •Ввод элементов массива

- •Вывод элементов массива

- •11.3. Обработка одномерных массивов

- •12. Двумерные массивы

- •12.1. Матрицы

- •12.2. Описание двумерного массива

- •Ввод элементов двумерного массива

- •Вывод элементов двумерного массива

- •12.3. Обработка двумерных массивов

- •13. Подпрограммы

- •13.1. Функции и процедуры

- •Структура программы, содержащей процедуру (функцию)

- •13.2. Процедуры

- •13.3. Вложенные процедуры

- •Директива forward

- •13.4. Функции

- •14. Обработка строк текста

- •14.1. Символьные переменные

- •Фрагмент таблицы ASCII-кодов букв латинского алфавита

- •Фрагмент таблицы ASCII-кодов букв русского алфавита

- •14.2. Функции обработки символьных переменных

- •14.3. Строковые переменные

- •14.4. Функции обработки строковых переменных

- •14.5. Процедуры обработки строковых переменных

- •14.6. Примеры обработки строковых переменных

- •15. Структурированные типы данных

- •15.1. Записи

4. Применение средств алгебры логики для описания функционирования устройств компьютера

Для описания того, как функционируют аппаратные средства компьютера очень удобен

математический аппарат алгебры логики, поскольку основной системой счисления в

компьютере является двоичная, в которой используются цифры «1» и «0».

Следовательно, одни и те же устройства компьютера могут применяться для обработки и хранения как числовой информации, представленной в двоичной системе счисления, так и логических переменных; на этапе конструирования аппаратных средств алгебра логики позволяет значительно упростить логические функции, описывающие функционирование схем компьютера, и, следовательно, уменьшить число элементарных логических элементов, из десятков тысяч которых состоят основные узлы компьютера.

Данные и команды в памяти компьютера и в регистрах процессора представляются в виде

двоичных последовательностей различной структуры и длины.

Существуют различные физические способы кодирования двоичной информации, но чаще всего единица кодируется более высоким уровнем напряжения, чем ноль.

В логической схеме компьютера выделяют логические элементы. Логический элемент компьютера – это часть электронной логической схемы, которая реализует элементарную логическую формулу.

Логическими элементами компьютеров являются электронные схемы «И», «ИЛИ», «НЕ», «И-НЕ», «ИЛИ-НЕ» и другие (называемые также вентилями), а также триггер. С помощью этих схем можно реализовать любую логическую формулу, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния – «1» и «0» в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению истина (1), а низкий – значению ложь (0).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую формулу, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности – это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значением истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

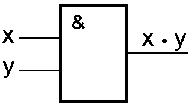

Схема «И» реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных схемах схемы «И» с двумя входами представлено на рис. 5.

Рис. 5. схема «И»

На выходе схемы «И» значение «1» будет тогда и только тогда, когда на всех входах будут «1». Когда хотя бы на одном входе будет «0», на выходе также будет «0».

Операция конъюнкции на функциональных схемах обозначается знаком «&» (читается как «амперсэнд»), являющимся сокращенной записью английского слова and.

22

Схема «ИЛИ» реализует дизъюнкцию двух или более логических значений. Условное обозначение схемы «ИЛИ» представлено на рис. 6.

Рис. 6. Схема «ИЛИ»

Значение дизъюнкции равно «1», если сумма значений операндов больше или равна «1». Когда хотя бы на одном входе схемы «ИЛИ» будет «1», на её выходе также будет «1».

Операция дизъюнкции на функциональных схемах обозначается знаком «1».

Схема «НЕ» (инвертор) реализует операцию отрицания. Условное обозначение схемы НЕ представлено на рис. 7.

Рис. 7. Схема «НЕ»

Если на входе схемы – «0», то на выходе будет «1». Когда на входе – «1», на выходе будет

«0».

Схема «И-НЕ» состоит из элемента «И» и инвертора и осуществляет отрицание результата схемы «И». Условное обозначение схемы «И-НЕ» представлено на рисунке 8. Таблица истинности схемы «И-НЕ» – это таблица 5.

Рис. 8. Схема «И-НЕ» Таблица истинности схемы «И-НЕ»

Таблица 5

|

|

|

|

|

х |

у |

|

х у |

|

|

|

|

|

|

0 |

0 |

|

1 |

|

|

|

|

|

|

0 |

1 |

|

1 |

|

|

|

|

|

|

1 |

0 |

|

1 |

|

|

|

|

|

|

1 |

1 |

|

0 |

|

|

|

|

|

|

Схема «ИЛИ-НЕ» состоит из элемента «ИЛИ» и инвертора и осуществляет отрицание результата схемы «ИЛИ». Условное обозначение схемы «ИЛИ-НЕ» представлено на рис. 9, а таблица истинности схемы ИЛИ-НЕ – это табл. 6.

23

Рис. 9. Схема «ИЛИ-НЕ» Таблица истинности схемы «ИЛИ-НЕ»

Таблица 6

|

|

|

|

|

х |

у |

|

х у |

|

|

|

|

|

|

0 |

0 |

|

1 |

|

|

|

|

|

|

0 |

1 |

|

0 |

|

|

|

|

|

|

1 |

0 |

|

0 |

|

|

|

|

|

|

1 |

1 |

|

0 |

|

|

|

|

|

|

Триггер – это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое – двоичному нулю.

Термин триггер происходит от английского слова trigger – защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает «хлопанье». Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить из одного электрического состояния в другое и наоборот.

Самый распространённый тип триггера – RS-триггер (S и R, соответственно, от английских set – установка, и reset – сброс). Условное обозначение триггера – на рис. 10.

Рис. 10. RS-триггер

Он имеет два симметричных входа S и R и два симметричных выхода Q и Q , причем

выходной сигнал Q является логическим отрицанием сигнала Q .

На каждый из двух входов S и R могут подаваться входные сигналы в виде

кратковременных импульсов ( ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие – нулем.

На рис. 11 показана реализация триггера с помощью вентилей ИЛИ-НЕ и соответствующая таблица истинности представлена в таблице 7.

24

Рис. 11. Схема ИЛИ-НЕ Таблица истинности реализации триггера ИЛИ-НЕ

Таблица 7

S |

R |

Q |

|

|

|

|

Q |

|

|||||

|

|

|

|

|

|

|

0 |

0 |

|

запрещено |

|

||

|

|

|

|

|

||

0 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

хранение бита |

|

||

|

|

|

|

|

|

|

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ:

1.Если на входы триггера подать S = 1, R = 0, то (независимо от состояния) на выходе Q верхнего вентиля появится «0». После этого на входах нижнего вентиля окажется R = 0, Q = 0 и выход станет равным «1».

2.Точно так же при подаче «0» на вход S и «1» на вход R на выходе появится «0», а на Q – «1».

3.Если на входы R и S – логическая «1», то состояние Q и Q не меняется.

4.Подача на оба входа R и S логического «0» может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 • 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Сумматор – это электронная логическая схема, выполняющая суммирование двоичных чисел. Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

При поразрядном сложении десятичных чисел (например, 157, 68 и 9) складывают сначала цифры разрядов единиц всех слагаемых (7 + 8 + 9); результат, если это однозначное число, записывают в разряд единиц итоговой суммы, если же результат — двузначное число (как в данном примере, 7 + 8 + 9 = 24), то в итог записывают только единицы (4), а десятки (2) переносят (добавляют) в разряд десятков слагаемых (5 + 6 + 2). Затем операция сложения повторяется, но уже над десятками, после этого – над сотнями и т.д., до получения итоговой суммы (234). При поразрядном сложении чисел, представленных в двоичном коде, также складываются цифры слагаемых в данном разряде и к полученному результату прибавляется единица переноса (если она имеется) из младшего разряда. В результате формируются (по правилам сложения в двоичной системе счисления) значения суммы в данном разряде и переноса в старший разряд.

25

Многоразрядный сумматор для поразрядного сложения обычно состоит из соответствующим образом соединённых одноразрядных суммирующих устройств. Простейшее из них, часто называют полусумматором (ПС), в случае сложения двоичных чисел может быть собрано, например, из 4 логических элементов: «И» (2 элемента типа совпадений схемы), «ИЛИ» (вентиль электрический), «НЕ» (инвертор). Схема ПС может видоизменяться в зависимости от используемой системы логических элементов. ПС производит суммирование двух с образованием цифр суммы S и переноса с (таблица 8). Однако для реализации многоразрядных сумматоров необходимо иметь суммирующее устройство на 3 входа (для суммирования трёх чисел – слагаемых xi и yi и переноса Ci-1 из младшего разряда), на выходах которого образуется сумма Si и перенос Ci+1 в старший разряд. Работа такого сумматора отражена в таблице 9.

Таблица истинности сложения чисел х и у

Таблица 8

x |

y |

S |

c |

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

1 |

0 |

1 |

0 |

|

|

|

|

0 |

1 |

1 |

0 |

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

Таблица истинности сложения чисел хi и уi

Таблица 9

xi |

yi |

ci-1 |

Si |

ci+1 |

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

Кроме основной операции – суммирования, большинство сумматоров используются для операций умножения и деления, а также для логических операций (логическое умножение и сложение и др.).

26