Филиппов-21.106

.pdf

жительное напряжение (+Uип) подается на вывод 14, отрицательное (–U ип) – на

вывод 7. На вход CLK (клемма 8) |

подаются синхронизирующие тактовые |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

импульсы. Сдвиг в сторону вы- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ходов со старшими |

номерами |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

осуществляется по |

переднему |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

фронту тактового сигнала CLK. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Входы A и B (клеммы 1 и 2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

называются последовательными |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

информационными, внутри мик- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

а |

б |

росхемы они подключены к ло- |

||||||||||||||

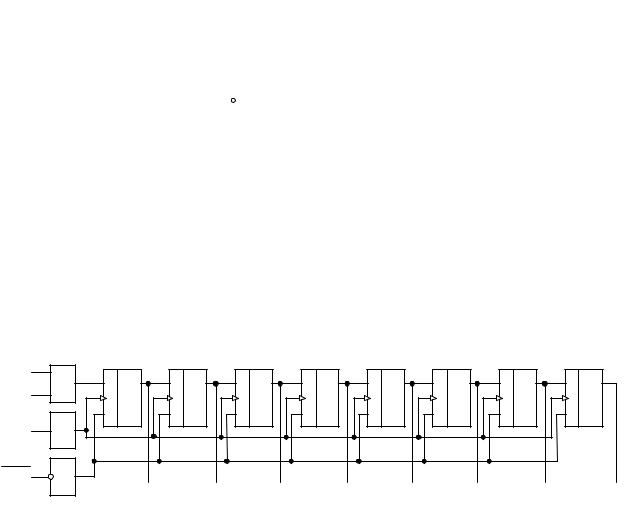

Рис. 3. Цоколевка (а) и условное обозначение (б) |

гическому элементу И, а с его |

|||||||||||||||||

|

|

микросхемы КР1564ИР8 |

|

|

|

|

выхода сигнал подается на вход |

|||||||||||

D первого триггера (рис. 4). При подаче на вход CLR (клемма 9) лог. 0 (потенциала низкого уровня) происходит сброс регистра, т. е. на его выходах устанавливается потенциал низкого уровня [4].

Рис. 4. Схема регистра КР1564ИР8

1.2.Порядок выполнения работы

1)Вставьте микросхему КР1564ИР8 в гнездо и подключите клемму 14 к источнику напряжения Е4 (5 В), а клемму 7 – к общей точке.

2)Соедините клеммы с помощью проводов. На вход 8 сигнал подавайте с генератора низкой частоты, выставив на нем множитель «1» и частоту 100 Гц. Осциллограф подключите к выходам Q0 (клемма 3) и Q1 (клемма 4). К выходам Q2 и Q3 подключите вольтметры V1 и V2 соответственно.

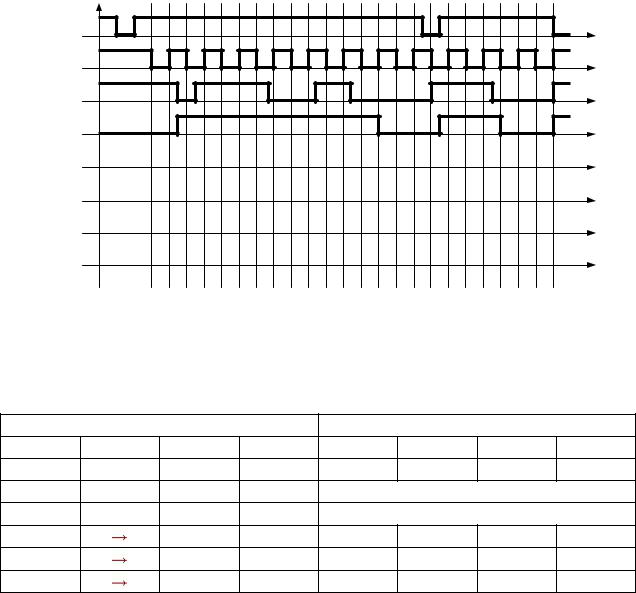

3)Подавая импульсы на входы А и В, исследуйте работу регистра, постройте временную диаграмму (рис. 5) и сравните ее с таблицей истинности

(табл. 1).

10

4)Смоделируйте исследуемую схему (зарубежным аналогом микросхемы КР1564ИР8 является 74HC164N) с помощью программы Multisim [5] или Proteus и проанализируйте ее работу.

5)Сделайте выводы по результатам исследований.

Рис. 5. Временная диаграмма работы регистра КР1564ИР8

|

|

|

|

|

|

|

|

Таблица 1 |

|

|

|

Таблица истинности регистра сдвига |

|

|

|||

|

|

Входы |

|

|

Выходы |

|

||

CLR |

CLK |

A |

B |

Q0 |

Q1 |

Q2 |

Q3 |

|

0 |

|

X |

X |

X |

0 |

0 |

0 |

0 |

1 |

|

0 |

X |

X |

|

Не меняются |

|

|

1 |

|

1 |

X |

X |

|

Не меняются |

|

|

1 |

0 |

1 |

1 |

1 |

1 |

Q0 |

Q1 |

Q2 |

1 |

0 |

1 |

0 |

X |

0 |

Q0 |

Q1 |

Q2 |

1 |

0 |

1 |

X |

0 |

0 |

Q0 |

Q1 |

Q2 |

Символом X в табл. 1 сокого или низкого уровня, нала.

обозначена подача на входы A и B потенциалов выне играющих роли в формировании выходного сиг-

1.3.Контрольные вопросы

1)Для чего предназначены регистры?

2)На каких типах триггеров может быть построен регистр?

11

3)Каково основное отличие параллельного регистра от последовательного?

4)За счет чего обеспечивается сдвиг информации в последовательном регистре?

Лабораторная работа 2

АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

Ц е л ь р а б о т ы: практическое ознакомление с арифметико-логическими устройствами; изучение функциональных возможностей и принципа работы микросхем арифметико-логических устройств.

2.1. Краткие теоретические сведения

Арифметико-логическое устройство (АЛУ) – функциональная часть микропроцессора, предназначенная для выполнения операций преобразования (обработки) величин: арифметических, логических (поразрядных), сдвига. АЛУ является одним из основных устройств микропроцессора, оно выполняет одну из первых функций микропроцессора – вычисление.

На уровне логических схем АЛУ состоит из логических элементов, сумматоров, триггеров и некоторых других элементов.

Арифметико-логическое устройство функционально можно разделить на две части:

микропрограммное устройство (устройство управления), задающее последовательность микрокоманд;

операционное устройство, в котором реализуется заданная последовательность микрокоманд.

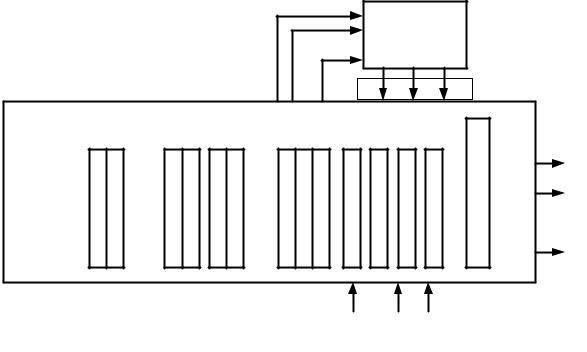

Структурная схема АЛУ и его связь с другими блоками машины показаны на рис. 6. В состав АЛУ входят регистры Рг1 – Рг7, в которых обрабатывается информация, поступающая из оперативной или пассивной памяти N1, N2, ..., NS; логические схемы, реализующие обработку информации по микрокомандам, поступающим из устройства управления [3].

Закон переработки информации задает микропрограмма М, которая записывается в виде последовательности микрокоманд A1,A2, ..., Аn-1,An. При этом различают два вида микрокоманд: внешние, т. е. такие микрокоманды, которые

12

поступают в АЛУ от внешних источников и вызывают в нем те или иные преобразования информации (на рис. 6 – микрокоманды A1,A2,..., Аn), и внутренние, которые генерируются в АЛУ и воздействуют на микропрограммное устройство, изменяя естественный порядок следования микрокоманд (на рис. 6 эти микрокоманды обозначены P1, P2, ..., Pm).

Рис. 6. Структурная схема арифметико-логического устройства

Результаты вычислений из АЛУ по кодовым шинам записи Y1, Y2, ...,Yn передаются в оперативное запоминающее устройство (ОЗУ).

Функции регистров, входящих в АЛУ:

Рг1 – сумматор (или сумматоры) – основной регистр АЛУ, в котором образуется результат вычислений;

Рг2, Рг3 – регистры слагаемых, сомножителей, делимого или делителя (в зависимости от выполняемой операции);

Рг4, Рг5 – адресные регистры, предназначены для запоминания (иногда и формирования) адреса операндов и результата;

Рг6 – k индексных регистров, содержимое которых используется для формирования адресов;

Рг7 – l вспомогательных регистров, которые могут быть аккумуляторами, индексными регистрами или могут использоваться для запоминания промежуточных результатов.

13

Часть операционных регистров является программно-доступной, т. е. они могут быть адресованы в команде для выполнения операций с их содержимым. К ним относятся сумматор, индексные регистры и некоторые вспомогательные регистры. Остальные регистры нельзя адресовать в программе, т. е. они являются программно-недоступными.

В микропроцессорах, применяемых в устройствах электроснабжения, до-

вольно часто АЛУ представлено микросхемой К155ИП3 (рис. 7). |

|

|

|

||||||||||||||

АЛУ К155ИП3 имеет |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

входы |

чисел А1 – |

А4 и |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

В1 – |

В4, входы управления |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

V0 – V3, М, вход переноса P0, |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

выходы результата F1 – F4, |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

выход переноса P4, выход ра- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

венства кодов К, выходы R и |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

G для схемы быстрого пере- |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

носа. Вход М определяет вид |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

выполняемых операций (при |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

подаче на М сигнала лог. 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

(потенциала высокого |

уров- |

|

|

а |

б |

||||||||||||

ня) на А и В выполняется од- |

Рис. 7. Цоколевка (а) и условное |

||||||||||||||||

на из 16 логических |

опера- |

обозначение (б) микросхемы К155ИП3 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

ций, при подаче лог. 0 выполняются арифметические операции). Комбинационная схема АЛУ может выполнять следующие операции:

сложение байтов с переносом или без него; логические операции И, ИЛИ и исключающее ИЛИ; инкремент, декремент, инверсию, циклический сдвиг влево, вправо через (или минуя) флаг переноса, обмен тетрад в байте; десятичную коррекцию содержимого аккумулятора. Работа АЛУ поясняется таблицей функционирования (табл. 2).

Наращивание разрядности АЛУ делается так же, как и в сумматорах, т. е. выход переноса P4 АЛУ младших разрядов подключается ко входу переноса P0 АЛУ старших разрядов. Однако при большом числе разрядов время выполнения операций увеличивается из-за большого числа переносов из разряда в разряд. Для ускорения этого процесса используются специальные микросхемы, которые называются схемами ускоренного переноса [4].

14

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2 |

||||||||||

|

|

|

Таблица функционирования АЛУ К155ИП3 |

|||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Функции |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

V3 |

V2 |

V1 |

|

V0 |

логические |

|

|

|

|

|

арифметические (М = 0) |

|||||||||||||||||||||||||||||||||||||||

|

|

|

P0 = 1 |

|

|

|

|

P0 = 0 |

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

(М = 1) |

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

переноса нет |

|

перенос есть |

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

A + 1 |

|||||||||||||||||||

|

|

|

|

|

A |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A Ú B |

|

(A B) + 1 |

|||||||||||||||||||||||||||

A B |

||||||||||||||||||||||||||||||||||||||||||||||||||

0 |

0 |

1 |

|

0 |

|

|

|

|

Ù B |

|

A Ú |

|

|

|

|

|

|

|

(A Ú |

|

) + 1 |

|||||||||||||||||||||||||||||

|

|

A |

B |

|

|

|

|

|

|

B |

||||||||||||||||||||||||||||||||||||||||

0 |

0 |

1 |

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

–1 |

|

0 |

|

|

|

|

|

|

|

||||||||||||||||||||||

0 |

1 |

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A + (A Ù |

|

) |

|

|

|

A + (A Ù |

|

|

) + 1 |

|||||||||||||||||||||

|

|

A Ù B |

|

|

|

|

B |

B |

||||||||||||||||||||||||||||||||||||||||||

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(A Ú B) + (A Ù |

|

) |

|

(A Ú B) + (A Ù |

|

) + 1 |

||||||||||||||||||||||||

|

|

|

|

|

B |

|

|

|

|

|

|

B |

B |

|||||||||||||||||||||||||||||||||||||

0 |

1 |

1 |

|

0 |

A Å B |

A – B – 1 |

|

|

A – B |

|||||||||||||||||||||||||||||||||||||||||

0 |

1 |

1 |

|

1 |

|

A Ù |

|

|

|

|

|

|

(A Ù |

|

|

) – 1 |

|

|

|

(A Ù |

|

|

) |

|||||||||||||||||||||||||||

B |

|

B |

B |

|||||||||||||||||||||||||||||||||||||||||||||||

1 |

0 |

0 |

|

0 |

|

|

|

Ú B |

A + (A B) |

|

A + (A B) + 1 |

|||||||||||||||||||||||||||||||||||||||

|

|

A |

||||||||||||||||||||||||||||||||||||||||||||||||

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A + B |

|

|

A + B + 1 |

|||||||||||||||||||||||||||

A Å B |

||||||||||||||||||||||||||||||||||||||||||||||||||

1 |

0 |

1 |

|

0 |

|

|

|

|

|

B |

(A Ú |

|

|

) + (A Ù B) |

|

(A Ú |

|

) + (A Ù B) + 1 |

||||||||||||||||||||||||||||||||

|

|

|

|

|

B |

B |

||||||||||||||||||||||||||||||||||||||||||||

1 |

0 |

1 |

|

1 |

|

A Ù B |

(A B) – 1 |

|

|

|

(A B) |

|||||||||||||||||||||||||||||||||||||||

1 |

1 |

0 |

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

A + A |

|

|

A + A + 1 |

|||||||||||||||||||||||||||||||

1 |

1 |

0 |

|

1 |

|

A Ú |

|

|

|

|

|

(A B) + A |

|

(A B) + A + 1 |

||||||||||||||||||||||||||||||||||||

|

B |

|||||||||||||||||||||||||||||||||||||||||||||||||

1 |

1 |

1 |

|

0 |

|

A Ú B |

(A Ú |

|

|

) + A |

|

(A Ú |

|

|

) + A + 1 |

|||||||||||||||||||||||||||||||||||

|

B |

B |

||||||||||||||||||||||||||||||||||||||||||||||||

1 |

1 |

1 |

|

1 |

|

|

|

|

|

A |

|

|

A – 1 |

|

|

|

|

|

|

A |

||||||||||||||||||||||||||||||

2.2. Порядок выполнения работы

Исследования необходимо выполнить для двух режимов. Первый режим.

1)Вставьте микросхему К155ИП3 в гнездо и подключите ее к источнику напряжения Е4. Клемму 12 подсоедините к общей точке. На вход P0 (клемма 7) подайте лог. 1.

2)На вход M (клемма 8) подайте лог. 1.

3)К соответствующим номеру рабочего места (номер указан на стенде) выходам (клеммы 9 – 11, 13) подключите вольтметры или осциллограф.

4)Подавая на входы управления (V0 – V3) напряжение лог. 1 и лог. 0 в соответствии с данными табл. 2, а на соответствующие номеру рабочего места

15

входы A1 – A4 и В1 – В4 напряжение лог. 1 и лог. 0 в следующем порядке: 0-0, 0-1, 1-0, 1-1, проанализируйте сигналы на выходах F1 – F4.

5) Для каждой проверенной функции составьте таблицу истинности.

Второй режим.

1)Подайте напряжение, соответствующее лог. 0, на клемму 8.

2)Подавая на входы управления (V0 – V3) напряжение лог. 1 и лог. 0 в соответствии с данными табл. 2, а на соответствующие номеру рабочего места входы A1 – A4 и В1 – В4 напряжение лог. 1 и лог. 0 в следующем порядке: 0-0, 0-1, 1-0, 1-1, проанализируйте сигналы на выходах F1 – F4.

3)Проанализируйте работу микросхемы в первом и во втором режимах. Смоделируйте исследуемую схему (зарубежный аналог – SN74181N) с

помощью программы Multisim [5] или Proteus и проанализируйте ее работу. Сделайте выводы по результатам исследований.

2.3.Контрольные вопросы

1)Каково назначение АЛУ?

2)Какие операции может выполнять АЛУ? При каких условиях?

3)Каково назначение входов P0 и P4?

4)На входы А1, В2, V3 схемы на рис. 7, a поданы потенциалы лог. 1, а на входы B3, A4, V0, V1, V2 – лог. 0. Какие потенциалы будут на выходах F1 – F4?

Лабораторная работа 3

ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Ц е л ь р а б о т ы: практическое ознакомление с постоянными запоминающими устройствами; изучение функциональных возможностей и принципа работы микросхем постоянных запоминающих устройств.

3.1. Краткие теоретические сведения

Часто в системах микропроцессорного управления устройствами электроснабжения требуется хранение информации, которая не изменяется в процессе

16

эксплуатации устройства или изменяется редко. Это такая информация, как программы в микроконтроллерах, начальные загрузчики в компьютерах, таблицы коэффициентов цифровых фильтров в сигнальных процессорах. Эта информация практически не требуется одновременно, поэтому простейшие устройства для запоминания постоянной информации (ПЗУ) можно построить на мультиплексорах. Эти запоминающие устройства в составе системы работают только в режиме чтения. В литературе постоянные запоминающие устройства иногда называются ROM (Read Only Memory – память, доступная только для чтения).

ПЗУ обладает способностью сохранять информацию при сбоях и отключении питания (энергонезависимость).

Микросхемы ПЗУ имеют матричную структуру и словарную организацию, поэтому информация считывается в форме многоразрядного кода.

По способу занесения информации микросхемы ПЗУ делятся на MROM (Mask Read Only Memory) – постоянные запоминающие устройства (масочные); PROM (Programmable ROM) – программируемые постоянные запоминающие устройства; EPROM (Erasable PROM) – перепрограммируемые постоянные запоминающие устройства с ультрафиолетовым стиранием информации; EEPROM (Electrically Erasable PROM) – перепрограммируемые постоянные за-

поминающие устройства с электронным стиранием информации.

Разрядность микросхемы памяти определяется количеством битов ячейки памяти или количеством разрядов шины данных. Адресное пространство (число ячеек – максимальное возможное число слов хранимых микросхемой) определяется как 2n , где n – разрядность шины адреса.

Информационная емкость равна произведению разрядности микросхемы на количество ячеек микросхемы памяти, определяется в битах или в байтах. Организация запоминающего устройства определяется произведением разрядности микросхемы на количество ячеек микросхемы памяти, выражается парой чисел и обозначается как N × m, где N – число ячеек микросхемы памяти, а m – разрядность микросхемы [3].

В микроконтроллерах, применяемых в устройствах электроснабжения, одним из используемых ПЗУ служит микросхема К555РЕ4 (рис. 8), которая может работать в двух режимах: хранения (невыборки) и считывания. Для счи-

17

тывания информации на выходах D0 – D7 необходимо подать код адреса и раз-

решающие сигналы управления на входы А0 – А10 и CS1 – CS3. |

|

|

|

|

|

|

||||||||||||

|

Микросхема |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

К555РЕ4 имеет не- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

сколько прямых и ин- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

версных входов управ- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

ления |

CS, |

связанных |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

определенным логичес- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ким оператором. По- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

этому необходимо по- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

давать на управляющие |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

входы |

определенную |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

комбинацию |

сигналов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

1-1-0, |

чтобы сформи- |

а |

б |

|

||||||||||||||

ровать |

условие разре- |

Рис. 8. Цоколевка (а) и условное |

|

|||||||||||||||

шения считывания. |

обозначение (б) микросхемы К555РЕ4 |

|

3.2.Порядок выполнения работы

1)Вставьте микросхему К555РЕ4 в гнездо и подключите клемму 24 к источнику напряжения Е4. Клемму 12 подсоедините к общей точке.

2)На входы CS1 – CS3 подайте комбинацию сигналов 1-1-0.

3)На адресных входах А0 – А10 установите адресацию на ячейку, заданную преподавателем.

4)По очереди подключая клеммы 9 – 11 и 13 – 17 к вольтметрам или осциллографу, проанализируйте сигналы на выходах D0 – D7.

5)Постройте временную диаграмму.

6)Смоделируйте исследуемую схему (зарубежный аналог – 6275-1) с помощью программы Multisim [5] или Proteus и проанализируйте ее работу.

7)Сделайте выводы по результатам исследований.

3.3.Контрольные вопросы

1)Каково основное функциональное назначение микросхем ПЗУ?

2)Какую роль выполняют выводы микросхем ПЗУ?

18

3) Как определить организацию, информационную емкость и разрядность микросхем ПЗУ?

Лабораторная работа 4

ОПЕРАТИВНЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

Ц е л ь р а б о т ы: практическое ознакомление с оперативными запоминающими устройствами; изучение функциональных возможностей и принципа работы микросхем оперативных запоминающих устройств.

4.1. Краткие теоретические сведения

Оперативные запоминающие устройства (ОЗУ) являются неотъемлемой частью микропроцессорных систем различного назначения, они осуществляют запись, хранение и считывание информации и работают только при включенном питании, т. е. ОЗУ являются энергозависимыми.

ОЗУ по виду хранения информации разделяются на статические и динамические. В статическом ОЗУ в качестве элемента памяти используется триггер, в динамическом – конденсатор. Длительность хранения информации в статических ОЗУ не ограничена, тогда как в динамических она связана с временем саморазряда конденсатора, а значит, требуются специальные средства регенерации и дополнительные затраты времени на этот процесс.

Конструктивно любое ОЗУ состоит из двух блоков – матрицы запоминающих элементов и дешифратора адреса. По технологическим соображениям матрица чаще всего имеет двухкоординатную дешифрацию адреса – по строкам и столбцам. На рис. 9 показана структура 16-битного статического ОЗУ. Матрица состоит из 16 элементов памяти (ЭП).

Каждая ячейка памяти адресуется по входам А и В путем выбора дешифраторами адресных линий по строкам А0...Аk и по столбцам B0...Bm и подачи по выбранным линиям сигнала лог. 1. При этом в выбранном элементе памяти срабатывает двухвходовый элемент И, подготавливая цепи чтения-записи информации на входных или выходных разрядных шинах. Разрешающим для вы-

19