- •FEATURES

- •APPLICATIONS

- •DESCRIPTION

- •ABSOLUTE MAXIMUM RATINGS

- •ELECTRICAL CHARACTERISTICS: +VA = +5V

- •DEVICE INFORMATION

- •TIMING INFORMATION

- •TIMING CHARACTERISTICS

- •TYPICAL CHARACTERISTICS

- •THEORY OF OPERATION

- •REFERENCE

- •ANALOG INPUT

- •DIGITAL INTERFACE

- •TIMING AND CONTROL

- •READING DATA

- •BYTE

- •NOISE

- •AVERAGING

- •LAYOUT

- •REVISION HISTORY

ADS8322

www.ti.com |

SBAS215A –JULY 2001–REVISED JANUARY 2010 |

THEORY OF OPERATION

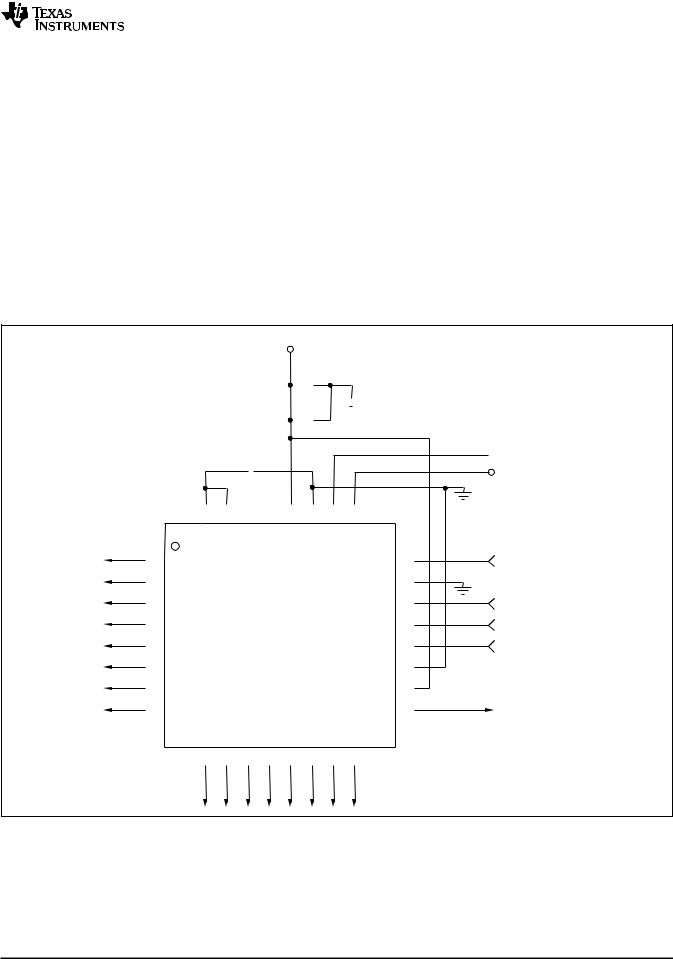

The ADS8322 is a high-speed successive approximation register (SAR) A/D converter with an internal 2.5V bandgap reference. The architecture is based on capacitive redistribution, which inherently includes a sample-and-hold function. The basic operating circuit for the ADS8322 is shown in Figure 13.

The ADS8322 requires an external clock to run the conversion process. The clock can be run continuously or it can be gated to conserve power between conversions. This clock can vary between 25kHz (1.25kHz throughput) and 10MHz (500kHz throughput). The duty cycle of the clock is unimportant as long as the minimum HIGH and LOW

times are at least 40ns and the clock period is at least 100ns. The minimum clock frequency is governed by the parasitic leakage of the capacitive digital-to-analog (CDAC) capacitors internal to the ADS8322.

The analog input is provided to two input pins, +IN and –IN. When a conversion is initiated, the differential input on these pins is sampled on the internal capacitor array. While a conversion is in progress, both inputs are disconnected from any internal function.

+5V Analog Supply

|

|

|

|

|

|

|

|

|

|

|

10µF |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.1µF |

|

|

0.1µF |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

31 |

|

30 |

|

29 |

28 |

27 |

26 |

25 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

REF |

REF |

|

NC |

NC |

+V |

|

AGND |

+IN |

|

−IN |

|

|||||||||

|

|

OUT |

IN |

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

DB15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

DB14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BYTE |

23 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

DB13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RD |

22 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

DB12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CONVST |

21 |

||||||

|

|

|

|

|

|

|

|

ADS8322 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

5 |

DB11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK |

20 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DGND |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

6 |

DB10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VD |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

7 |

DB9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

DB8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUSY |

17 |

||

|

|

DB7 |

DB6 |

|

DB5 |

DB4 |

DB3 |

|

DB2 |

DB1 |

DB0 |

|

||||||||||

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

10 |

|

11 |

|

12 |

13 |

14 |

15 |

16 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+

+

Analog Input

−

Chip Select

Read Input

Conversion Start

Clock Input

Busy Output

Figure 13. Typical Circuit Configuration

Copyright © 2001–2010, Texas Instruments Incorporated |

Submit Documentation Feedback |

9 |

Product Folder Link(s): ADS8322