лекции ВТиИТ / 02_Память

.pdf

Память в вычислительных системах

Классификация типов памяти:

1.По типу доступа

Адресная

Ассоциативная

Последовательная:

FIFO(первый зашел, первый вышел)

LIFO (последний зашел, первый вышел)

циклические

2.По возможности изменения данных

RAM(оперативно запоминающее устройство - ОЗУ)

Статическое

Динамическое

ROM(постоянно запоминающее устройство - ПЗУ)

Масочные (ROM)(M)

С возможностью программирования (EPROM)

С возможностью перепрограммирования (EEPROM)

Flash

3.По энергозависимости

Энергозависимые

Энергонезависимые

Основные параметры памяти

1. |

Информационная емкость памяти (равна числу ячеек памяти) |

|||||||||||

2. |

Структура – определяет, сколько ячеек памяти может считать одновременно |

|||||||||||

|

|

4 kb = 4096*1 = 1024*4 = 512*8 и т.д. |

||||||||||

3. |

Быстродействие |

|||||||||||

|

|

|

|

Установка адреса |

||||||||

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

cs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R/W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

DO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

D |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tвыб |

|

|

|

|

||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

tвыб = tвыд - время выборки/выдачи информации на шину данных. |

||||||||||||

4. |

Потребляемая мощность |

|||||||||||

|

n |

|

|

|

||||||||

A |

|

|

|

|

||||||||

|

|

|

|

|

||||||||

|

m |

|

|

|

|

|||||||

|

|

|

|

|||||||||

|

|

|

DI |

|

|

|||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

DO |

|

|

||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

R/W |

|

|

|||||||

|

|

|

|

|

|

|

||||||

|

|

|

cs |

|

|

|||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

А – адресная шина.

DI – шина входных данных DO – шина выходных данных

R/W - определяет режим работы чтение/запись. CS – вход «выбор микросхемы».

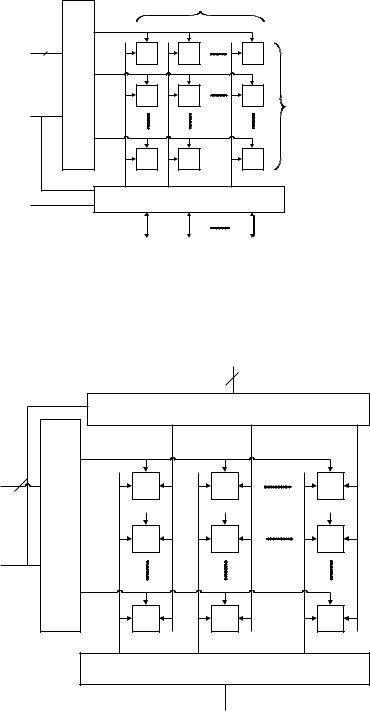

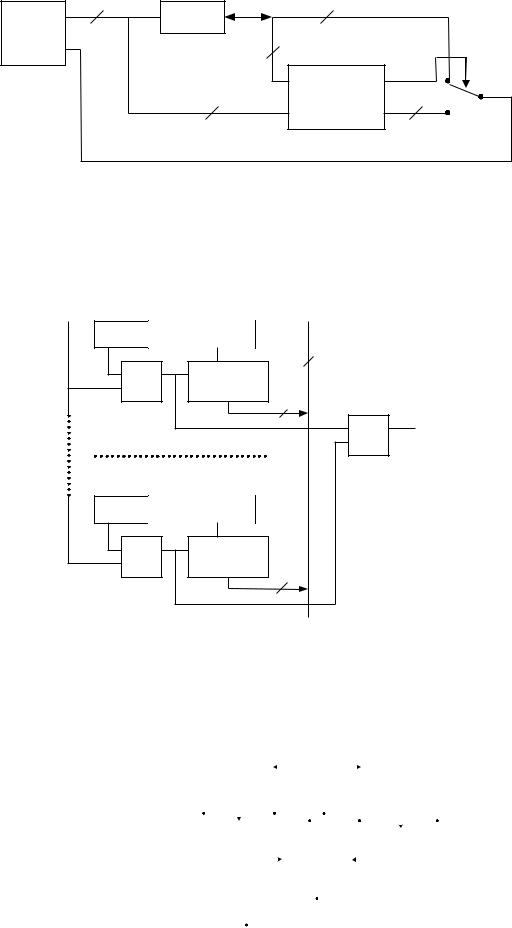

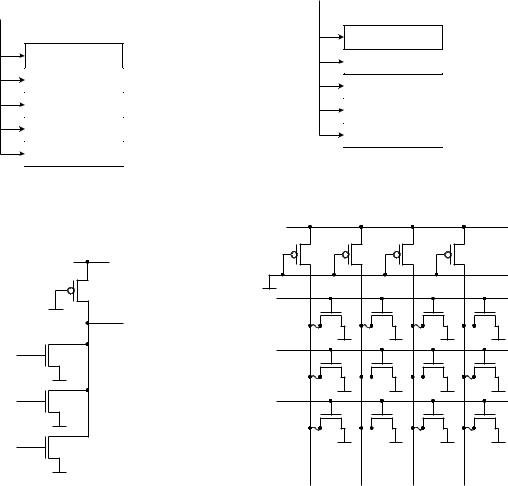

Структуры запоминающих устройств Адресные структуры

(2D):

|

m |

|

|

DC |

|

|

|

n |

|

|

|

ЗЭ |

ЗЭ |

ЗЭ |

|

ЗЭ |

ЗЭ |

ЗЭ |

n |

cs |

|

2 |

|

ЗЭ |

ЗЭ |

ЗЭ |

|

|

Усилитель R/W |

|

|

R/W |

|

|

|

DI/O |

DI/O |

DI/O |

Матрица запоминающих элементов (ЗЭ) M=k*m, М – информационная емкость в битах, k – число хранимых слов, m – их разрядность.

Дешифратор DC активизирует одну из выходных линий -> считываем или записываем данные (слово) разрядностью m из ЗЭ. Возможно применение только для малой емкости.

3D:

n/2 |

A1 |

cs |

|

A2 |

n/2 |

|

DCy |

|

DCx |

|

|

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

ЗЭ |

|

1 |

|

1 bit

Только чтение. 1 бит данных за 1 цикл. Выбирается 1 ЗЭ на пересечении активных выходов. Адреса делятся как 2n/2*2n/2=2n

3D реализация m-разрядного слова:

|

|

|

|

|

|

|

|

DCy |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

2n/2 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

n/2 |

|

|

|

|

|

|

|

M |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DCx |

|

|

|

|

|

|

|

M |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

|

|

A n/2 |

|

|

2n/2 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

m

Модифицированная структура 2DM:

|

|

|

|

|

DCx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

n-1 |

...A |

k |

|

2n-k |

|

|

|

|

|

2n-k x m2k |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

1 |

2 |

|

|

|

m |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ak-1...Ao |

|

k |

|

|

|

|

2k |

|

|

|

|

2k |

|

|

|

|

2k |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Mux |

|

|

|

Mux |

|

|

|

Mux |

|

||||

|

|

cs |

|

|

|

|

|

2k - >1 |

|

|

2k - >1 |

|

|

2k - >1 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E0 |

|

|

|

E0 |

|

|

|

E0 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

Dm - 1 |

|

Dm - 2 |

|

Do |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Дешифратор выбирает из матрицы 2n-k x m2k целую сроку, состоящую из m слов, каждое разрядностью 2k. Вторая часть разрядов адреса используется для выбора нужных разрядов из строки m2k . Из каждого 2k выбирается 1 бит (на MUX 2k -> 1). На выходах управляемых буферов ЕО получается m-разрядное слово.

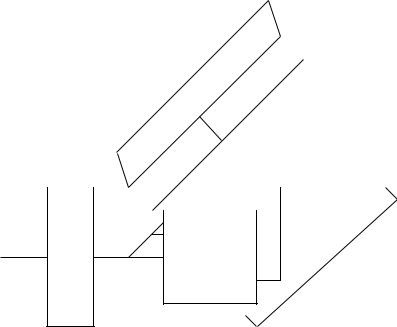

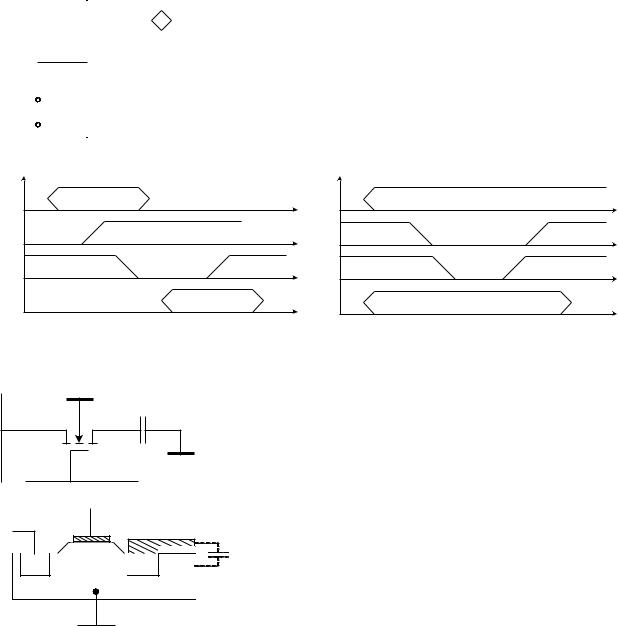

Память с последовательным доступом:

На примере FIFO

|

WR |

RD |

|

|

|

|

|

|

|

|

|

S |

T |

|

|

|

|

|

R |

|

|

|

СчWR |

СчRD |

|

|

|

|

|

|

|

|

n |

|

|

|

|

|

|

|

= = |

|

|

|

n |

|

n |

|

|

|

n |

|

|

|

|

DI |

WR |

Awr |

Ard |

RD |

DO |

|

|

m |

|

|

|

m |

|

&

&

Буфер

пуст

Буфер

полный

СчWR(СчRD) – счетчик записи(считывания)

Перед началом работы счетчики сбрасываются, при работе происходит чередование циклов запись/считывание, т. е. счетчик чтения догоняет счетчик записи, если адреса сравняются при чтении, то буфер пуст, а если при записи, то буфер полон. Файловый регистр имеет независимые входы адреса чтения и независимые входы адреса записи. Файловый регистр позволяет выполнять операции записи и чтения данных независимо друг от друга.

Схема файлового регистра |

|

|

|

|

||

DI |

4 |

DI |

RG DO |

4 |

|

DI MUXDO 4 DO |

|

|

|

|

|||

|

|

& |

|

|

|

|

|

|

E DD1 |

|

|

|

|

|

4 |

DI |

RG DO |

4 |

ARD |

S1 |

|

|

|

|

|

S2 DD5 |

|

|

|

& |

|

|

|

|

|

|

E DD2 |

|

|

|

|

|

4 |

DI |

RG DO 4 |

|

|

|

|

|

& |

|

|

|

|

|

|

E DD3 |

|

|

|

|

|

4 |

DI |

RG DO 4 |

|

|

|

|

|

& |

|

|

|

|

|

|

E DD4 |

|

|

|

|

AWR |

|

|

|

|

|

|

Запись и чтение выполняются 4-х разрядными словами. Данные хранятся в регистрах DD1DD4. Считывание данных из регистров выполняется через мультиплексор (DD5).

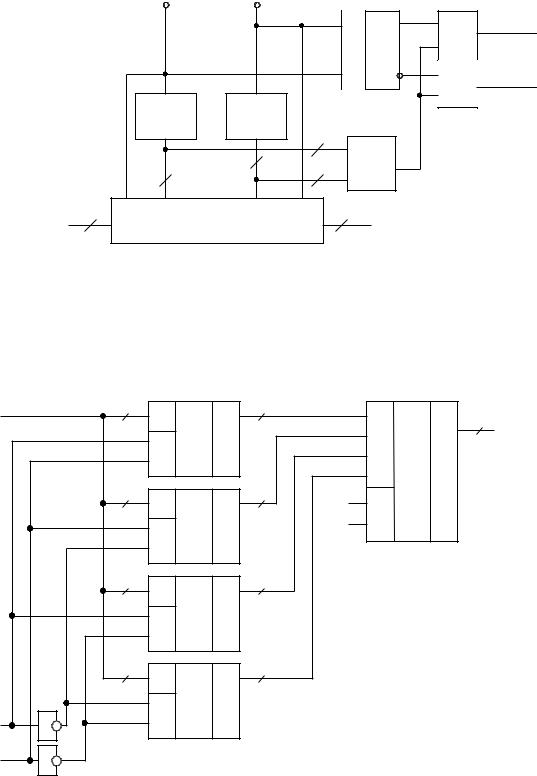

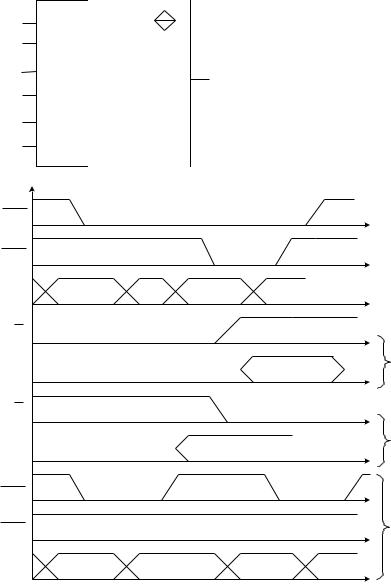

КЭШ (Cache) – память (сокращенное время обмена данных). |

|

Ставится между процессором и оперативной памятью. |

|

A |

D |

|

RAM |

CPU |

|

|

D |

|

Hi |

|

Cach |

Dat |

A |

|

Tag |

|

D |

КЭШ обладает малой емкостью и высоким быстродействием. При чтении данных сначала обращаются в КЭШ, для поиска данных используется Tag – это отличительный признак информации (обычно физический адрес RAM), если информация есть в КЭШ, то вырабатывается сигнал Hit и данные считываются из КЭШ, если информации там нет, то она считывается из RAM с одновременной записью в КЭШ

Полностью ассоциативная КЭШ память:

Tag |

Tag |

Data |

Data |

|

address |

||||

|

|

|

||

|

|

|

D |

|

|

= = |

BUF |

|

|

|

|

|

Hit |

|

|

|

|

1 |

|

|

Tag |

Data |

|

|

|

= = |

BUF |

|

Физический адрес запрашиваемой информации сравниваются с полем Tag. При совпадении устанавливается сигнал Hit и данные через буферы считываются на шину данных.

Оперативные запоминающие устройства – ОЗУ (RAM)

Статические SRAM

Ячейкой памяти является триггер на двух КМОП ключах (VT2-3 и VT4-5).

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uпит |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT1 |

|

|

|

VT2 |

|

|

VT4 |

|

|

|

|

|

|

|

VT6 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

_ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VT3 |

|

|

VT5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dj |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dj |

|||||||||||

|

ЛВ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Запись: на шины Dj и /Dj подается парафазный сигнал (если 1, то Dj=1, а /Dj=0, если 0, то Dj=0, а /Dj=1). На линию выборки (ЛВ) подается 1, транзисторы VT1 и VT6 открываются и данные с шины Dj записываются в ячейку памяти на КМОП ключах VT2-3 и VT4-5. Чтение информации: подается 1 на шину адреса и выходы ключей подключаются к шинам данных.

Достоинства: обладает высоким быстродействием, применяется для реализации кэш-памяти в микропроцессорах.

Недостатки: занимает большую площадь на кристалле, высокая стоимость микросхем.

|

|

A0 |

SRAM |

|

|

|

|

|

|

|

|

|

|

||

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

. |

|

DI/O |

|

||

|

|

A7 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

__ |

|

0 |

|

|

|

|

|

|

|

|

|||

|

|

cs |

|

1 |

|

|

|

|

|

|

|

||||

|

|

RW |

|

2 |

|

|

|

|

|

|

|

|

|||

|

|

|

. |

|

|

||

|

|

|

|

|

|||

|

|

__ |

|

. |

|

|

|

|

|

E0 |

|

7 |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Чтение |

Запись |

|

A |

A |

|

|

__ |

|

R/W |

R/W |

|

cs |

__ |

|

cs |

||

|

||

D |

D |

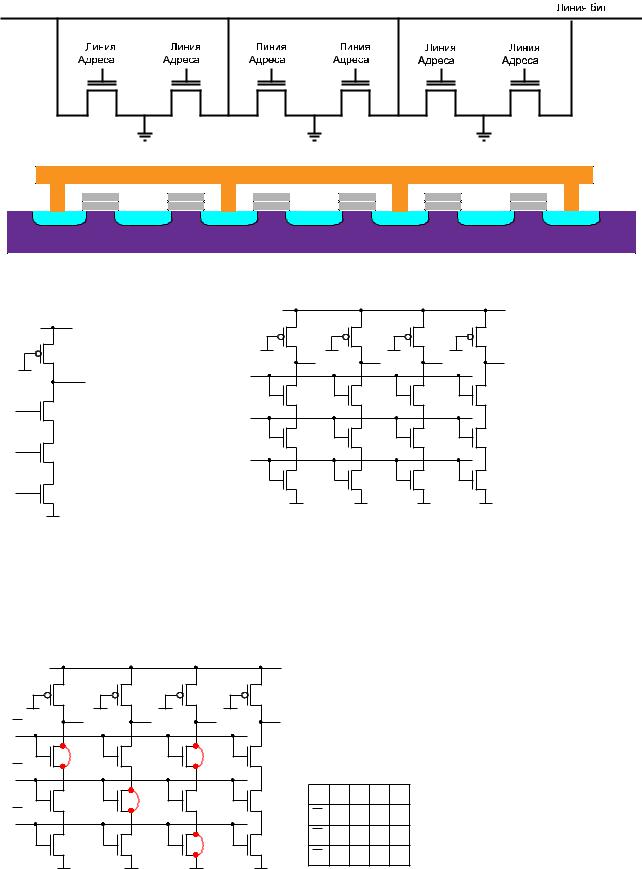

Динамические ОЗУ

Представляет собой один транзистор

ЛЗС |

Cз |

|

ЛВ

ЛЗС |

ЛВ |

|

|

|

|

n+ |

n+ |

Cз |

|

||

|

p |

|

ЛЗС – линия записи/считывания ЛВ – линия выборки

При чтении на ЛВ подают 1, заряд с Сз попадает на ЛЗС. Cз – паразитная емкость между подложкой и стоком. Заряд емкости -> запись, разряд -> считывание.

|

A |

|

|

|

|

___ |

DRAM |

|

|

|

RAS |

|

|

|

|

___ |

|

|

|

|

CAS |

|

DO |

|

|

|

|

|

|

|

R/W |

|

|

|

|

OE |

|

|

|

|

DI |

|

|

|

RAS |

|

|

|

|

CAS |

|

|

|

|

A |

А СТР |

А СТЛБ |

|

|

|

|

|||

R/W |

|

|

|

|

DO |

|

|

|

чтение |

|

|

|

D |

|

R/W |

|

|

|

|

DI |

|

|

|

запись |

|

|

|

|

|

RAS |

|

|

|

|

|

|

|

|

регене- |

CAS |

|

|

|

рация |

A |

А СТР |

А СТР |

D |

|

|

||||

Выполняют мультиплексирование адреса – на одни и те же входы подают адрес строки и RAS, а потом – адрес столбца и CAS.

RAS - Row Address Strobe (сигнал адреса строки) CAS – Column Address Strobe (сигнал адреса столбца)

Достоинство: малая площадь.

Недостаток: считывание разрушает информацию.

Требуется постоянная регенерация (реализуют на специальных схемах), что снижает быстродействие. Используется как основная оперативная память в компьютерах.

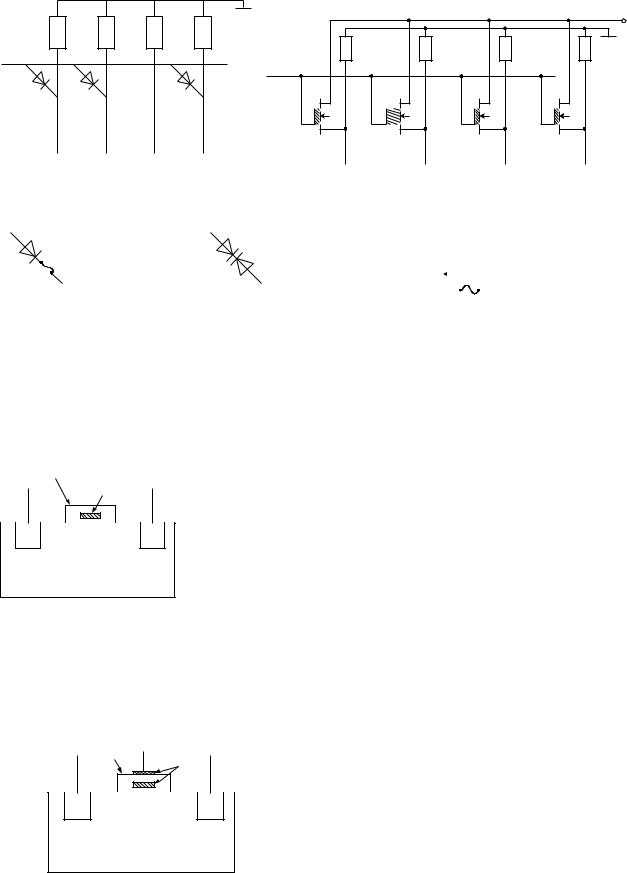

Постоянные запоминающие устройства ПЗУ (ROM)

Масочные

Uп

R |

R |

R |

|

|

|

A1 |

|

R |

R |

R |

R |

|

|

|

|

|

|

|

|

A1 |

|

|

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

Программируемые ПЗУ

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

При подаче высокого |

Вызывая пробой, получаем 1 |

|

|

|||||||||||

|

||||||||||||||

напряжения плавкая |

|

|

Вызывая пробой, получаем 0 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

вставка перегорает и |

|

|

|

|

|

|

|

|

|

|

|

|

||

образуется 0 |

|

|

|

|

|

|

|

|

|

|

|

|

||

Перепрограммируемые ПЗУ (репрограммируемые - РПЗУ) |

|

|

|

||||||

РПЗУ-УФ (стирание ультрафиолетом): |

|

|

|

|

|||||

|

На основе транзистора с плавающим затвором. |

|

|

|

|

||||

|

диэлектрик |

|

Программирование выполняют подачей напряжения исток (И) – |

||||||

И |

металл |

С |

сток |

(С) |

порядка 20 В, |

происходит |

лавинный |

пробой |

p-n |

|

З |

|

перехода. |

Электроны, |

обладающие |

большой |

энергией, |

||

|

|

проникают |

через диэлектрик на металлический затвор. После |

||||||

n+ |

|

n+ |

|||||||

|

|

|

снятия напряжения электроны остаются на затворе. Электроны, |

||||||

|

|

|

находящиеся на затворе, создают поле, мешающее созданию |

||||||

|

p |

|

канала между истоком и стоком. Таким образом, в диапазоне |

||||||

|

|

|

обычных рабочих напряжений, транзистор не открывается (канал |

||||||

исток-сток не создается). Это можно трактовать как запись «0» в ячейку памяти. |

|

|

|||||||

|

Стирание информации производят облучением затвора ультрафиолетом. УФ лучи |

||||||||

создают в диэлектрике тепловые токи и заряд с затвора стекает в подложку. Число циклов |

|||||||||

программирования десятки, сотни раз. |

|

|

|

|

|

||||

РПЗУ-ЭС (электрическое стирание):

Используют двухзатворный транзистор. Добавлен управляющий затвор.

И диэлектрик |

З металл С |

n+ |

n+ |

p

Запись производится аналогично РПЗУ-УФ.

Стирание: подается напряжение И-С порядка 20 В, а на затвор подается небольшое отрицательное напряжение => поле затвора выталкивает электроны из плавающего затвора.

Flash память

Использует технологию РПЗУ с электрическим стиранием, ячейки памяти объединены в блоки (группы ячеек памяти)

Boot Block Flash Memory – для загрузки |

Flash File Memory – вся память разделена на |

памяти |

блоки одинакового размера |

Разделяется на блоки (неравномерно) |

|

8 байт |

|

|

|

|

8 байт |

|

|

|

|

16 байт |

|

|

|

|

128 байт |

|

|

|

|

128 байт |

|

|

|

|

Схема NOR |

|

|

|

|

|

|

|

|

U |

Логический элемент 3ИЛИ-НЕ: |

|

|

|

|

U |

|

|

|

|

|

A1 |

|

|

|

out |

|

|

|

|

in1 |

A2 |

|

|

|

|

|

|

|

|

in2 |

A3 |

|

|

|

|

|

|

|

|

in3 |

|

|

|

|

|

D1 |

D2 |

D3 |

D4 |

Верхние транзисторы играют роль нелинейной нагрузки и всегда открыты.

На одну линию выборки адреса Аi подается 1. На линиях данных Di появляется: 0 – если транзистор открыт и соединен с линией данных (закорачивается на землю), 1 – если транзистор закрыт или не соединен с линией данных (нет закорачивания на землю).

Для флеш памяти NOR используется такая же матрица, только нет перемычек – все транзисторы подсоединены к линиям данных. Используются транзисторы с плавающим затвором с наведенным каналом.

Если на плавающем затворе есть заряд, то канал И-С при подаче напряжения на затвор не образуется. Т.е. транзистор не закорачивает линию данных на землю, и на выходе Di появляется 1. Если заряда нет, то при подаче напряжения на линию выборки (затвор транзистора) образуется канал и транзистор открывается, закорачивая линию данных на землю – на выходе 0.

Таким образом, для NOR – если есть заряд на плавающем затворе – то транзистор всегда закрыт (напряжение на управляющем затворе мало и не может ослабить влияние поля электронов на плавающем затворе – канал не образуется).

0 |

1 |

2 |

3 |

4 |

5 |

N |

N, GND |

N |

N, GND |

N |

N, GND |

N |

|

|

|

P |

|

|

|

Схема NAND |

|

|

|

|

Логический элемент 3И-НЕ |

|

|

|

U |

U |

|

|

|

|

|

D1 |

D2 |

D3 |

D4 |

out |

A1 |

|

|

|

|

|

|

|

|

in1 |

A2 |

|

|

|

|

|

|

|

|

in2 |

A3 |

|

|

|

|

|

|

|

|

in3 |

|

|

|

|

Алгоритм выборки строки: на все линии адреса подаются 1, на одну (интересующую нас) – подается 0. все транзисторы, на которые подаются 1 – открыты.

Транзистор, на который подан 0:

-должен быть открыт (красные соединения), если хотим выдать на линию данных Di 0 (т.е. все транзисторы открыты – выход Di закорочен на землю) – т.е. записан 0

-закрыт, если хотим выдать 1 – т.е. в ячейку записана 1.

|

|

|

U |

D1 |

D2 |

D3 |

D4 |

A1 |

|

|

|

A2 |

|

|

|

|

|

|

D1 D1 D1 D1 |

A3 |

|

|

A1 0 1 0 1 |

A2 1 0 1 1

A3 1 1 0 1

Для флеш-памяти используется транзистор с плавающим затвором и наведенным каналом, но режим работы транзистора и его характеристики отличаются от такого же транзистора для флеш-памяти NOR.

Напряжение на затворе подается такого значения, чтобы можно было компенсировать влияние заряда на плавающем затворе (если он там есть) и создать канал между истоком и стоком транзистора. Таким образом, при подаче на затвор напряжения (логической 1),