- •Микропроцессорные системы

- •Аппаратные средства поддержки реального и календарного времени в микропроцессорных и микроконтроллерных системах (таймеры и процессоры событий).

- •Организация подсистем прерываний в микропроцессорных и микроконтроллерных системах.

- •Основные функции инструментальных пакетов проектирования промышленных систем автоматизации и управления (на примерах инструментального пакета step7 или любого иного).

- •Открытые магистрально модульные системы. Основные требования к открытым системам реального времени. Стандарты мэк 61131.

- •Сегментация памяти в реальном и защищенном режимах микропроцессоров архитектуры ia-32.

- •Обмен данными в режиме пдп микропроцессорных и микроконтроллерных системах. Организация подсистем пдп.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами программирование режимов работы таймеров/счетчиков.

- •Поясните модульный принцип построения микроконтроллеров, компоненты процессорного ядра, состав и характеристики модулей. Примеры архитектур реальных микроконтроллеров.

- •Архитектура микропроцессоров Intel p6 и р7. Конвейеризация вычислительных процессов, использование кэш-памяти программ и данных, предсказание ветвлений и спекулятивное выполнение.

- •Организация вода – вывода данных в микропроцессорных системах.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами адресацию данных и команд, адресацию стека, выполнение косвенных переходов в программе.

- •Основные требования к открытым системам реального времени. Стандарты мэк 61131. Языки программирования плк. Стандарты мэк 61131.3.

- •Программируемые логические контроллеры (плк). Принципы работы плк сканирующего типа. Рабочие циклы и время реакции плк.

- •Организация подсистем прерываний в мп системах на микроконтроллерах платформы х86, Pentium.

- •Микропроцессоры платформы х86, Pentium: управление виртуальной памятью, средства защиты памяти.

- •Средства и методы разработки программного обеспечения и его отладки микроконтроллерных систем. Интегрированные среды проектирования.

- •Для микроконтроллеров к1816ве51 или st7, stm8, stm32 поясните и продемонстрируйте примерами ввод и вывод данных в параллельном и последовательном кодах.

- •Способы обмена данными в микропроцессорных системах. Пояснение выполните на примерах структурных схем и фрагментах программ обмена.

- •Какие способы обмена данными применяются в микропроцессорных системах. Поясните на примерах структурных схем и фрагментах программ обмена.

- •Основные функции инструментальных пакетов проектирования промышленных систем автоматизации и управления (на примерах инструментального пакета step7 или любого иного).

- •Системное и прикладное программное обеспечение магистрально-модульных систем.

- •Аппаратные средства поддержки реального и календарного времени в микропроцессорных и микроконтроллерных системах (таймеры и процессоры событий).

- •Ввод/ вывод информации в последовательных кодах: проблемы, примеры использования программируемых аппаратных средств, надежность и долговечность.

Организация подсистем прерываний в мп системах на микроконтроллерах платформы х86, Pentium.

При работе микропроцессорной системы часто возникают ситуации, когда требуется прервать выполнение текущей программы и перейти к подпрограмме, обеспечивающей необходимую реакцию системы на создавшиеся обстоятельства. Такие ситуации называются прерываниями или исключениями в зависимости от причин, вызывающих их возникновение. Специальные виды таких прерываний реализуются при отладке программ, для чего в состав процессора введены необходимые функциональные блоки, работа которых контролируется с помощью регистров отладки DR7-0.

Для современных процессоров и систем, реализуемых на их основе, применяется тестирование и самотестирование. Процессоры семейства Р6 содержат ряд средств, которые обеспечивают выполнение данных процедур.

В МПС на микропроцессорах платформы х86 стартовый адрес процедуры обслуживания прерываний определяется обращением к таблице прерываний через однобайтный вектор, формируемый аппаратными средствами подсистемы прерываний

В общем случае, все эти ситуации разделяются по принципу их обнаружения, источника возникновения и реакции на них на следующие три категории:

прерывания и особые ситуации — обнаруживаются и обрабатываются процессором в самые различные моменты времени и могут происходить как из внешних так и из внутренних источников, все другие типы экстраординарных ситуаций занимают более низкий уровень иерархии и могут обрабатываться, только если сперва заявят о своем существовании через прерывание или особую ситуацию;

исключительные ситуации FPU — могут возникать только при выполнении команд сопроцессораи полностью определяются его текущим состоянием, генерация исключительной ситуации в свою очередь может вызывать генерацию прерывания или особой ситуации, обработчик которой далее сам разбирается с тем, какое исключение произошло и какие действия в связи с этим следует предпринять;

исключительные ситуации SIMD — могут возникать только при выполнении SIMD-команди полностью определяются состояниемSIMD-регистровпроцессора, сообщают о своем возникновении также, как и исключения FPU через специальное прерывание, т.е. обработчик прерывания или особой ситуации должен сам программным путем определить причину его поступления.

Прерывания и особые ситуации — это специальные средства, обеспечивающие быструю реакцию процессора на внешние воздействия и прочие неожиданные ситуации. При поступлении прерывания или генерации особой ситуации выполнение программы прерывается, а управление передается специальной процедуре — обработчику прерывания или особой ситуации. В большинстве случаев, когда обработка прерывания или особой ситуации заканчивается, управление может быть возвращено в прерванную программу, которая продолжит свое выполнение с той самой точки, в которой она была остановлена. Процессор производит автоматическое сохранение/восстановление состояния для обеспечения этой возможности.

Существует два источника поступления прерываний и три типа особых ситуаций.

Прерывания:

внешние маскируемые прерывания — принимаются на выводе INTR# CPU, если флаг EFLAGS.IFустановлен, маскируемые прерывания не проходят;

внешние немаскируемые прерывания — принимаются на выводе NMI# CPU, механизм запрета немаскируемых прерываний отсутствует.

Особые ситуации:

генерируемые процессором особые ситуации — возникают в процессе и по результатам выполнения команд, разделяются на ошибки, ловушки и сбои;

программные прерывания — могут быть вызваны командами INTO,INT 3,INT n,BOUND;

особые ситуации генерируемые средствами самопроверки процессора.

Обработка прерываний в реальном и защищенном режимах

В реальном режиме для перехода к обслуживанию запроса прерывания или исключения процессор обращается к таблице векторов прерываний, которая располагается в начальной области памяти, начиная с адреса 0…0h. Элементами таблицы являются вектора прерываний – начальные адреса подпрограмм обслуживания различных типов прерываний. Вектор прерывания в реальном режиме содержит четыре байта (два байта база сегмента кода и два байта смещение). Размер всей таблицы может составлять 1024 байт, чтобы обслуживать до 256 возможных видов прерываний.

При возникновении прерываний процессор производит следующие действия:

- Заносит текущее значение регистров CS и IP в стек.

- Заносит текущее значение регистра FLAGS в стек/

- Запрещает прерывания, устанавливая признак IF в регистре EFLAGS.

- Устанавливает признаки TF=RF=AC=0 в регистре EFLAGS.

- Загружает в регистры CS, IP новое содержимое из таблицы прерываний.

Возврат из подпрограммы обслуживания прерываний выполняется командой IRET, которая восстанавливает сохраненное в стеке содержимое регистров FLAGS, CS, IP.

В защищенном режиме вызов подпрограмм обслуживания прерываний осуществляется через дескрипторную таблицу прерываний IDT (Interrupt Descriptor Table), которая может располагаться в любом месте адресного пространства памяти. Базовый линейный адрес этой таблицы хранится в регистре IDTR. Загрузка содержимого этого регистра осуществляется командой LIDT, а сохранение выполняется командой SIDT. Команда LIDT является привилегированной и может выполняться только программой, имеющей высший уровень привилегий CPL=0. Команда SIDT может быть выполнена при любом уровне привилегий программы.

47 16 15 0

|

Базовый адрес IDT |

Границы IDT |

Рис. 4.2. Формат содержимого регистра IDTR

Элементами таблицы IDT являются системные дескрипторы прерываний, имеющие размер по 8 байт. Поэтому максимальный размер таблицы IDT составляет 2 Кбайт при использовании всех 256 видов прерываний (исключений). В таблице могут содержаться три вида системных дескрипторов: шлюз прерывания, шлюз ловушки и шлюз задачи.

Шлюзы содержат селектор вызываемого при обслуживании сегмента, который поступает в регистр CS, и относительный адрес первой команды подпрограммы обслуживания, который загружается в регистр EIP. В дескрипторе также содержится бит Р, указывающий на присутствие (при значении Р=1) в памяти сегмента, в котором находится соответствующая подпрограмма обслуживания, и двух битовое поле gDPL, определяющее уровень привилегий шлюза (см. раздел 3.1). Бит D в байте доступа определяет режим работы процессора при обслуживании прерываний: если значение D=0, то процессор функционирует как 16-разрядный процессор 80286, если D=1, то обеспечивается 32-разрядный режим функционирования, характерный для процессоров 386, 486, Pentium, P6.

Передача управления через шлюз прерывания или шлюз ловушки может сопровождаться изменением уровня привилегий. Процессор проверяет значение gDPL в дескрипторе шлюза при выполнении программных прерываний, вызываемых командами INT n, INT3, INTO. Переход к выполнению подпрограммы обслуживания в этих случаях производится, если уровень привилегий текущей программы меньше или равен значению gDPL шлюза: CPL<=gDPL. Таким образом, величина gDPL ограничивает уровень привилегий программ, которые могут вызывать данную процедуру обслуживания. При выполнении других видов прерываний и исключений процессор игнорирует gDPL шлюза.

Уровень привилегий сегмента команд, в котором размещается подпрограмма обслуживания, должен быть меньше или равен уровню привилегий текущей программы: DPL<=CPL. Нарушение этого правила приводит к исключению типа #GP. Поэтому рекомендуется подпрограммы обслуживания прерываний и исключений располагать в сегментах с уровнем привилегий DPL=0, чтобы избежать ситуации, когда при поступлении запроса прерывания или исключения уровень текущей программы CPL окажется меньше, чем DPL сегмента команд обработчика прерывания.

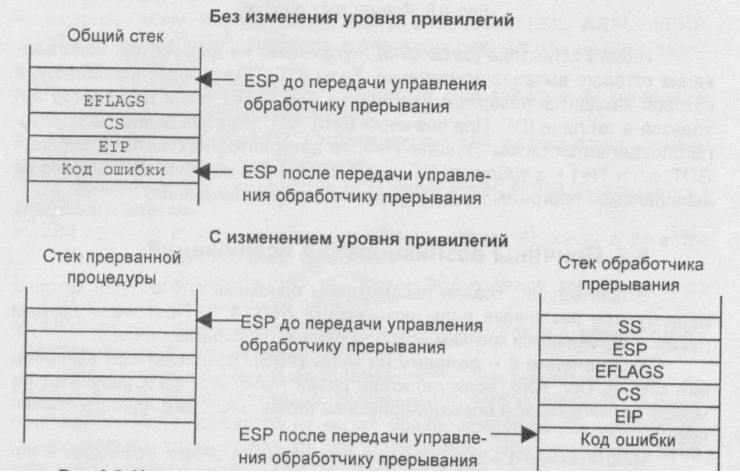

При возникновении прерывания процессор сохраняет в стеке следующую информацию (рис 4.3):

•Содержимое регистра SS прерванной процедуры (если имеет место изменение уровня привилегий).

•Содержимое регистра ESP прерванной процедуры (если имеет место изменение уровня привилегий).

•Содержимое регистра EFLAGS.

•Содержимое регистра CS.

•Содержимое регистра EIP.

•Код ошибки (если он формируется для данного исключения).

Рис. 4.3. Использование стека при прерываниях в защищенном режиме

После сохранения в стеке содержимого регистра EFLAGS процессор устанавливает в этом регистре значения признаков TF=VM=NT=0. Единственное различие между использованием шлюза ловушки и шлюза прерывания состоит в том, как процессор поступает с признаком IF. Если вызов подпрограммы обслуживания производится через шлюз прерывания, то процессор после сохранения в стеке содержимого регистра EFLAGS устанавливает значение признака IF=0, запрещая маскируемые прерывания. Если переход к подпрограмме обслуживания осуществляется через шлюз ловушки, то значение признака IF не изменяется.

Возврат из подпрограммы обслуживания прерывания осуществляется с помощью команды IRET. При восстановлении из стека содержимого регистра EFLAGS действуют следующие правила:

•поле IOPL восстанавливается только, если CPL=0,

•флаг IF изменяется только, если CPL < IOPL.

Формат дескриптора шлюза задачи при реализации прерываний и исключений имеет вид, представленный на рис.3.16. Когда прерывание обрабатывается через шлюз задачи, то процессор выполняет обычную процедуру переключения задач, как это описано в разд. 3.4.

При реализации некоторых исключений (табл. 4.1) процессор заносит в стек код ошибки, формат которого приведен на рис. 4.4.

31 16 15 3 2 1 0

|

Резервировано |

Индекс селектора |

TI |

IDX |

XT |

Рис. 4.4. Формат кода ошибки

Индекс селектора (биты 15-3) - указывает на дескриптор, использование которого вызвало исключение. Биты IDT, TI указывает на таблицу, в которой находится неверный дескриптор. Бит IDT=1, если дескриптор находится в таблице IDT. При значении бита IDT=0 размещение дескриптора определяется битом TI: если Tl=0, то дескриптор находится в таблице GDT, если Т1=1 - в таблице LDT. Бит ЕХТ=1, если исключение вызвано не выполняемой программой, а внешним сигналом прерывания.