- •Харківський національний університет будівництва та архітектури

- •Методичні вказівки

- •Для практичних занять з дисципліни

- •«Мікропроцесорна техніка»

- •Практична робота №1. Тема «Представлення чисел в різних системах числення».

- •Практична робота №2. Тема “ Арифметичні дії над двійковими числами”

- •Контрольні питання.

- •Практична робота №3 Тема “Програмна модель мікропроцесора кр580м80а”

- •14. Як перейти від останова до запуску мікропроцесора? Практична робота №4 Тема: «Програмування мікропроцесора. Послідовні алгоритми»

- •Таблиця 2.

- •Практична робота №5. Тема: «Програмування мікропроцесора. Алгоритми з розгалуженнями»

- •Таблиця 5

- •Рекомендована література.

Контрольні питання.

Яка максимальна кількість розрядів необхідно для подання результату додавання двох 8-розрядних двійкових чисел?

Чим відрізняються двійкові числа 101, 0101 і 0000 0101? Як це може вплинути на результат двійкового підсумовування?

З якої причини відбувається позика з більше старшого розряду числа?

В чому різниця між переносом у більше старший розряд і позикою з нього?

Практична робота №3 Тема “Програмна модель мікропроцесора кр580м80а”

Ціль роботи: знайомство з складовими елементами структурної схеми мікропроцесора КР580М80А та особливостями його роботи.

Форма звіту: письмовий звіт з результатами виконання практичного завдання.

Завдання 1. Вивчити структурну схему КР580М80А, призначення регістрів.

Методичні вказівки.

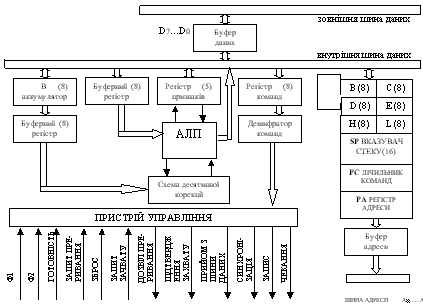

На мал. 1 приведена структурна схема БІС КР580ВМ80А. Коротко опишемо її вузли.

Регістри даних. Для збереження даних, що беруть участь в операціях, передбачено сім 8-розрядних регістрів. Регістр А, названий акумулятором, призначений для обміну інформацією з зовнішніми пристроями (тобто вміст цього регістра може бути видано або на вхід мікропроцесора, або з входу мікропроцесора в нього може бути прийняте від зовнішнього пристрою число), при виконанні арифметичних, логічних операцій і операцій зрушення він служить джерелом операнда (числа, що беруть участь в операції), у нього міститься результат виконаної операції.

Шість інших регістрів, позначених B, C, D, Е, Н, L, утворять блок регістрів загального призначення (РЗП) (назва зв'язана з тим, що в цих регістрах можуть зберігатися як дані, так і адреси). Ці регістри можуть використовуватися як одиночні 8-розрядні регістри. Якщо необхідно зберігати 16-розрядні числа, регістри поєднуються в пари ВС, DE, HL.

Покажчик стека. Регістр SP (16-розрядний) служить для адресації особливого виду пам'яті, називаної стеком (організація стека буде розглянута нижче).

Лічильник команд. Регістр PC (16-розрядний) призначений для збереження адреси команди; після вибірки з оперативної пам'яті поточної команди вміст лічильника збільшується на одиницю, і в такий спосіб формується адреса чергової команди (при відсутності безумовних і умовних переходів).

При звертанні до пам'яті як адресу може використовуватися і вміст пари регістрів блоку ΡΟΗ.

мал. 1

При видачі адреси уміст відповідного регістра передається в 16-розрядний регістр адреси РА, з якого далі через буфер адреси адреса надходить на 16-розрядну шину адреси. З цієї шини адреса може бути прийнятий в оперативну пам'ять. Число кодових комбінацій 16-розрядної адреси дорівнює 216, кожна з цих кодових комбінацій може визначати адресу (номер) однієї з осередків оперативної пам'яті. У такий спосіб забезпечується можливість звертання до пам'яті, що містить до 216 = 26 · 210 = 64 До 8-розрядних слів (байтів).

Арифметико-логічний пристрій. У 8-розрядному АЛУ передбачена можливість виконання чотирьох арифметичних операцій (додавання з передачею переносу в молодший розряд і без обліку цього переносу, вирахування з передачею займу в молодший розряд і без нього), чотирьох видів логічних операцій (кон’юнкції, диз'юнкції, нерівнозначності, порівняння), а також чотирьох видів циклічного зрушення. При реалізації арифметичних і логічних операцій одним з операндів служить вміст акумулятора, результат операції міститься в акумулятор. Циклічне зрушення виконується тільки над вмістом акумулятора.

Передбачено можливість виконання арифметичних операцій над десятковими числами, представленими в коді 8421. При збереженні десяткового числа розряди регістра поділяються на двох груп по чотирьох розряду, і в кожній групі розрядів зберігається одна десяткова цифра, представлена в коді 8421. Таким чином, у регістрі можна зберігати 2-розрядне десяткове число. При виконанні операції підсумовування десяткових цифр може знадобитися корекція результату шляхів додатка до нього числа 01102. Така корекція результату в кожній 4-розрядній групі результату в мікропроцесорі виконується схемою десяткової корекції (СДК).

Регістр ознак (РП). Цей 5-розрядний регістр призначений для збереження визначених ознак, що виявляються в числі, що являє собою результат виконання деяких операцій. П'ять тригерів цього регістра мають наступне призначення:

тригер переносу Тс при виконанні арифметичних операцій встановлюється в стан, що відповідає переносові зі старшого розряду числа, при виконанні операції зрушення в стан, що відповідає умістові висунутого з акумулятора розряду;

тригер нуля Tz встановлюється в стан 1, якщо результат операції АЛУ або операції збільшення вмісту регістра дорівнює нулеві;

тригер знака Ts встановлюється в стан, що відповідає значенню старшого розряду результату операції АЛУ або операції збільшення вмісту регістра;

тригер чіткості Тр встановлюється в стан I, якщо число одиниць у розрядах результату парне;

тригер додаткового переносу tv зберігає виникаючий при виконанні операції перенос з 4-го розряду.

Блок керування. Складається з регістра команд, куди приймається перший байт команди, і пристрою керування, що формує керуючі сигнали, під дією яких виконуються мікро операції в окремих вузлах. Керуючий пристрій містить виконану на програмувальній логічній матриці керуючу пам'ять, у якій зберігаються мікропрограми окремих операцій. Користувач не може змінити вмісту керуючої пам'яті, а виходить, і складу команд.

Буфери.

Буфери даних і буфери адреси забезпечують зв'язок центрального процесора з зовнішніми шинами даних і адреси. Особливість буферів полягає в тому, що в кожнім розряді вони використовують логічні елементи з трьома станами. У них крім станів 0 і 1 передбачено ще третій стан, у якому вони мають практично нескінченний вихідний опір і виявляються відключеними від відповідних шин. Такі буфери дозволяють процесорові відключатися від зовнішніх шин (шин даних і адреси), надаючи них у розпорядження зовнішніх пристроїв, а також використовувати ту саму шину даних як для прийому даних (тобто як вхідну шину), так і для видачі даних (тобто як вихідну шину), що скорочує число висновків мікросхеми.

ВХІДНІ

ЛОГІЧНІ ЕЛЕМЕНТИ

ВИХІДНІ

ЛОГІЧНІ ЕЛЕМЕНТИ

мал.5.2

На мал.5.2 показаний принцип двохнаправленного обміну даними між внутрішньою і зовнішньої шиками даних. Якщо здійснюється прийом даних (передача даних із зовнішньої шини даних на внутрішню шину даних), відключаються, переходячи в третій стан, вихідні логічні елементи; при видачі даних (передачі з внутрішньої шини на зовнішню шину) відключаються вхідні логічні елементи.

Завдання 2. Вивчити формат даних і команд.

Методичні вказівки.

Дані (обробляється інформація і результати обробки) зберігаються в оперативній пам'яті й у процесорі у виді 8-розрядних двійкових чисел . Таким чином, слово має наступний формат.

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

БАЙТ ДАНИХ

Для команд використовуються одно-, двох- і трьох байтові формати. Більшість команд є однобайтовими.

Однобайтовий формат команди:

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

КОД ОПЕРАЦІЇ

Двохбайтовий формат команди.

|

B1 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

КОД ОПЕРАЦІЇ

|

B2 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

ОПЕРАНД ЧИ НОМЕР (АДРЕСА)ПРИСТРОЮ ВВОДА-ВИВОДУ

У першому байті двохбайтовий команди указується вид виконуваної операції, у другому байті приводиться число, що є операндом при виконанні операції, або адреса пристрою введення або висновку при обміні даними з периферійними пристроями

Трьохбайтовий формат команди:

|

B1 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

B2 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

B3 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Байти трьохбайтової команди мають наступне призначення: у першому указується вид виконуваної операції, що випливають два байти використовуються для вказівки двохбайтової адреси команди (при виконанні безумовних і умовних переходів, звертанні до підпрограм), або адреси чарунки оперативної пам'яті, уміст якого є операндом, або двохбайтового операнда. В усіх випадках байт В2 є молодшим, байт В3, — старшим.

Завдання 3. Вивчити способи адресації в командах мікропроцесора. Методичні вказівки.

Для виконання будь-якої операції в команді повинна бути указівка про вид операції, а також відкіля беруться числа, що беруть участь в операції і куди міститься результат виконаної операції (тобто вказівка про джерела і приймач операндів). Під способами адресації рОЗПміють способи вказівки джерел і приймачів операндів. Опишемо способи адресації, що використовуються в мікропроцесорі.

Пряма адресата. При цьому способі адресою операнда являється зазначена у команді (у байті коду операції) адреса регістра мікропроцесора (див. мал. 1). Адреси регістрів приведені в наступній таблиці.

Під М рОЗПміється чарунка оперативної пам'яті, адресою якого служить вміст пари регістрів HL.

-

РЕГІСТР

АДРЕСА РЕГІСТРА

B

C

D

E

H

L

M

A

000

001

010

011

100

101

110

111

Покажемо деякі приклади команд із прямою адресацією, взятих із таблиці системи команд мікропроцесора. Тут під мнемонікою команди рОЗПміють її скорочене позначення, що полегшує запам'ятовування команди.

У кодовій комбінації команди 01 001 010 два старших розряди (01) визначають вид операції (операція пересилання вмісту одного регістра в іншій), у наступних двох 3-розрядних групах(001 і 010)приведені адреси регістрів С и D. Команда представляє собою операцію пересилання в регістр С умісту регістра D.

У команді 10 000 010 п'ять старших розрядів (10 000) представляють вид операції (операції суми); у трьох молодших розрядах (010) зазначена адреса регістра D, що служить джерелом операнда. При виконанні операції суми джерелом іншого операнда і приймачем результату виконаної операції є акумулятор А.

Безпосередня адресація. При цьому способі адресації операнди (один або два) задаються безпосередньо в команді слідом за байтом коду операції в другому байті або в другому і третьому байтах.

-

Мнемоніка команди

Кодова комбінація команди

Виконуюча операція

MOV C, D

01001010

C

(D)

(D)ADD D

10000010

A

(A)+(D)

(A)+(D)

Приклади команд з безпосередньою адресацією.

1 )ADI

B1 11000110 A

(A)+<B2>

)ADI

B1 11000110 A

(A)+<B2>

B2 01001100

2 )MVI

D B1 00010110 D

(B2)

)MVI

D B1 00010110 D

(B2)

B2 01001110

3

)LXI

D B1 00010001 D

<B3>; E

<B2>

)LXI

D B1 00010001 D

<B3>; E

<B2>

B2 01100101

B3 10100101

<Bi> - вміст байту Bi команди.

Команда з мнемонікою ADI передбачає підсумовування вмісту акумулятора з числом, приведеним у другому байті команди (у прикладі це число дорівнює 4С16).

Команда MVI робить пересилання числа, приведеного в другому байті команди (у прикладі це число дорівнює 4Е16), у регістр D, адреса якого (010) зазначений у розрядах D5 D4 D3 перші байти команди.

Команда LXI робить пересилання чисел, приведених у другому і третьому бантах (у прикладі — чисел 6516 і А516)відповідно в молодший і старший регістри пари регістрів DE. У розрядах D5 D4 D3 перші байти пари регістрів зазначена адресою (010) одного з регістрів цієї пари.

Непряма· адресація. При цьому способі адресації в команді відзначається пара регістрів блоку РОН (шляхом вказівки адреси одного з регістрів цієї пари), уміст якої служить адресою, по якому в оперативній пам'яті знаходиться операнд.

По команді LDAX В акумулятор завантажується вмістом чарунки оперативної пам'яті, адресою якого служить уміст пари регістрів ВР (для вказівки саме цієї пари регістрів у розрядах D5 D4 D3 команди приведена адреса 001 регістра З).

По команді STAX У вміст акумулятора запам'ятовується в чарунки, адресою якого служить уміст пари регістрів ВР (для вказівки пари регістрів у розрядах D5 D4 D3 команди приведена адреса 000 регістра В).

Завдання 4. Вивчити принцип роботи мікропроцесора.

Методичні вказівки.

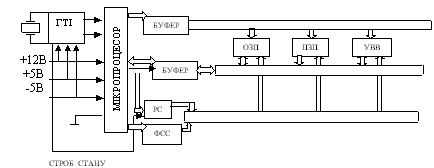

На мал. 3 показана структурна схема мікропроцесорної системи на МПК КР580. Генератор тактових імпульсів (ГТИ) формує дві імпульсні послідовності Ф1 і Ф2, необхідні для тактування роботи мікропроцесора. Імпульси двох послідовностей не повинні перекриватися в часі і повинні мати амплітуду 12В. ПЗП може бути використаний для збереження програми, ОЗП — для збереження даних.

Загальний принцип функціонування мікропроцесорної системи полягає в наступному. З мікропроцесора на шину адреси видається адреса чергової команди. Лічена по цій адресі з пам'яті (наприклад, із ПЗП) команда надходить на шину даних і приймається в мікропроцесор, де вона виконується. У лічильнику команд мікропроцесора формується адреса наступної команди. Після виконання даної команди на шину адреси надходить адреса наступної команди і т.д. При виконанні команди можуть знадобитися додаткові звертання до пам'яті для виклику в мікропроцесор додаткових байтів команди (у випадку двох-, трьох- байтових команд), операндів або для запису в пам'ять числа, виданого з мікропроцесора.

Розглянемо докладніше процес виконання команди. Цей процес розбивається на цикли, що позначаються M1, M2, M3, M4, M5. У кожнім циклі виробляється одне звертання мікропроцесора до пам'яті або до пристрою введення або виведення (УВВ) (виключення складає лише виконання команди DAD). У залежності від типу команда може бути виконана за один цикл (M1) або за два цикли (M1, M2 )або за три цикли (M1, M2, M3) і т.п. Самі довгі за часом виконання команди виконуються в п'ять циклів (M1,..., M5).

Мал.3.

Мал.3.

Кожен цикл включає кілька тактів, що позначаються Т1, Т2, Т3, Т4, Т5 . Цикли можуть містити три (Т1,.... Т3, чотири (Т1,..., Т4) такти або п’ять (Т1,..., Т5) тактів. Перші три такти у всіх циклах використовуються для організації обміну з пам'яттю й УВВ, такти Т4 і Т5 (якщо вони присутні в циклі) — для виконання внутрішніх операцій у мікропроцесорі. На мал. 5.5 показана тимчасова діаграма циклу з п'яти тактів.

Відлік тактів виробляється від позитивних фронтів імпульсів Φ,. Розглянемо цикл M1. У такті Т1 уміст лічильника команд видається на шину адреси, адреса приймається пам'яттю, де починається процес читання байта команди з зазначеного чарунки. У такті Т2 перевіряється наявність сигналу (рівня лог. 1) на вході Готовність (див. мал.5.1). Цей сигнал подається на вхід мікропроцесора через інтервал часу, достатній для завершення процесу читання з пам'яті. Якщо на вході Готовність сигнал відсутній (діє рівень лог.0), то мікропроцесор встановлюється в режим чекання, у якому кожен наступний такт розглядається як такт Т2 доти, поки не з'явиться сигнал на вході Готовність. З приходом цього сигналу мікропроцесор виходить з режиму чекання, переходячи в такт Т3. У цьому такті виданий з пам'яті байт команди із шини даних приймається в мікропроцесор, де він помішається в регістр команд. У такті Т4 аналізується прийнятий байт команди і з'ясовується, чи потрібні додаткові звертання в оперативну пам'ять. Якщо такі звертання не потрібні (команда однобайтова й операнди знаходяться в регістрах мікропроцесора), то в цьому ж такті або з використанням додатково такту Т5 виконується операція, що передбачається командою.

Якщо необхідні додаткові звертання в оперативну пам'ять, то після такту Т4 цикл M1 завершується і відбувається перехід до циклу M2- Нехай, наприклад, команда однобайтова, але в операції повинний брати участь операнд, що зберігається в оперативній пам'яті. Тоді в циклі M2пронсходят наступні процеси: у такті Т1, видається адреса комірки пам'яті, у такті Т2 перевіряється наявність сигналу на вході Готовність (сигналу об тон, що пройшов інтервал часу, достатній для читання з пам'яті). З появою цього сигналу відбувається перехід до такту Т3, у якому видане з пам'яті число із шини даних приймається в мікропроцесор, і в цьому ж такті виконується операція, що передбачається командою.

При виконанні більшості команд у випадках, коли відбуваються додаткові Звертання до пам'яті, перший цикл М1 містить чотири такти, у кожнім наступному циклі утримується три такти і відбувається одне додаткове звертання до пам'яті.

Інформація про стан мікропроцесора.

У кожнім циклі в інтервалі часу від моменту позитивного фронту імпульсу послідовності Ф1 у такті Т1 до моменту позитивного фронту, імпульсу Ф2 я такті Т2 мікропроцесор видає на вихід Синхронізація (мал. 1) рівень лог.1 і на шину даних — інформацію про стан. БРЕШИ (див. мал. 5,3) формує строб стану, яким здійснюється прийом інформації про стан мікропроцесора із шини даних я регістр стану (тимчасове положення строба стану показане на мал. 5.5). У табл. 5.3 показані призначення сигналів у розрядах коду стану мікропроцесора. У табл. 5.4 приведена відповідність цих сигналів окремим видам циклів.

|

РОЗРЯД КОДУ СТАНУ |

ПРИЗНАЧЕННЯ СИГНАЛУ В РОЗРЯДІ |

|

D0

D1

D2

D3

D4

D5

D6

D7 |

ПІДТВЕРДЖЕННЯ ПЕРЕРИВАННЯ: ВИКОРИСТОВУЕТЬСЯ ДЛЯ СТРОБУВАННЯ КОМАНДИ RSTВ МІКРОПРОЦЕСОР З ПРИСТРОЮ ,ЗАПРОШУЮЧОГО ПЕРЕРИВАННЯ

ЗАПИС-ВИВІД : РІВЕНЬ ЛОГ.0 СВІДЧИТЬ ПРО ТЕ ,ЩО В ДАНОМУ ЦИКЛІ БУДЕ ПРОХОДИТИ ЗАПИС (ВИДАННЯ ІНФОРМАЦІЇ З МІКРОПРОЦЕСОРА В ОПЕРАТИВНУ ПАМ’ЯТЬ)ЧИ ВИВІД (ПЕРЕДАЧА ІНФОРМАЦІЇ З МІКРОПРОЦЕСОРУ В УВВ ); РІВЕНЬ ЛОГ.1 ОЗНАЧАЕ ,ЩО ПРОХОДЕ ЗЧИТУВАННЯ (ПРИЙОМ ІНФОРМАЦІЇ З ОПЕРАТИВНОЇ ПАМ’ЯТІ) ЧИ ВВОД,(ПРИЦОМ З УВВ)

НА АДРЕСНІЙ ШИНІ ВСТАНОВЛЕНО ЗМІСТ ВКАЗУВАЧА СТЕКУ

ПІДТВІРДЖЕННЯ ОСТАНОВУ МІКРОПРОЦЕСОР В СТАНІ ОСТАНОВУ

НА АДРЕСНІЙ ШИНІ ВСТАНОВЛЕНО НОМЕР ЗОВНІШНЬОГО ПРИСТРОЮ І ЗДІЙСНЮЄТЬСЯ ВИВІД ЗМІСТУ АККУМУЛЯТОРА НА ПРИСТРІЙ ВИВОДУ

МІКРОПРОЦЕСОР ПРИЙМАЄ ПЕРШИЙ БАЙТ КОМАНДИ

НА АДРЕСНІЙ ШИНІ ВСТАНОВЛЕНО НОМЕР ПРИСТРОЮ ВВОДУ І ЗДІЙСНЮЄТЬСЯ ВВОД ІНФОРМАЦІЇ З ПРИСТРОЮ ВВОДУ В АККУМКЛЯТОР МІКРОПРОЦЕСОРА

В ДАНОМУ ЦИКЛІ ПРОХОДЕ ЗЧИТУВАННЯ З ПАМ’ЯТІ В МІКРОПРОЦЕСОР |

Таблиця 5.3

|

ВИД ЦИКЛУ |

СТАН МІКРОПРОЦЕСОРА | |||||||

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 | |

|

ВИБІРКА ПЕРШОГО БАЙТУ КОМАНДИ ЗЧИТУВАННЯ З ПАМЯТІ ЗАПИС В ПАМЯТЬ ЗЧИТУВАННЯ СТЕКУ ЗАПИС СТЕКУ ВВОД В УВВ ВИВІД З УВВ ПІДТВЕРДЖЕННЯ ПРЕРИВАННЯ ПІДТВЕРДЖЕННЯ ОСТАНОВУ ПІДТВЕРДЖЕННЯ ПРЕРИВАННЯ ПРИ ОСТАНОВІ |

1 1 0 1 0 0 0 0 1 0 |

0 0 0 0 0 1 0 0 0 0 |

1 0 0 0 0 0 0 1 0 1 |

0 0 0 0 0 0 1 0 1 1 |

0 0 0 0 0 0 0 0 1 1 |

0 0 0 1 1 0 0 0 0 0 |

1 1 0 1 0 1 0 1 1 1 |

0 0 0 0 0 0 0 1 0 1 |

Таблиця 5.4

Завдання 5. Опанувати системою команд мікропроцесора.

Методичні вказівки.

Команди розбиті на сім груп. Група може містити кілька видів операцій. Кожен вид операцій характеризується деякою структурою кодових комбінацій команд, де замість ri повинний бути підставлений адреса регістра я замість Ki - 3-розрядна кодова комбінація, що визначає конкретний тип команди.

У таблиці зазначене число байтів, що утримуються в команді, число циклів і тактів, у які виконуєте· команда (у знаменнику зазначене число циклів до тактів у випадках, коли як адресу регістра зазначена комбінації 110 і потрібне додаткове звертання в оперативну пам'ять для вибірці операнда, адресою якого служить уміст пари регістрів HL).

Для кожного типу команди показано, як формуються ознаки в п'ятьох тригерах регістра ознак. Прийнято наступних систем· позначень:

+ означає, що ознака в даному тригері формується;

- означає, що відповідна ознака при виконанні даної команди не формується і у тригері зберігається значення ознаки, сформоване при виконанні попередніх команд;

0 означає установку тригера в стан 0;

1 означає установку тригера в стан 1.

Відзначимо наступні особливості формування ознак:

команди пересилання і переходів не змінюють стану тригерів ознак;

команди збільшення або зменшення вмісту одиночного регістра використовують всі ознаки, за винятком ознаки переносу,

команди збільшення або зменшення вмісту пара регістрів не змінюють стану тригерів ознак;

команди арифметичних операцій використовують всі ознаки;

при виконанні логічних операцій тригери переносів Тс і Тv скидаються в стан 0;

команди додавання вмісту пари регістрів використовують тільки ознаку переносу С.

Завдання 6. Опанувати принципи роботи із стеком.

Методичні вказівки.

Стек — пам'ять з визначеною (спрощеною) формою адресації. У мікропроцесорній системі на МПК КР580 стек організується в такий спосіб. В ОЗП команди розміщуються в чарунках з молодшими, послідовно наростаючими адресами. Стек використовує чарунку зі старшими адресами, і в міру заповнення стека займаються чарунки з адресами, що послідовно убувають (мал. 6, а), Особливість організації стека полягає в наступному. Покажчик стека SP містить так звану адресу входу в стек, при читанні зі стека здійснюється вибірка вмісту чарунки за адресою входу в стек (адреса, що зберігається в SP); при записі число вводиться в стек, за адресою, на одиницю меншою вмісту SP; одночасно з записом і читанням змінюється вміст SP: при записі зменшується, а при читанні збільшується на одиницю.

|

0 |

|

|

1 |

|

|

2 |

|

|

3 |

|

|

. . |

. . |

|

|

|

|

|

|

|

(SP) |

|

|

. . |

. . |

|

N-2 |

|

|

N-1 |

|

|

N |

|

|

ЧАРУНКИ КОМАНДИ |

|

АДРЕСА ЧАРУНКИ |

Мал. .6

|

ЧАРУНКИ СТЕКУ |

а)

аа A-1

A-2

A

SP SP

ЗАПИС ЗАПИС СТАРШОГО МОЛОДШОГО БАЙТА СЛОВА СТЕК

БАЙТА СЛОВА В СТЕК В СТЕК

б)

А

А+1 A+2

А

А

SP A+1

SP SP A+2

стек

стек

стек

стек

стек

в)

Обмін зі стеком виконується двобайтовими словами, що займають дві чарунки пам'яті. Припустимо, що покажчик стека зберігає адресу А. При введенні нового слова його байти повинні бути поміщені в пару сусідніх із входом у стек чарунок, що мають адреси А - 1 і А - 2. Таким чином, введення в стек зводиться до наступної послідовності дій: вміст SP зменшується на одиницю і по адресі, що утвориться, міститься старший байт введеного двобайтового слова; потім вміст SP знову зменшується на одиницю і по адресі, що утвориться, міститься молодший байт слова, що вводиться, (мал. 6,б). Ми бачимо, що SP щоразу вказує адресу чарунки, що є входом у стек.

Вивід даних зі стека здійснюється також двобайтовими словами. При цьому щоразу доступна для читання лише чарунка, адреса якого утримується в SP. Якщо покажчик стека зберігає адресу А, то байти виведеного зі стека слова вибираються з чарунок пам'яті, що мають адреси А і А + 1. Таким чином, вибір слова зі стека зводиться до такої послідовності дій: читання молодшого байта виведеного слова з чарунки, адресою якої служить вміст SP, і збільшення вмісту SP на одиницю; потім читання старшого байта виведеного слова за адресою, що зберігається в SP, і збільшення вмісту SP на одиницю (мал. 6,в).

Про такий принцип функціонування, коли читається послідовно поміщена в пам'ять інформація, говорять як про принцип "останнім увійшов — першим вийшов". Як бачимо, при запису та читанні здійснюється звертання в чарунку, адресу якої зберігає SP. Це спрощує адресацію пам'яті, але виключає можливість звертання в довільну чарунку пам'яті.

Розглянемо деякі команди операцій зі стеком.

Установка в SP будь-якого початкового значення здійсню по команді пересилання SPHL (11 111 001), по якій у SP пересилається вміст пари регістрів HL.

Команда введення з пари регістрів DE у стек: PUSH D (11 010 101). У розрядах DSD4D3 кодової комбінації команди зазначена адреса 010 старшого регістра пари DE. По цій команді виконуються наступні дії: SP (SP) - 1, [(SP)] (D), SP (SP) - 1, [(SP)] (Е).

К

оманда

пересилання зі стека в пари

регістрів DE: POP D (1 1 0 1 0 00 1). Тут

у розрядах D5

D4

D3

кодової

комбінації команди зазначена

адреса 010 старшого

регістра

пари DE. По даній команді виконуються

дії

:Е (SP)], SP (SP)+1,D (SP)J,SP (SP) + 1.

оманда

пересилання зі стека в пари

регістрів DE: POP D (1 1 0 1 0 00 1). Тут

у розрядах D5

D4

D3

кодової

комбінації команди зазначена

адреса 010 старшого

регістра

пари DE. По даній команді виконуються

дії

:Е (SP)], SP (SP)+1,D (SP)J,SP (SP) + 1.

Завдання 7. Особливі умови роботи мікропроцесора.

Методичні вказівки.

Запуск мікропроцесора

Після подачі на відповідні входи мікропроцесора живлячих напруга і тактових імпульсів послідовностей Ф1 і Ф2 подається сигнал рівня лог.1 на вхід Скидання. Цим сигналом скидаються в стан лог.0 лічильник команд PC, регістр команд, розміщені в керуючому пристрої тригери дозволу переривань; підтвердження захоплення і чекання. Після закінчення дії сигналу Скидання (при переході сигналу від рівня лог.1 до рівня лог.0 мікропроцесор починає працювати з такту T1 циклу М1, і видає на шину адреси нульове значення адреси. Уміст регістрів блоку ???, акумулятора, регістра ознак міняється тільки в процесі виконання команд.

Стан захоплення

Стан захоплення характеризується тим, що мікропроцесор, закінчуючи виконання поточного циклу команди, переводить буфери шини даних і буфери шини адреси в третій стан. При цьому мікропроцесор відключається від зовнішніх шин, надаючи них у розпорядження деякого зовнішнього пристрою, і припиняє роботу.

Перехід у стан захоплення відбувається в такий спосіб. Від зовнішнього пристрою надходить сигнал рівня лог.1 на вхід Запит захоплення. Цей сигнал при негативному фронті імпульсу Ф1 такту Т2 приймається в тригер захоплення керуючого пристрою. Керуючий пристрій закінчує виконання поточного циклу, переходить у стан захоплення і підтверджує це видачею сигналу на виході Підтвердження захоплення. Сигнал на виході Підтвердження захоплення видається при позитивному фронті імпульсу Ф1 у такті Т3, якщо поточний цикл не виявляєте циклом запису; у противному випадку цей сигнал видається при позитивному фронті імпульсу Ф1 такту, що випливає за тактом Т3.

Після закінчення дії сигналу Захоплення (при переході від рівня лог. 1 до рівня лог. 0) мікропроцесор починає виконання наступного циклу з місця, де було припинене виконання програми.

Стан переривання

У мікропроцесорі передбачена можливість по запитах зовнішніх пристроїв переривати виконання поточної програми і переходити на виконання нової програми, так називаної програми, що перериває, (або програми обслуговування переривання). Після закінчення виконання програми, що перериває, мікропроцесор повертається до виконання основної програми з команди, на якій відбулося переривання.

Якщо на деякій ділянці програми допускається її переривання, то при складанні програми на початку цієї ділянки передбачається команда EI, по якій тригер дозволу переривання в керуючому пристрої мікропроцесора встановлюється в стан лог. 1, а наприкінці дільниця-команда DI, при виконанні якої тригер скидається в стан лог. 0. Стан тригера видається на вихід дозвіл переривання.

Процес переривання зв'язаний з наступними діями. Від зовнішнього пристрою надходить сигнал рівня лог. 1 на вхід Запит переривання. Якщо переривання дозволене (тобто на виході Дозвіл переривання мається рівень лог.1), те після закінчення виконання поточної команди тригер дозволу переривання скидається в стан лог.0, а в інформації про стан мікропроцесора, видаваному на шину даних, з'являються сигнали Підтвердження переривання (у розряді D0), Уведення (у розряді D1) і сигнал про те, що в даному циклі робите· прийом першого байта команди (у розряді D5). Сигнал Підтвердження переривання використовується в якості строба для видачі зовнішнім пристроєм на шину дані команди RST (команди рестарт).

При виконанні команди RST уміст лічильника команд PC запам'ятовується в стеці, а в PC записується адреса першої команди програми, що перериває. Ця адреса задається в такий спосіб. Команда RST має структуру 11 ААА 111, і в лічильник команд заноситься значення 00 000 000 00 ААА 000, що і служить адресою першої команди програми, що перериває. Задаючи визначену трьохрозрядну комбінацію ААА, зовнішній пристрій може задати адреса першої команди однієї з восьми програм, що переривають.

Після закінчення виконання програми, що перериває, повернення в основну програму відбувається в такий спосіб. Програма, що перериває, закінчується командою RET (повернення з підпрограми). У процесі виконання цієї команди адреса команди основної програми, перед якою відбулося переривання, вибирається зі стека і передається в регістр адреси, а збільшене на одиницю значення заноситься в лічильник команд.

Стан останова

У системі команд мікропроцесора мається команда HLT(останов), що викликає припинення виконання програми і перехід у стан останова. Цей стан характеризується тим, що буфери шини адреси і шини даних переходять у третій стан, мікропроцесор відключається від зовнішніх шин і на виході Чекання встановлюється рівень лог. 1.

Стан останова може бути перервано сигналами запуску мікропроцесора або перекладу його в стан переривання.

Завдання 8. Виконати контрольне завдання та відповісти на запитання.

1. Перерахувати операції, які виконує АЛП мікропроцесора КР580.

2. Для чого використовується схема десяткової корекції?

3. Перерахувати регістри загального призначення та особливості їх адресації.

4. Як працює регістр ознак?

5. Скласти алгоритм роботи пам'яті типу стек.

6. Які особливості роботи регістра – лічильника команд?

7. Перерахувати сигнали пристрою управління та їх призначення.

8.Описати призначення генератора тактових імпульсів.

9. Описати цикли і такти в роботі мікропроцесора. Від чого залежить кількість тактів для виконання команди?

10. Опишіть запуск мікропроцесора.

11. Опишіть стан захоплення.

12. Опишіть стан переривання.

13. Як припинити виконання команд?