Kon_Pr_pids_sign_27-05-14

.pdf

U |

|

U |

|

U |

|

|

R4 |

. |

|

||

âèõ |

2 |

1 |

R1 |

|

|||||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||

Коефіцієнт підсилення диференційного |

сигналу K |

|

Uвих |

за умови R1 = R2, R3 = R4 |

|||||||

U |

|

U |

|||||||||

|

|

|

|

|

|

|

|

|

2 |

1 |

|

визначається відношенням опорів ОЗ R4 та вхідного опору R1.

5.2. Пристрої аналогової обробки сигналів

Використовуючи той чи інший вид ОЗ, на базі ОП ми можемо реалізувати пристрої аналогової обробки сигналів, тобто пристрої, які дають змогу виконувати математичні операції з аналоговими сигналами. При цьому досить просто реалізувати схеми інтегрування, диференціювання, логарифмування, потенціювання, додавання. Використання комбінацій зазначених операцій дають змогу виконати операції

множення, ділення тощо.

Інтегруюча ланка Схема інтегрування електричного сигналу може бути здійснена за схемою рис.5.9.

Рис.5.9 Схема електрична принципова інтегруючої ланки на ОП.

Операція інтегрування аналогових сигналів найбільш ефективно виконується з допомогою схеми, виконаної на ОП, ОЗ в якій містить конденсатор, ємність якого за визначенням.

C UQ .

Використовуємо принцип віртуального замикання:

|

|

|

U |

âõ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

1 |

t |

|

|

I |

|

|

|

, |

U |

|

|

|

|

U |

|

|

|

, |

|

|

де |

|

U |

|

|

|

|

I |

|

(t) d (t) . |

|||||||||

|

âõ |

|

R |

|

|

âèõ |

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

C |

|

C |

C |

0 |

âõ |

|

||||||||

Отже, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

I |

|

|

(t) d (t) . |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

âèõ |

|

C |

âõ |

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Підставивши відповідне значення Івх, отримаємо |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

U |

|

|

|

|

|

1 |

|

|

t U âõ(t) |

d (t) ; |

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

âèõ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

C 0 |

|

|

R |

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|||

або |

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

U |

|

|

(t) d (t) . |

|

|

|

||||||||||||||

|

|

|

|

|

|

âèõ |

|

|

|

|

|

|

âõ |

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RC |

0 |

|

|

|

|

|

|

|

|

|

|||||||||||

Якщо величина вхідної напруги – константа, то вихідна напруга буде дорівнювати

Uâèõ RC1 U t U0 .

Якщо вхідний сигнал буде гармонійним, наприклад, косинусоїдним

33

Uâõ(t) U cos t ,

то |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

U |

âèõ |

|

|

sin t U U |

0 |

. |

|

||||||

|

RC |

|

|

|||

Зростання частоти вхідного сигналу буде супроводжуватись зменшенням амплітуди вихідного зі швидкістю – 6 дб (тобто 6 дб при зміні у два рази). Така залежність амплітуди вихідного сигналу від частоти є характерною ознакою інтегруючої ланки.

При використанні реального операційного підсилювача слід враховувати вхідний струм Ів, при відсутності сигналу, й зміщення нуля підсилювача (наявність напруги U0), оскільки з часом вплив цих параметрів збільшується. При встановленні нульової вхідної напруги Uвх 0 через конденсатор буде протікати струм, зумовлений наявністю вказаних особливостей реальних операційних підсилювачів:

U

Ic R0 I B

Рис.5.10. Схема електрична принципова інтегруючої ланки на реальному ОП.

Внаслідок протікання струму буде змінюватись і вихідна напруга:

dU |

âèõ |

|

1 |

|

|

1 |

U |

0 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

IC |

|

|

|

I B |

|||

dt |

C |

C |

|

R |

||||||

|

|

|

|

|

|

|

|

|

|

|

При струмі Ів , що дорівнює, наприклад ,1мкА, вихідна напруга буде зростати на 1В кожної секунди, якщо С=1мкФ. З отриманого рівняння випливає, що при заданій величині постійного часу вхідний струм, при відсутності сигналу, буде тим меншим, чим більше значення ємності конденсатора використано в інтеграторі. Загалом, величина ємності конденсатора С не може бути вибрана як завгодно великою. Як правило, величину ємності конденсатора слід вибирати такою, щоб вплив Ів не перевищував U0. Для цього необхідно, щоб виконувалась умова

I |

|

|

U0 |

|

U0e |

. |

B |

|

|

||||

|

|

R |

|

|

||

Приймемо, що необхідно забезпечити постійну часу інтегрування рівну одній секунді з допомогою конденсатора ємністю 1 мкФ. При використанні операційного підсилювача, напруга зміщення якого не перевищуватиме 1мВ вхідний струм повинен бути не більше

I |

|

|

1ìêÔ 1ì |

1ìÀ . |

|

âõ |

1ñ |

||||

|

|

|

Операційний підсилювач з біполярними транзисторами на вході не в змозі забезпечити такий низький рівень струму при відсутності вхідного сигналу. В цьому випадку використовують метод компенсації цього струму рис.5.11..

34

Рис. 5.11. Схема електрична принципова інтегруючої ланкиp з компенсацією вхідного струму ОП.

Величина опору резистора R1 того ж порядку, що й величина опору R. Спад напруги на резисторі R1 дорівнює R1Ів. Якщо Uвх=0, то, оскільки U U , через R протікатиме струм

I |

U |

|

U |

|

|

|

||||

|

|

|

|

|

. |

|

|

|||

|

|

|

|

|

|

|

||||

|

|

|

R |

|

R |

|

|

|||

Оскільки R1=R, то |

|

|

|

|

|

|

|

|

|

|

I |

U |

|

R1I B |

I |

|

. |

||||

|

|

B |

||||||||

|

R1 |

|

|

|

R1 |

|

|

|

||

|

|

|

|

|

|

|

|

|||

При цьому струм через конденсатор буде дорівнювати нулю.

Змінюючи в певних межах величину опору резистора R1, можна також компенсувати зміщення нуля U0. Некомпенсованим залишається дрейф вхідних струмів, який для операційних підсилювачів на біполярних транзисторах може бути достатньо великим. З цієї точки зору слід надавати перевагу операційним підсилювачам із польовими транзисторами на вході, для яких вхідний струм при відсутності сигналу найбільш малий, що немає необхідності в компенсації.

Похибки інтегрування можуть бути зумовлені струмами витікання конденсатора оберненого зв'язку. В електролітичних конденсаторах ці струми складають приблизно одиниці мікроампер, тому їх використання в інтеграторах не припустиме. Як правило, для цих цілей використовують метало-паперові конденсатори, однак їх використання при ємностях більше 10 мкФ утруднене.

У деяких випадках виникає необхідність задавати на виході інтегратора певний фіксований рівень напруги, зупиняти роботу інтегратора при досягненні певного рівня. Такі функції можна отримати з допомогою додаткових елементів, введених до схеми.

Рис. 5.12. Схема електрична принципова інтегруючої ланки з можливістю задання на виході інтегратора довільного рівня напруги та зупинки процесу інтегрування при досягненні заданого рівня

вихідного сигналу.

Якщо у схемі ключ S2 розімкнуто, а S1 замкнутий, то ми отримуємо звичайний інтегратор напруги U1. Розімкнувши S1, для випадку ідеального інтегратора забезпечимо нульовий зарядний струм. При цьому вихідна напруга зафіксується на величині, що відповідатиме моменту вимкнення. Такий режим роботи інтегратора використовується в тому випадку, коли на виході інтегратора необхідно забезпечити постійне значення напруги. Для того, щоб забезпечити початковий рівень вихідного сигналу, слід розімкнути ключ S1 і замкнути S2. У цьому випадку схема працює як звичайний інтегруючий підсилювач з вихідною напругою

U вих U 2 RR3 .

2

Диференцююча ланка

35

Операцію диференціювання сигналу можна здійснити з допомогою електронної схеми, наведеної на рис. 5.13.

Рис. 5.13. Диференцююча ланка на ОП

Величину вхідного струму можна визначити як швидкість зміни заряду накопичення в конденсаторі

Iвх dQdt , де Q=CU.

Підставивши відповідні значення, отримаємо

Iвх C dUdt .

Отже,

Uвих U R R Iвх RC dUdt .

Розглянемо випадки:

а) якщо U = const, то Uвих = 0;

б) якщо U = U0 ∙ t, то Uвих = –RCU0, отже, вихідна напруга буде мати фіксований рівень;

в) якщо U = U0 ∙ sin t, то Uвих = –RCU0 ∙ cos t.

У даному випадку зростання частоти вхідного сигналу супроводжується зростанням амплітуди вихідного сигналу. Такий характер частотної залежності вихідного сигналу є характерною рисою диференцюючої ланки.

Перш ніж перейти до розгляду схем потенціювання та логарифмування розглянемо узагальнену ВАХ діода. В аналітичному вигляді вона може бути такою

|

|

|

|

|

U |

|

|

|

|

|

|

|

|

Ä |

|

|

|

|

|

|

U |

|

|

I |

|

I |

S |

e |

|

Ò 1 . |

|

|

Ä |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

У даному випадку UT – термічний потенціал, причому

UÒ m kTe ,

де

k – стала Больцмана;

Т – абсолютна температура Кельвіна; е – заряд електрона;

m – деякий параметр, величина якого змінюється від 1 до 2.

При 300ºК величина UТ ≈ 26 мВ. При UД > UТ струм, що протікає через діод, буде визначатись формулою

|

|

|

|

U Ä |

||

|

|

|

|

|

|

|

I |

Ä |

I |

S |

e UÒ , |

||

|

|

|

|

|

||

де

UД – спад напруги на діоді;

36

ІД – струм, що протікає через діод.

Схема потенціювання На рис. 5.14 наведена принципова електрична схема потенціювання.

Рис.5.14. Принципова електрична схема потенціювання аналогового сигналу.

Використовуємо принцип віртуального замикання, при цьому вхідний струм

|

|

|

|

|

|

|

|

|

U Ä |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

âõ |

I |

Ä |

I |

S |

e UÒ ; |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

U Ä |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

U |

âèõ |

U |

R |

R I |

âõ |

R I |

S |

e UÒ . |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

За принципом віртуального замикання UД = Uвх, отже,

|

|

|

|

U âõ |

||

|

|

|

|

|

|

|

U |

âèõ |

R I |

S |

e UÒ . |

||

|

|

|

|

|

||

Схема логарифмування

Якщо поміняти місцями резистор та діод тобто елементи R та VD схеми (рис.5.14), то ми отримаємо схему (рис.5.15) здійснення математичної операції логарифмування.

Рис.5.15. Принципова електрична схема логарифмування аналогового сигналу

Величина вхідного струму буде визначатись формулою

I |

|

|

Uâõ |

. |

âõ |

|

|||

|

|

R |

||

37

Щоб знайти спад напруги на діоді UД, потрібно виконати логарифмування виразу

U Ä

|

I Ä |

|

|

|

|

|

I Ä |

|

|

U Ä |

|

|

|

|

|

|

|

|

|

I Ä |

|

||||||||

|

e U Ê . Після логарифмування |

|

ln |

|

. Звідси U |

|

|

U |

|

|

ln |

. |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

Ä |

Ê |

|

||||||||||||||||||

|

I S |

|

|

|

|

|

I S |

|

UÒ |

|

|

|

|

|

|

I S |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

Оскільки Uвих = –Uд, то U |

|

U |

|

|

ln |

I Ä |

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

âèõ |

Ò |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

I S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Оскільки ІД = Івх – за принципом віртуального замикання, а I |

|

|

|

Uâõ |

|

, то |

||||||||||||||||||||||

|

âõ |

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

||

|

|

|

|

|

|

U |

|

|

U |

|

|

ln |

Uâõ |

. |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

âèõ |

Ò |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R I S |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Схема сумування (інвертуючий суматор)

Принципова електрична схема інвертуючого суматора наведена на рис.5.16.

|

|

|

I |

|

|

U1 |

... |

I |

|

|

U n |

, причому |

|

|

||||||||

|

|

|

1 |

R1 |

n |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Rn |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Iâõ I1 I2 |

... In ; |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U |

|

U |

2 |

|

|

U |

|

U |

|

R |

|

I |

|

|

|

R |

|

|

1 |

|

|

... |

||||||

âèõ |

R |

|

âõ |

|

R |

R |

|

|||||||||||||||

|

|

|

ÎÇ |

|

|

|

|

ÎÇ |

|

|

|

|

||||||||||

|

|

|

ÎÇ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

2 |

|

U n .

R n

Рис.5.16. Принципова електрична схема інвертуючого суматора.

Якщо вважати, що R1 = R2 = … =Rn = RОЗ, напруга на виході схеми буде визначатись наступною формулою: Uâèõ U1 U2 ... Un .

Якщо ж R1 = R2 = … =Rn = R, а RОЗ =R/n, то Uâèõ U1 U 2 ... U n 1n .

Отже, на виході схеми буде формуватись напруга, що дорівнює інвертуючому середньому арифметичному від n вхідних напруг. У зв‟язку з цим такі схеми прийнято називати схемами усереднення.

Не інвертуючий суматор

38

Рис.5.17. Принципова електрична схема не інвертуючого суматора двох аналогових сигналів.

Згідно з принципом віртуального замикання, напруги на інвертуючому та не інвертуючому входах рівні між собою:

|

|

|

|

U U U |

|

|

|

|

|

|

|

R1 |

|

; |

|||||||||

|

|

|

âèõ R |

R |

2 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|||||

|

|

|

|

|

|

|

I1 I2 0 ; |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

U U |

|

|

|

|

|||||||||

|

|

|

|

|

|

I1 |

|

|

1 |

|

|

|

|

|

|

; |

|

|

|

||||

|

|

|

|

|

|

|

|

|

R3 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

U |

2 |

U |

|

|

|

|

||||||||||

|

|

|

|

|

|

I 2 |

|

|

|

|

|

|

|

; |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

R4 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

отже, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U U |

|

U |

2 |

U |

|

|

|

|

||||||||||||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

0 ; |

|

|

||||

|

|

|

|

|

|

R3 |

|

|

|

R4 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

або |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

4 |

(U |

1 |

U ) R (U |

2 |

U ) |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

0 . |

||||||

|

|

|

|

|

|

R3 R4 |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

Даний вираз дорівнюватиме нулю, якщо:

R4 (U1 U ) R3 (U 2 U ) 0 ;

R4U1 R3U 2 U (R4 R3 ) .

Оскільки U U , то підставимо значення U :

R4U1 R3U 2 |

U âèõ |

|

|

R1 |

|

|

(R4 R3 ) . |

|||

R |

R |

2 |

|

|||||||

|

|

|

|

|

1 |

|

|

|

|

|

Приймемо, що R1=R2=R3=R4=R, тоді |

|

|

|

|

|

|

|

|

|

|

R(U U |

|

) U |

|

|

R |

|

2R . |

|||

|

âèõ 2R |

|||||||||

1 |

|

2 |

|

|

|

|||||

Отже,

Uâèõ U1 U2 .

Замість U підставимо в дане рівняння значення U отримаємо:

U |

|

|

R1 R2 |

|

R5 |

(U U |

|

) , |

âèõ |

|

|

2 |

|||||

|

|

R1 |

|

1 |

|

|||

|

|

|

|

R R5 |

|

|

||

при R1=R, R5=R2 й отримаємо

U |

|

|

R R5 |

|

R2 |

(U U |

|

) |

R2 |

(U U |

|

) . |

âèõ |

|

|

2 |

|

2 |

|||||||

|

|

R1 |

|

R R5 |

1 |

|

1 |

|

||||

|

|

|

|

|

|

|

R1 |

|

|

|||

Отже, вихідна напруга буде пропорційна сумі вхідних напруг при R1=R2. Тобто якщо коефіцієнт підсилення дорівнює одиниці,

Uâèõ U1 U2 .

39

У випадку аналогових ЕОМ операція множення виконується шляхом логарифмування відповідних величин, додаванням про логарифмованих відповідних величин і потенціювання результату сумування.

Рис. 5.18. Принципова електрична схема не інвертуючого суматора трьох аналогових сигналів

Оскільки |

U U , а |

|

|

I |

1 |

I |

2 |

I |

3 |

0 |

то |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

U |

1 |

U |

U |

2 |

U |

|

U |

3 |

U |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 ; |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

R3 |

|

|

R4 |

|

|

|

|

R5 |

|

|

|

|

|

Дане рівняння буде справедливим якщо після знаходження спільного знаменника і додавання дробів чисельник буде рівний нулеві

R4 R5 (U1 U ) R3R5 (U 2 U ) R3R4 (U3 U ) 0 ;

Розкриємо дужки і перенесемо доданки , що містять U в праву частину рівняння отримаємо

R4 R5U1 R3R5U 2 R3R4U3 U (R4 R5 R3R5 R3R4 ) .

Підставивши значення U , отримаємо

R4 R5U1 R3R5U 2 R3R4U3 U âèõ |

R1 |

|

|

(R4 R5 R3R5 R3R4 ) ; |

||||||||||

R R |

2 |

|||||||||||||

|

|

|

|

|

|

|

1 |

|

|

|

|

|

||

Приймемо, що R3=R4=R5=R. В цьому випадку рівняння матиме такий вигляд |

||||||||||||||

R 2 (U |

|

U |

|

U |

|

) U |

|

|

|

R1 |

|

3R 2 . |

||

1 |

2 |

3 |

âèõ R |

|

2 |

|||||||||

|

|

|

|

|

R |

|

||||||||

|

|

|

|

|

|

|

1 |

|

|

|

|

|||

Якщо R2=2R1, тоді |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U1 U2 |

U3 Uâèõ. |

|

|

|||||||||

Дане рівняння отримане при додаванні трьох різних напруг. Якщо кількість входів дорівнює n то формула матиме вигляд

n |

U âèõ |

|

R1 |

n . |

Ui |

|

|

||

R |

(n 1)R |

|||

i 1 |

1 |

1 |

|

|

Використовуючи схеми логарифмування, сумування та потенціювання, можна побудувати схеми помножувача напруг.

40

Рис.5.19. Схема електрична принципова множення двох аналогових сигналів.

У тому випадку якщо U1 U 2 , тобто на обидва входи подається дві однакові напруги, то вихідна напруга буде пропорційна квадрату вхідної. Введемо умовне позначення цієї схеми:

Рис.5.20. Умовне позначення схеми піднесення до квадрату аналогового сигналу.

Якщо схему, яка виконує операцію піднесення до квадрата, використати як ланку ОЗ, то ми отримаємо схему добування кореня квадратного:

Рис.5.21. Схема електрична принципова знаходження кореня квадратного аналогового сигналу.

Згідно з принципом віртуального замикання U U , у свою чергу

|

U |

|

|

|

|

|

|

|

|

U âèõ |

2 |

|

|||

U |

|

|

, а U |

|

|

, |

|||||||||

âõ |

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

||

|

|

|

|

|

U |

|

|

|

2 |

|

|

|

|

||

|

|

|

|

|

âèõ |

|

|

|

|

|

|

||||

отже, |

U âõ |

|

|

|

|

|

; |

|

|

||||||

|

|

A |

|

|

|

|

|||||||||

|

AU |

âõ |

U |

|

|

2 |

; |

|

|

||||||

|

|

|

|

|

|

âèõ |

|

|

|

|

|

||||

тому

41

U âèõ

AU âõ .

AU âõ .

Розглянуті схеми множення належать до схем одно квадрантного множення. Тобто обидві помножувані величини повинні бути додатної полярності. Існують схеми двох - і навіть чотирьох квадрантного помноження, але вони використовують дещо інші принципи і, що найбільш важливо, обмежені лише двома множниками, а в цьому випадку число множників практично не обмежене. З іншого боку, це відкриває можливість підносити не тільки до другого степеня, але й до третього, четвертого і т.д., якщо відповідні входи об'єднати. Отримавши схему піднесення до третього степеня, вмикаємо її в коло оберненого зв'язку операційного й отримуємо схему добування кубічного кореня.

5.3. Компаратори сигналів на операційних підсилювачах

Для визначення моменту рівності напруг двох сигналів використовуються схеми ввімкнення ОП в компараторному режимі, в якому використовуються як один вхід ОП, так і два. Петля ОЗ, як правило, не замикається.

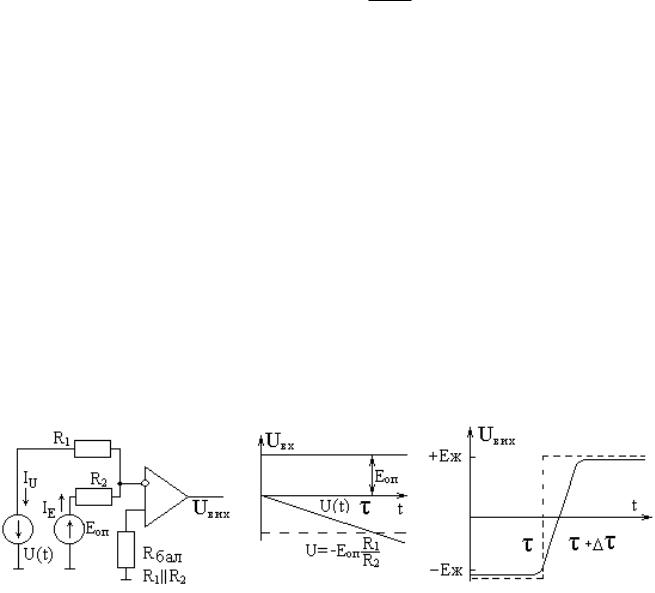

Одно вхідний компаратор сигналів. Компаратор такого типу рис.5.22 призначений для порівняння величини різнополярних вхідних напруг, причому в момент їх рівності за абсолютною величиною вихідна напруга компаратора змінюється на другий граничний стан. В схемі рис.5.22 Rбал– балансний резистор. Величина опору цього резистора рівна опору паралельно ввімкнених резисторів R1||R2. До моменту часу τ напруга U0(t) за модулем менша від Еоп тому вона й визначає полярність напруги на виході ОП. Оскільки в даному випадку Еоп>0, то Uвих ≈ Еж‾. Після досягнення вхідним сигналом U0(t) порогового значення –ЕопR1 ∕ R2 вихідна напруга визначається вхідним сигналом U0, при цьому Uвих = Еж+. У момент виконання рівності U0= ЕопR1 ∕ R2 підсилювач компаратора знаходиться в нестійкому стані.

а) б) в)

Рис.5.22 Одно вхідний компаратор сигналів: а) схема електрична принципова; б) осцилограми вхідних сигналів; в) осцилограма вихідного сигналу.

Нахил лінійно змінної частини вихідного сигналу компаратора визначається коефіцієнтом підсилення ОП. З метою збільшення швидкості перемикання, ОП у схемах компараторів використовується без ОЗ (без від'ємного ОЗ). . При зміні знаку різниці вхідних напруг вихідна напруга не може миттєво перейти із одного стану насичення в інший оскільки величина швидкості наростання вихідної напруги ОП. Перемикання проходить з деякою затримкою ∆τ, яка визначається часом перезарядки ємностей схеми ОП, а отже швидкодією ОП. Для ОП з посередніми технічними характеристиками швидкість наростання вихідної напруги становить близько1 В/мкс. В цьому випадку перехід від, наприклад, ─15 В до +15 В повинен тривати практично 30 мкс. Внаслідок скінченності часу встановлення ОП при його переході в із станів насичення, час перемикання компаратора збільшується не менше ніж в 10 разів.

Значно менші часи затримки забезпечуються при використанні спеціалізованих інтегральних компараторів. Вони також призначені для роботи без ОЗ і характеризуються особливо малими часами встановлення.

Одно вхідний компаратор має відносно низький опір, проте дозволяє порівнювати значні за амплітудою сигнали без похибок, зумовлених синфазною складовою. Амплітуда сигналів між входами ОП не повинна перевищувати припустимого рівня для диференційних сигналів. Водночас відносна точність порівняння сигналів тим більша, чим більша іх амплітуда.

Двох вхідний компаратор. Компаратор такого типу рис.5.23 порівнює електричні сигнали

42