4.2. Використання паралельних портів введення-виводу

Як відмічено в 3.8 портів Р0.Р3 можуть використовуватися:

Як 8-розрядні паралельні порти ввода/вывода інформації;

Як 32 однорозрядних лінії ввода/вывода;

При роботі із зовнішньою пам'яттю програм і даних;

У режимі альтернативних функцій (8 ліній порту Р3);

При програмуванні і перевірці РПП.

По сигналу ”RESET” в регістри-клямки всіх портів автоматично записуються одиниці, що набудовують все 32 лінії портів на введення інформації, а вісім ліній порту Р3, окрім цього, - на режим “альтернативних” функцій.

4.2.1. Особливості роботи порту Р0

На рисунку 11 приведена спрощена структурна схема i-го розряду порту Р0, що відображає його роботу в двох основних режимах:

Робота із зовнішньою пам'яттю програм або даних;

Робота портом ввода/вывода.

Рисунок 11 – Спрощена структурна схема порту Р0 (i-го виводу)

Залежно від виконуваних в даний час команд (робота з портами або з ВП) внутрішній сигнал «управління» набуває значення: 0 - Р0 використовується як порт ввода/вывода; 1 - порт використовується для роботи з ВП.

4.2.1.1. Особливості роботи Р0 з ВП (ВПП або ВПД)

Сигнал «управління» рівний 1. Мультиплексор МХ знаходиться у верхньому положенні. На вхід інвертора і один з входів конъюнктора поступає значення i-го розряду молодшого байта адреси ВП - 1/0. Після інвертора воно набуває значення 0/1. Оскільки на іншому вході конъюнктора присутня логічна 1, то вихідний сигнал конъюнктора повторює значення i-го розряду адреси - 1/0. Таким чином, на затворах транзисторів VT1 і VT2 присутньо дві протилежні комбінації логічних сигналів:

1 /0

на затворі VT1

/0

на затворі VT1

при значенні i-го біта адреси 1/0.

0/1 на затворі VT2

У схемі використані МОН-польові транзистори з каналом типа n. Якщо на затворі такого VT логічна 1, то транзистор – відкритий, а якщо логічний 0, то – закритий. Отже, якщо в i-м біті адреси видається логічна 1, то VT1 – відкритий, а VT2 – закритий, і з i-го виведення порту 0 знімається також 1. Якщо ж в i-м біті адреси присутній логічний 0, то VT1 – закритий, а VT2 – відкритий.

З виходу при цьому знімається логічний 0. Сказане можна представити наступною таблицею 18.

Таблиця 18

|

Значення i-го біта МБ адреси ВП (даних, що виводяться)

|

Сигнали на затворах транзисторів

|

Стан транзисторів

|

Значення вихідного сигналу

| ||

|

VT1

|

VT2

|

VT1

|

VT2

| ||

|

0 |

0 |

1 |

закритий

|

відкритий

|

0 |

|

1 |

1 |

0 |

відкритий

|

закритий

|

1 |

Виводи порту Р0 при роботі з ВП використовуються в режимі мультиплексування: спочатку видається МБ адреси ВП, а потім через виводи видаються або приймаються дані. Видаються при роботі з ВПД, а приймаються при роботі з ВПП або ВПД. Слід звернути увагу на те, що при читанні ВПП або ВПД на нижній транзистор VT2 апаратний автоматично подається логічний 0, VT закривається і не шунтує i-й виведення Р0, через яке відбувається читання пам'яті. Відзначимо також, що при виконанні команд роботи із зовнішньою пам'яттю в тригери-клямки порту Р0 автоматично записуються логічні 1.

4.2.1.2. Особливості роботи Р0 як порти ввода/вывода

Сигнал «управління» дорівнює нулю. МХ знаходиться в нижньому положенні. На затворі VT1 постійно присутній логічний 0, і він закритий.

4.2.1.2.1. Виведення даних через Р0

Через РШД внутрішнім сигналом «запис клямки» значення i-го біта, що виводиться, запам'ятовується в тригері-клямці. При виводі логічного 0 сигналом високого рівня, що знімається з виходу тригера-клямки, транзистор VT2 відкривається (VT1 закритий постійно), і з i-го виведення порту Р0 видається логічний 0. При виводі логічною 1 сигналом низького рівня, що знімається з виходу тригера-клямки, транзистор VT2 закривається (VT1 закритий постійно), і i-й виведення Р0 виявляється «обірваним» - знаходиться в z-состоянии. Тому для виводу логічною 1 через i-й вивід, коли Р0 працює як порт ввода/вывода, необхідно включати зовнішній «підтягуючий» резистор (стоку) і i-м виведенням порту Р0 (див. Рисунок 11).

4.2.1.2.2. Введення даних через Р0

При введенні даних відповідний тригер-клямка має бути встановлений в 1. Інакше (якщо він в 0) VT2 – відкритий і шунтує i-й вивід, тобто постійно вводитиметься логічний 0. Встановити тригери-клямки в 1 можна різними способами:

сигналом «RESET» автоматично у всі тригери-клямки записуються одиниці;

при виконанні команд, що працюють з ВП (ВПП чи і ВПД), автоматично в тригери-клямки записуються одиниці;

командами, що працюють з портом Р0 в цілому;

командами, що працюють з окремими бітами Р0.

При виконанні команд «введення» виробляється внутрішній сигнал «читання виводів», який через буфер В2 передає значення i-го виведення Р0 на РШД.

4.2.1.3. Спеціальний режим використання порту Р0:

режим «читання-модифікація-запис»

У цьому режимі порт Р0 працює в тих випадках, коли при виконанні команд порт є одночасно операндом і местомом призначення результату. При цьому інформація прочитується не із зовнішніх виводів, а з тригерів-клямок. Це відбувається при виробленні внутрішнього сигналу «читання клямки» через буфер В1. Усередині мікроконтроллера відбувається модифікація вмісту i-го тригера-клямки відповідно до виконуваної команди, а потім запис нового значення назад в тригер-клямку.

Якщо прочитувати інформацію не з тригерів-клямок, а із зовнішніх виводів, то можлива помилка. Наприклад, якщо одиничний вихідний сигнал управляє якимсь потужним виконавським елементом, то цей сигнал може падати по рівню і при читанні з виведення Р0, а не з клямок, може сприйматися як логічний 0 замість логічної 1.

4.2.2. Особливості роботи порту Р1

Порт Р1 не використовується при роботі із зовнішньою пам'яттю, тому на відміну від портів P0 і P2 є "чистим" портом введення-виводу.

Структура Р1 приведена в [1] і дуже схожа на розглянуту вище схему порту Р0 (Рисунок 11).

Порт Р1 містить 8 тригери-клямок, буфери введення-виводу, декілька МОН-ТРАНЗИСТОР, один з яких виконує функцію зовнішнього ("що підтягує") резистора Rc, групу додаткових логічних елементів для підвищення швидкодії.

Порт Р1 може використовуватися в режимі "читання – модифікація – запис", який описаний при розгляді порту Р0.

Окрім застосування як порт введення-виводу порт Р1 застосовується при програмуванні і перевірці РПП (див. розділ 6).

Кожна з восьми ліній порту Р1 може програмуватися незалежно один від одного на введення або виведення інформації.

4.2.3. Особливості роботи порту Р2

Структура порту Р2 приведена в [1] і виконана аналогічно схемам Р0, Р1. Окрім введення-виводу порт Р2 використовується для видачі старшого байта адреси при роботі із зовнішньою пам'яттю, тому його схема також як і Р0 містить мультиплексор. Порт Р2 бере участь в програмуванні і перевірці РПП, може використовуватися в режимі "читання – модифікація – запис", описаному вище (4.2.1.3). Кожна з восьми ліній порту Р2 може програмуватися незалежно один від одного на введення або виведення інформації.

4.2.4. Особливості роботи порту Р3

Спрощена структура i-го виведення (i = 0, 1, ., 7) порту Р3 приведена на рисунку 13.

Рисунок 13 - Спрощена структурна схема Р3 (i-го виводу)

Р3 може працювати як двонаправлений 8-розрядний порт введення-виведення інформації або виконувати альтернативні функції.

4.2.4.1. Робота Р3 в режимі "альтернативних функцій"

Р3 може виконувати три альтернативні функції виходу і п'ять альтернативних функцій входу.

4.2.4.1.1. Виконання портом Р3 альтернативних

функцій виходу

Порт Р3 може виконувати три альтернативні функції виходу. При цьому використовуються наступні його виводи:

Р3.1 (T?D) – вихід послідовного порту, призначений для виведення послідовних даних з передавача послідовного порту;

Р3.6 (WR) – вихід, з якого знімається сигнал, - строб запису у ВПД при ви полнении команд MOVX @Ri, A; MOVX @DPTR, A;

P3.7 (RD) – вихід, з якого знімається сигнал, - строб читання з ВПД при виконанні команд MOVX A @Ri; MOVX A @DPTR.

Аби одна з 3-х ліній Р3 могла виконувати названі функції, у відповідний тригер-клямку регістра порту має бути записана логічна 1, яка з одиничного виходу тригера подається на нижній вхід конъюнктора (Рисунок 13).

Якщо значення альтернативної функції виходу 0/1, то після елементу І-НЕ воно перетвориться в 1/0 і поступає на затвор МОН-ТРАНЗИСТОР з n-каналом. Якщо на вході транзистора одиниця, то він відкритий, а якщо нуль, то – закритий. Тобто з виходу транзистора і відповідного виходу порту знімається 0/1, рівний значенню альтернативної функції.

4.2.4.1.2. Виконання портом Р3 альтернативних

функцій входу

Порт Р3 може виконувати п'ять альтернативних функцій входу. При цьому використовуються наступні його виводи:

Р3.0 (R?D) – вхід послідовного порту, призначений для введення послідовних даних в приймач послідовного порту;

P3.2 (INT0) – використовується як вхід 0 зовнішнього запиту переривання;

P3.3 (INT1) – використовується як вхід 1 зовнішнього запиту переривання;

P3.4 (T0) – вхід лічильника зовнішніх подій T/CNT 0;

P3.5 (T0) – вхід лічильника зовнішніх подій T/CNT 1.

У схемах названих п'яти ліній порту Р3 сигнал "альтернативна функція виходу" набуває одиничного значення. У тригери-клямки має бути записана одиниця. Нульовим сигналом на затворі вихідний транзистор закритий і не шунтує вхід порту.

4.2.4.2. Робота Р3 портом виводу

У трьох розрядах порту Р3: Р3.1, Р3.6 і Р3.7, використовуваних як альтернативні функції виходу, внутрішній сигнал «альтернативна функція виходу» рівний 1, якщо в даний момент не виконується команда MOVX і немає видачі даних з передавача послідовного порту. У останніх п'яти розрядах Р3 названий сигнал постійно набуває одиничного значення. В цьому випадку сигналом на виході порту управляє відповідний тригер-клямка. Якщо тригер встановлений в 1, то Р3.i = 1, а якщо тригер знаходиться в 0, то Р3.i = 0.

4.2.4.3. Робота Р3 портом введення

В цьому випадку у відповідний тригер-клямку має бути записана 1, аби вихідний транзистор був закритий і не шунтував i-й виведення порту. Внутрішнім сигналом «читання виводів» (введення) через буфер В2 сигнал, що вводиться, передається на резидентну шину даних (РШД).

Аналогічно останнім портам Р3 може використовуватися в режимі «читання-модифікація-запис», який описаний при розгляді роботи порту Р0.

Слід підкреслити, що кожен біт порту Р3 може програмуватися незалежно один від одного і використовуватися як вхід, вихід або виконувати одну з альтернативних функцій.

4.3. Застосування послідовного порту

Послідовний порт ОЕОМ може використовуватися у вигляді регістра зрушення для розширення можливостей введення-виводу або як універсальний асинхронного приемопередатчика (УАПП) з фіксованою або змінною швидкістю послідовного обміну і можливістю дуплексного включення (тобто через послідовний порт можна приймати і передавати дані одночасно).

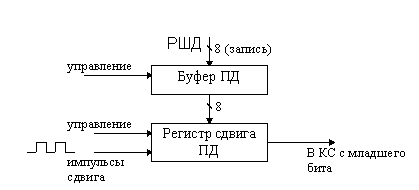

Послідовний порт містить наступні основні вузли (Рисунок 14): передавальний регістр зрушення; приймаючий регістр зрушення; буферний регістр приймача (SBUF), який містить буфер передавача (ПД) і буфер приймача (ПРМ).

Режим передачі:

Режим прийому:

Рисунок 14 - Спрощена структура послідовного порту

Послідовний порт працює в одному з двох режимів: передачі і прийому.

При передачі байт по резидентній шині даних (РШД) записується в буфер передавача. Імпульсами зрушення, які може формувати таймер-счетчик1 (див. розділ 4.1), дані в послідовному двійковому коді, починаючи з молодшого значущого розряду, передаються в канал зв'язку (КС).

При прийомі під дією імпульсів зрушення, які можуть бути сформовані в T/CNT 1, дані з каналу зв'язки в послідовному двійковому коді, починаючи з молодшого розряду, заповнюють регістр зрушення приймача. Після виконання необхідних перевірок прийнятий байт переписується в буфер приймача, звідки може бути прочитаний відповідною командою.

Отже, при передачі проводиться перетворення паралельного ДК в послідовний, а при прийомі – навпаки.

Послідовний порт може приймати черговий байт навіть якщо вже прийнятий до цього байт не був прочитаний з регістра приймача. Проте, якщо до закінчення прийому байт, що знаходиться в регістрі приймача, не буде прочитаний, прийнятий байт втрачається. Програмний доступ до регістрів приймача і передавача здійснюється зверненням до регістра спеціальних функцій SBUF. При записі в SBUF байт завантажується в регістр передавача, а при читанні SBUF байт читається з регістра приймача.

Прийом і видача байта даних починається з молодшого розряду і закінчується старшим розрядом. Для дозволу прийому необхідно встановити 1 в розряді REN регістра управління SCON (регістр SCON описаний в розділі 3.7).

Послідовний порт може бути запрограмований на один з чотирьох режимів приема/передачи шляхом програмування розрядів SM0 і SM1 регістра SCON. У всіх чотирьох режимах передача ініціюється будь-якою командою, яка використовує SBUF як регістра призначення (виконує операцію "Запис в SBUF"). Прийом в режимі 0 ініціюється одночасним виконанням умов REN = 1 і RI = 0 (REN і RI – розряди регістра управління SCON). У останніх режимах прийом ініціюється приходом старт-біта (нульовий рівень) при REN = 1.

4.3.1. Робота послідовного порту в режимі 0

У режимі 0 послідовний порт працює як восьмирозрядний регістр зрушення. При цьому 8 біт інформації в послідовному коді приймаються і передаються через двонаправлене виведення RXD. На виведенні TXD формується сигнал синхронізації зрушень.

Швидкість (частота) приема/передачи в режимі 0 постійна і складає fBQ/12, де fBQ – частота синхронізації ОЕОМ.

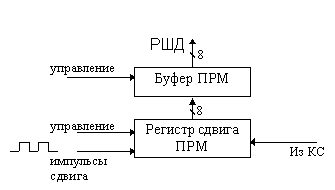

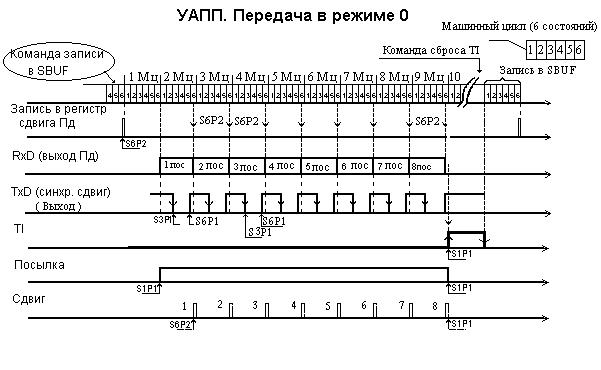

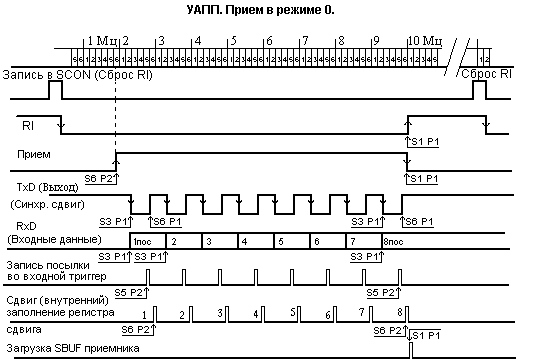

Тимчасові діаграми, що ілюструють роботу послідовного порту в режимі 0, показані на малюнках 15, 16. Всі змальовані на цих малюнках сигнали, за винятком RXD і TXD, є внутрішніми сигналами ОЕОМ.

Рисунок 15 - Передача в режимі 0

Рисунок 16 - Прийом в режимі 0

4.3.1.1. Передача в режимі 0

Передача починається будь-якою командою, яка використовує SBUF як регістра призначення (виконує операцію "запис в SBUF") (Рисунок 15).

При виконанні такої команди у фазі S6P2 виробляється внутрішній імпульс ЗАПИС В SBUF, по якому призначений до передачі байт записується в регістр зрушення передавача і запускається блок управління передачею. Внутрішня система того, що тактує ОЕОМ організована так, що між сигналом ЗАПИС В SBUF і початку передачі проходит один повний машинний цикл, після чого виробляється внутрішній сигнал ПОСИЛКА, що вирішує видачу вмісту регістра зрушення передавача на вихід RXD (виведення Р3.0 ОЕОМ) і імпульсів синхронізації зрушення (СИНХР ЗРУШЕННЯ на рисунку 15) на вихід TXD (виведення Р3.1 ОЕОМ). Сигнал СИНХР СДВІГ має низький рівень в поляганнях S3, S4 і S5 кожного машинного циклу і високий рівень в станах S6, S1 і S2. У фазі S6P2 кожного машинного циклу, в якому сигнал ПОСИЛКА активний, формується внутрішній імпульс ЗРУШЕННЯ, по якому вміст регістра зрушення передавача зрушується на одну позицію і на виході RXD виставляється черговий біт передаваної посилки. Всього формується вісім імпульсів ЗРУШЕННЯ, після чого блок управління передачею знімає сигнал ПОСИЛКА і встановлює прапор переривання передавача TI (розряд в регістрі SCON). Обоє ці дії виконуються у фазі S1P1 10-го машинного циклу після сигналу ЗАПИС В SBUF. По перериванню (TI = 1) уривається основна програма, викликається підпрограма, яка скидає прапор TI і записує черговий передаваний байт в SBUF

4.3.1.2. Прийом в режимі 0

Прийом починається при одночасному виконанням двох умов: REN = 1 і RI = 0 (Рисунок 16). У фазі S6P2 наступного машинного циклу блок управління прийомом виробляє внутрішній сигнал ПРИЙОМ, що вирішує видачу імпульсів СИНХР СДВІГ на вихід ОЕОМ TXD. Імпульси СИНХР СДВІГ міняють своє полягання у фазах S3P1 і S6P1 і синхронізують моменти вступу посилок на вхід ПРМ. Біти посилок, що приймаються, через вхід RXD поступають на регістр зрушення приймача. Стан входу RXD опитується у фазі S5P2. У фазі S6P2 кожного машинного циклу, в якому сигнал ПРИЙОМ активний, формується внутрішній імпульс ЗРУШЕННЯ і вміст регістра зрушення приймача зрушується вліво на одну позицію. Значення, яке при цьому записується в його крайній правий розряд, є значенням сигналу на вході RXD, отриманим у фазі S5P2 цього ж машинного циклу. Всього формується вісім імпульсів ЗРУШЕННЯ, після чого блок управління прийомом формує сигнал завантаження вмісту регістра зрушення приймача в SBUF. У фазі S1P1 10-го машинного циклу після запису в SCON, RI, що скинула, в 0, сигнал ПРИЙОМ скидається і встановлюється прапор переривання приймача RI (біт в регістрі SCON). Далі по RI = 1 виконується переривання основної програми, викликається підпрограма, яка скидає прапор RI і читає прийнятий байт з буфера ПРМ.

4.3.2. Робота послідовного порту в режимі 1

У режимі 1 прием/передача даних здійснюється у форматі восьмирозрядного УАПП. Через TXD передаються, а через RXD приймаються 10 біт: старт-біт (0), 8 біт даних і стоп-біт (1). При прийомі стоп-біт заноситься в біт RB8 регістра SCON. Швидкість (частота) приема/передачи визначається частотою переповнювань таймера / лічильника 1 FOV T/C1. Ця частота усередині УАПП проходить перетворення за схемою, приведеною на рисунку 17.

Рисунок 17 - Схема формування синхрочастот передачі і прийому усередині МК51 для

послідовного порту, що працює в режимах 1,3

Залежно від значення біта SMOD регістра PCON частота, що поступає на вхід дільників на 16, F’OV T/C1 = FOV T/CNT1 при SMOD = 1 і при SMOD = 0. На виходах дільників на 16 формуються частоти синхронізації передавача fСИНХР.ПД і приймача fСИНХР.ПРМ. На виходах 7, 8, 9 дільника на 16, формуючого fСИНХР.ПРМ, виробляються 3 коротких імпульсу, коли на вхід лічильника-дільника поступають відповідно 7-, 8- і 9-й імпульси частоти F’OV T/C1, починаючи з початку циклу рахунку. Ці імпульси використовуються логічною схемою ідентифікації значення чергової прийнятої посилки (0/1) за мажоритарним принципом.

4.3.2.1. Передача в режимі 1

Передача ініціюється будь-якою командою, використовуючою SBUF як регістр призначення, в який проводиться запис. Внутрішній імпульс ОЕОМ, що виробляється при цьому, ЗАПИС В SBUF завантажує призначений до передачі байт в молодших 8 розрядів регістра зрушення передавача і ініціює початок роботи блоку управління передачею (Рисунок 18).

Рисунок 18 - Передача в режимі 1

У режимі 1 регістр зрушення передавача має 9 розрядів і в його 9-й розряд по імпульсу ЗАПИС В SBUF заноситься "1" (стоп-біт).

Реально передача починається у фазі S1P1 машинного циклу, наступного за найближчим після ЗАПИС В SBUF переповнюванням дільника на 16 в ланцюзі сигналу fСИНХР.ПД (Рисунок 16). Таким чином, початок передачі синхронизовано дільником на 16, а не імпульсом ЗАПИС В SBUF. Період сигналу fСИНХР.ПД (синхронізація передачі) визначає час, протягом якого видаваний біт присутній на виході TXD (час передачі біта).

Передача починається установкою активного рівня внутрішнього сигналу ОЕОМ ПОСИЛКА, поява якого викликає видачу на вихід TXD рівня старт-біта (нуль). Після цього через час передачі одного біта стає активним внутрішній сигнал ОЕОМ ДАНІ, який вирішує видачу вмісту регістра зрушення передавача на вихід TXD (виведення Р3.0 ОЕОМ). При появі активного сигналу ДАНІ старт-біт на виході TXD змінявся бітом D0 регістра зрушення передавача. Після закінчення часу передачі біта D0 формується перший внутрішній імпульс ОЕОМ ЗРУШЕННЯ, по якому вміст регістра зрушення передавача зрушується на один розряд, і біт D0 на виході TXD замінюється бітом D1. Всього формується 9 імпульсів ЗРУШЕННЯ, внаслідок чого на вихід TXD видаються 8 біт даних і стоп-біт. Після закінчення видачі всіх біт посилки блок управління передачею встановлює, як показано на рисунку 18, прапор переривання передавача TI і знімає сигнали ПОСИЛКА і ДАНІ. По перериванню відбувається скидання прапора TI, запис нового байта і так далі

4.3.2.2. Прийом в режимі 1

Прийом починається при виявленні переходу сигналу на вході RXD з "1" в "0". Для відстежування такого переходу вхід RXD апаратний опитується з частотою F’OV T/C1 (Рисунок 17).

Коли перехід сигналу на вході RXD з "1" в "0" виявлений, негайно скидається лічильник-дільник на 16 в ланцюзі сигналу fСИНХР.ПРМ (Рисунок 19), внаслідок чого відбувається поєднання моментів переповнювання цього лічильника-дільника (імпульси fСИНХР.ПРМ на рисунку 19) з кордонами зміни бітів посилки, що приймається, на вході RXD.

Рисунок 19 - Прийом в режимі 1

Шістнадцять станів лічильника-дільника ділять час, протягом якого кожен біт посилки, що приймається, присутній на вході RXD, на 16 фаз, з 1-ою по 16-у для кожного біта. У фазах 7, 8 і 9 спеціальний пристрій ОЕОМ, біт-детектор, прочитує з входу RXD 3 значення біта, що приймається, за мажоритарним принципом "2 з 3-х" вибирає з них одне і подає його на вхід регістра зрушення приймача. Блок управління прийомом при цьому формує внутрішній імпульс ОЕОМ ЗРУШЕННЯ, внаслідок чого вміст регістра зрушення приймача зрушується на один розряд і прийнятий біт заноситься в регістр зрушення приймача. Всього формується 10 імпульсів ЗРУШЕННЯ, а регістр зрушення приймача в режимі 1 є 9-розрядним. Тому після 10-го імпульсу ЗРУШЕННЯ в регістрі зрушення приймача знаходяться біти даних D0—D7 і стоп-біт. Після 10-го імпульсу ЗРУШЕННЯ блок управління прийомом завантажує дані з регістра зрушення приймача в SBUF, завантажує стоп-біт з регістра зрушення приймача в розряд RB8 регістра SCON і встановлює прапор переривання приймача RI. Сигнал завантаження SBUF, RB8 і установки RI виробляється блоком управління прийомом лише в тому випадку, якщо у момент генерації останнього імпульсу ЗРУШЕННЯ виконуються наступні умови:

1. RI= 0 і

2. Або SM2 = 0, або прийнятий стоп-біт рівний "1".

Якщо хоч би одна з цих умов не виконується, прийнята посилка безповоротно втрачається, а прапор RI не встановлюється. Якщо обоє приведеної умови виконано, стоп-біт поступає в RB8, вісім біт даних поступають в SBUF і встановлюється прапор RI. В цей же час, незалежно від виконання приведених вище умов, послідовний порт знов починає відстежування переходу сигналу з "1" в "0" на вході RXD і прийом нового байта. До закінчення цього процесу попередній байт має бути прочитаний з буфера ПРМ, інакше буде накладення нового прийнятого байта на старий.

Якщо мажоритарний відбір при прийомі першого біта посилки (старт-біт) показує ненульове значення біта, всі пристрої блоку прийому скидаються, і починається відстежування

наступного переходу сигналу з "1" в "0" на вході RXD. Таким чином, забезпечується захист від помилкових старт-бітів.

4.3.3. Робота послідовного порту в режимах 2 і 3

Режими 2 і 3 — це режими 9-розрядного УАПП з постійною (режим 2) і змінною (режим 3) швидкістю обміну. У цих режимах 11 біт передаються / приймаються відповідно через виводи TXD / RXD в наступній послідовності: старт-біт, 9 біт даних, стоп-біт. 9-й біт даних при передачі визначається вмістом розряду ТВ8 регістра SCON. При прийомі 9-й біт даних заноситься в біт RB8 регістра SCON.

Швидкість (частота) прийому / передачі в режимі 2 (Рисунок 20) програмно налаштовується на одну з двох можливих величин: fBQ/32 і fBQ/64, де fBQ – частота синхронізації ОЕОМ.

Рисунок 20 - Схема формування синхрочастот передачі і прийому усередині МК51 для

послідовного порту, що працює в режимі 2

У режимі 3 швидкість (частота) прийому / передачі визначається частотою переповнювань Таймера / Лічильника 1 FOV T/CNT1 (Рисунок 17).

Відмінність в швидкості (частоті) прийому / передачі є єдиною відмінністю між режимом 2 і режимом 3. У всьому іншому ці два режими повністю ідентичні.

Тимчасові діаграми, що ілюструють роботу послідовного порту в режимах 2 і 3, приведені в [1, 2].

Робота УАПП в режимах 2 і 3 дуже схожа на режим 1. Але при цьому є ряд відмінностей:

У форматі обмінюваних даних. Після восьми інформаційних перед стоп-бітом присутній програмований 9-й біт. При передачі значення 9-го біта визначається значенням розряду TB8 регістра SCON. При прийомі 9-й біт фіксується в розряді RB8 регістра SCON.

Якщо біт SM2 регістра SCON встановлений в одиницю, то повідомлення, в якому 9-й біт дорівнює нулю, бракується (втрачається). Тобто прапор RI не встановлюється, і переривання основної програми при прийомі не відбувається.

На тимчасових діаграмах роботи передавача в режимах 2 і 3 в порівнянні з режимом 1 додасться ще один біт (TB8) і цикл передачі подовжується на один такт (період частоти синхронізації передавача).

На тимчасових діаграмах роботи приймача в режимах 2, 3 додасться ще один біт (RB8), що приймається, перед стоп-бітом. Крім того, детектування стоп-біта не відбувається, і прапор RI встановлюється після 10-го зрушення, тобто після фіксації RB8.

4.3.4. Швидкість передачі-прийому даних через

послідовний порт

Швидкість (частота пересилки бітів) послідовного обміну Vпд залежно від режиму роботи послідовного порту визначається або частотою синхронізації ОЕОМ fBQ (режими 0 і 2), або частотою переповнювання Таймера / Лічильника 1 Fov (режими 1 і 3).

У режимі 0 швидкість послідовного обміну максимальна. Вона постійна і складає:

Vпд =fBQ/12 [бит/с]. (3)

При необхідності працювати із змінною швидкістю використовується режим 2 послідовні порти. У цьому режимі швидкість послідовної передачі залежить від стану біта SMOD регістра SCON і частоти fBQ:

Vпд = (2SMOD/64) * fBQ [бит/с]. (4)

Т. е. при SMOD = 0 Vпд = fBQ/64, а при SMOD = 1 Vпд = fBQ/32. По сигналу “скидання” біт SMOD встановлюється в нуль. Для установки біта SMOD використовуються команди з байтовою адресацією, наприклад, команда MOV 87H, #80Н.

У режимах 1, 3 також є можливість змінити швидкість послідовної передачі:

Vпд = (2SMOD/32) * FOV T/C1 [бит/с] (5)

де FOV T/C1 – частота переповнювань Т/С 1.

Для використання Т/С 1 як джерело для завдання швидкості обміну необхідно:

1) заборонити переривання від Т/С 1;

2) запрограмувати працю Т/С 1 таймером або як лічильник, встановивши при цьому для нього один з режимів 0, 1 або 2;

3) запустити Т/С 1 на рахунок.

Зазвичай для синхронізації послідовного порту таймер Т/С 1 включається в режим автозавантаження (режим 2).

В цьому випадку швидкість послідовного обміну визначається по формулі:

Vпд = (2SMOD * fBQ)/(32 * 12 * [256-(TH1)]) [бит/с], (6)

де (ТН1) – десятковий код вмісту ТН1. Якщо необхідний последовательный обмін з дуже низькою швидкістю, то можна використовувати Т/С 1 в режимі 16-розрядного таймера (режим 1), вирішивши при цьому переривання від Т/С 1 з метою перезавантаження TL1/TH1 в підпрограмі обслуговування переривання.

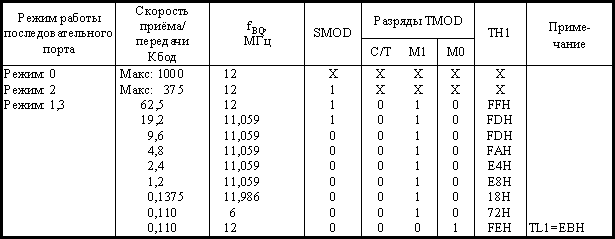

У таблиці 19 приведений ряд стандартних швидкостей послідовного обміну і те, як вони можуть бути реалізовані в ОЕОМ.

Таблиця 19 - Формування стандартних швидкостей обміну по послідовному порту

У таблиці 20 приведена звідна інформація по всіх чотирьох режимах роботи послідовного порту ОЕОМ сімейства МК51.

Таблиця 20 - Звідна інформація по всіх режимах роботи послідовного порту

4.3.5. Приклад програмування послідовного порту ОЕОМ

Вихідні дані для програмування:

Швидкість обміну – 110 бит/с (бод);

fBQ= 6 Мгц;

Режим роботи послідовного порту - 3;

Режим роботи T/C1 – 2;

Вигляд обміну – під управлінням мікропроцесора (програмно-керований);

Біт SMOD регістра PCON сигналом "RESET" встановлений в 0.

Нижче наведений приклад програми ініціалізації послідовного порту і фрагменти програмно-керованого обміну:

; ініціалізація послідовного порту

; для роботи із швидкістю 110 бод на

; частоті тактового сигналу 6 Мгц;

INT1:CLRTCON.6 ; останов таймера;

CLRIE.3 ; заборона переривань відT/C1;

CLRIE.4 ; заборона переривань від УАПП;

MOVTH1,#72H; автозавантажуване значення для здобуття

; швидкості 110 бод;

MOVSCON,#11011000B; установка режиму 9-розрядного УАПП;

MOVTMOD,#00100000B; установка режиму автозавантаження таймера 1;

SETBTCON.6 ; запуск таймера1;

; прийом символу від зовнішнього пристрою;

CIN:JNBRI,CIN; чекання завершення прийому;

MOVA,SBUF; читання отриманого символу;

CLRRI; очищення прапора прийому;

; передача символу на зовнішній пристрій;

COUT:JNBTI,COUT; чекання закінчення передачі попереднього

; символу;

CLRTI; очищення прапора передачі;

MOVSBUF,A; видача символу.

4.3.6. Особливості межконтроллерного обміну інформацією в

локальних мережах, що управляють

Режим 2 і режим 3 послідовні порти дозволяють організувати роботу ОЕОМ в багатопроцесорних системах, що використовують для обміну інформацією між ОЕОМ моноканал, що розділяється (коаксіальний кабель, вита пара, оптоволокно) [2]. У цих режимах приймається дев'ять біт даних і 9-й прийнятий біт записується в біт RB8 регістра SCON. При цьому, якщо біт SM2 регістра SCON встановлений в "1", то після прийому останньої посилки прапор переривання приймача RI буде встановлений лише в тому випадку, якщо RB8 = 1. Цю особливість роботи послідовного порту в режимах 2 і 3 можна використовувати для організації межконтроллерного обміну таким чином.

Коли ведуча ОЕОМ хоче передати блок даних однієї з ведених ОЕОМ, вона видає в моноканал посилку з адресою веденою, якою буде переданий блок даних. Адресна посилка відрізняється від посилки з даними тим, що в адресній посилці 9-й біт даних рівний "1", а в посилці з даними – "0". Таким чином, при SM2 = 1 жодна ведена ОЕОМ не реагуватиме на посилку з даними, але всі ведені зреагують на адресну посилку. Проаналізувавши отриману адресу, ОЕОМ, що адресується, скидає свій біт SM2, а останні залишають його без зміни і знов переходять до виконання перерваної програми. Після цього ведуча ОЕОМ може починати видачу в моноканал блоку даних, на посилки якого реагуватиме лише ОЕОМ, в якої SM2 = 0.

Біт SM2 ніяк не бере участь в роботі послідовного порту в режимі 0. У режимі 1 біт SM2 може використовуватися для контролю правильності прийнятого стоп-біта: у режимі 1, якщо SM2 = 1, прапор переривання приймача RI не буде встановлений, якщо прийнятий стоп-біт не рівний "1".

4.4. Особливості структури переривань

Механізм переривань в ОЕОМ дозволяє автоматично реагувати на зовнішніх і на внутрішні події (переповнювання таймеров/счетчиков; завершення послідовного обміну). Алгоритм обробки переривання при виявленні запиту переривання представлений на рисунку 21. На рисунку 22 змальовані всі можливі джерела переривання і порядок їх обробки.

Рисунок 21 - Схема алгоритму обробки переривання

Кожне із зовнішніх переривань може бути активізоване по рівню ("0") або по фронту (перехід з "1" в "0") сигналів на виводах ОЕОМ Р3.2, Р3.3, що визначається станом бітів IT0 і IT1 регістра TCON. Під час вступу запиту зовнішнього переривання (х=0,1) встановлюється прапор IЕх (х=0,1) регістра TCON. Установка прапорів IЕх в регістрі TCON викликає відповідне переривання. Очищення прапора IЕх проводиться таким чином: при перериванні по фронту IЕх скидається апаратний (автоматично внутрішніми засобами ОЕОМ) при зверненні до відповідної підпрограми обробки переривання; при перериванні по нульовому рівню прапор очищається при знятті запиту зовнішнього переривання, тобто в IЕх відстежується стан виводу .

Аби зовнішнє переривання по рівню було розпізнане, необхідне, аби низький рівень на виводі стримувався в перебіг не менше 12 періодів сигналу тактової частоти ОЕОМ. Це пояснюється тим, що перевірка виводів ОЕОМ виконується внутрішніми апаратними засобами ОЕОМ один раз в кожному машинному циклі. В разі зовнішнього переривання по фронту прапор IЕх буде встановлений, якщо дві послідовні перевірки входу покажуть в одному машинному циклі "1", а в наступному "0". Тому, якщо зовнішнє переривання активізується по переходу із стану високого рівня в стан низького рівня, то мінімум одному машинному циклу низького рівня повинен передувати мінімум один машинний цикл високого рівня на виводі . Якщо зовнішнє переривання активізується по рівню, запит повинен стримуватися до початку обслуговуючої підпрограми і зніматися до завершення цієї підпрограми для запобігання повторному обслуговуванню.

Переривання від таймеров/счетчиков викликаються установкою прапорів TF0 і TF1 регістра TCON, які встановлюються при переповнюванні відповідних регістрів таймеров/счетчиков (за винятком режиму 3, див. розділ 4.1.4). Очищення прапорів TF0 і TF1 проводиться внутрішньою апаратурою ОЕОМ при переході до підпрограми обслуговування переривання.

Переривання від послідовного порту викликається установкою прапора переривання приймача RI або прапора переривання передавача TI в регістрі SCON. На відміну від всіх останніх прапорів, RI і TI скидаються лише програмною дорогою зазвичай в межах підпрограми обробки переривання, де визначається, якому з прапорів RI або TI відповідає переривання.

Кожне з перерахованих джерел переривань може бути індивідуально дозволений або заборонений установкою або скиданням відповідного біта в регістрі дозволу переривань IE. Регістр IE містить також біт ЕА, скидання якого в "0" забороняє відразу всі переривання. Необхідною умовою переривання є його дозвіл в регістрі IE. Формат і опис регістра дозволу прерываний приведені в розділі 3.5.

Всі біти, які викликають переривання (IE0, IE1, TF0, TF1, RI, TI), можуть бути програмно встановлені або скинуті з тим же результатом, що і в разі їх апаратної установки або скидання. Т. е. переривання можуть програмно вызываться або чекаючі обслуговування переривання можуть програмно ликвидироваться. Крім того, переривання по можуть викликатися програмною установкою Р3.2 = 0 і Р3.3 = 0, як показано в наведеному нижче прикладі:

MAIN:MOVIE# 00000101B; дозвіл переривання від .

MOVIP# 04H; привласнення старшого пріоритету.

SETBEA; загальний дозвіл переривання.

MOVP3; # 11110011В ; імітація зовнішніх переривань.

SUBR:ORG013H; перехід до підпрограми обслуговування .

У запропонованому прикладі запити переривання і, що мають різний пріоритет, поступають одночасно. При цьому обслуговується переривання з вищим пріоритетом.

У разі, коли переривання по (x = 0, 1) викликається рівнем сигналу на відповідному вході ОЕОМ, прапор IЕх (х = 0, 1) при переході до підпрограми обробки переривання автоматично скидається, а потім, якщо відповідне виведення ОЕОМ Р3.2 або Р3.3 все ще знаходиться в стані логічного "0", знов встановлюється. Тому, у разі, коли переривання по входах викликається рівнем, програмна установка в "1" прапорів IE0, IE1 викличе переривання, після чого відповідний прапор IЕх (х = 0, 1) буде автоматично скинутий при переході до підпрограми обробки переривання.

Прапори IE0, IE1, TF0, TF1, RI, TI встановлюються незалежно від того дозволено чи ні відповідне переривання в регістрі IE.

Структура пріоритетів переривань є двоступінчатою. Кожному джерелу переривання може бути індивідуально привласнений один з двох рівнів пріоритету: високий або низький. Виконується це установкою (високий рівень пріоритету) або скиданням (низький рівень пріоритету) відповідного біта в регістрі пріоритетів переривань IP (описаний в розділі 3.5). Програма обробки переривання з низьким рівнем пріоритету може бути перервана запитом переривання з високим рівнем пріоритету, але не може бути перервана іншим запитом переривання з низьким рівнем пріоритету. Програма обробки переривання з високим рівнем пріоритету не може бути перервана жодним іншим запитом переривання ні від одного з джерел. Якщо два запити з різними рівнями пріоритету прийнято одночасно, спочатку буде обслужений запит з високим рівнем пріоритету. Якщо одночасно прийняті запити з однаковим рівнем пріоритету, обробка їх проводитиметься в порядку, що задається послідовністю внутрішнього опиту прапорів переривань. Таким чином, в межах одного пріоритетного рівня існує ще одна структура пріоритетів:

|

Джерело

|

Пріоритет усередині рівня

|

|

1. IE0

|

(вищий)

|

|

2. TF0

|

|

|

3. IE1

|

|

|

4. TF1

|

|

|

5. RI + TI

|

(нижчий)

|

Необхідно особливо підкреслити, що структура "Пріоритет усередині рівня" працює лише в тих випадках, коли визначається послідовність обслуговування запитів на переривання, які прийняті одночасно і при цьому мають однаковий рівень пріоритету.

Спрощена схема системи переривань ОЕОМ приведена на рисунку 22.

Рисунок 22 - Спрощена схема системи переривань

Обробка переривань і час відгуку. Рівні на виводах і інвертуються і замикаються в прапори переривання IE0 і IE1 у фазі S5P2 кожного машинного циклу. У фазі S5P2 встановлюються прапори переривань послідовного порту RI і TI. Прапори TF0 і TF1 таймеров/счетчиков встановлюються у фазі S5P2 машинного циклу, в якому відбувається переповнювання Т/С. Аналіз (опит) прапорів виконується внутрішніми засобами ОЕОМ в наступному після установки (замикання) прапорів машинному циклі (цикл опиту прапора). І лише після виконання останнього циклу поточної команди проводиться апаратний виклик відповідної підпрограми обслуговування, еквівалентний команді LCALL [1].

Команда LCALL, що апаратний-реалізовується, завантажує вміст лічильника команд РС в стек (при цьому PSW в стек не записується), після чого записує в РС адресу відповідної підпрограми обробки переривання:

|

Джерело переривання

|

Адреса підпрограми (вектор переривання)

|

|

IE0

|

0003 Н

|

|

TF0

|

000У Н

|

|

IE1

|

0013 Н

|

|

TF1

|

001У Н

|

|

TI + RI

|

0023 Н

|

При виконанні команди LCALL, що апаратний-реалізовується, у вічко стека з молодшою адресою завантажуються розряди 0 – 7 лічильника команд, а в наступне вічко стека – розряди 8 – 15 лічильника команд.

Підпрограма обслуговування переривання триває до виконання команди RETI. Команда RETI відновлює стан логіки переривання і завантажує в лічильник команд РС 2 байти адреси повернення з двох верхніх вічок стека. Відновлення стану логіки переривання полягає в наступному: при переході по вектору на підпрограму обробки переривання автоматично до виконання команди RETI незалежно від стану біт регістра IE забороняються всі переривань з рівнем пріоритету, рівним рівню пріоритету обслуговуваного переривання, тобто вкладені переривання з рівними рівнями пріоритету неможливі. Команда RETI знімає цю заборону. При використанні команди RET відновлюється лише стан лічильника команд, тобто відбувається повернення в перервану програму. Стан логіки переривання команда RET не міняє, тобто логіка управління обслуговуванням переривань як і раніше вважає, що продовжує обслуговуватися переривання, підпрограма обробки якого була закінчена командою RET.

4.5. Організація покрокового режиму роботи

Організація покрокового режиму роботи в ОЕОМ сімейства МК51 може бути реалізована з використанням особливостей системи переривання при дуже невеликих витратах в плані додаткового програмного забезпечення. Як вже наголошувалося, при переході по вектору на підпрограму обробки переривання автоматично до виконання команди RETI забороняються всі переривання з рівнем пріоритету, рівним рівню пріоритету обслуговуваного переривання. Після виконання команди RETI обов'язково буде виконаний мінімум одна команда перерваної програми, після чого можливий наступний перехід на обробку переривання. Використовувати цю особливість для організації покрокового режиму можна таким чином:

— запрограмувати одне із зовнішніх переривань (наприклад ) на активізацію по рівню;

— закінчити підпрограму обробки переривання наступною послідовністю команд:

LABEL1:JNBP3.2,LABEL1 ; чекання "1" на вході Р3.2 ( )

LABEL2:JBP3.2,LABEL2 ; чекання "0" на вході Р3.2 ( )

RETI ; повернення і виконання однієї команди

— задати на вході Р3.2 ( ) постійний рівень "0" з можливістю подачі одиничних імпульсів, наприклад, за допомогою кнопки "КРОКУ".

Після того, як вказані маніпуляції виконані, відбуватиметься наступне: виконається одна команда основної програми, після чого управління буде передано підпрограмі обробки переривання по, яка не зможе завершитися до тих пір, поки на вході не буде зафіксований імпульс "0"—"1"—"0". Після проходження такого імпульсу, що задається кнопкою "КРОКОМ" виконається команда RETI, управління повернеться в основну програму, де буде виконана одна команда, після чого знов почне оброблятися переривання по . Таким чином, одне натиснення кнопки "КРОКУ" (один імпульс "0"—"1"—"0" на вході ) викликає виконання однієї команди основної програми.

4.6. Організація пам'яті

Всі ОЕОМ сімейства МК51 мають декілька адресних просторів, функціонально і логічно розділених за рахунок різниці в механізмах адресації і сигналах управління записом і читанням:

— пам'ять програм;

— внутрішня пам'ять даних;

— зовнішня пам'ять даних.

Структура адресного простору ОЕОМ показана на рисунку 23. Зліва наводяться адреси відповідних областей пам'яті.

Рисунок 23 - Простір пам'яті ОЕОМ

Пам'ять програм (ПП) має 16-бітову адресну шину.

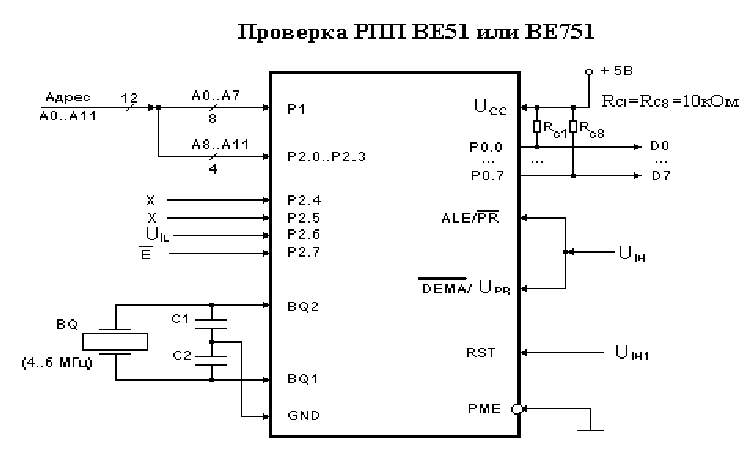

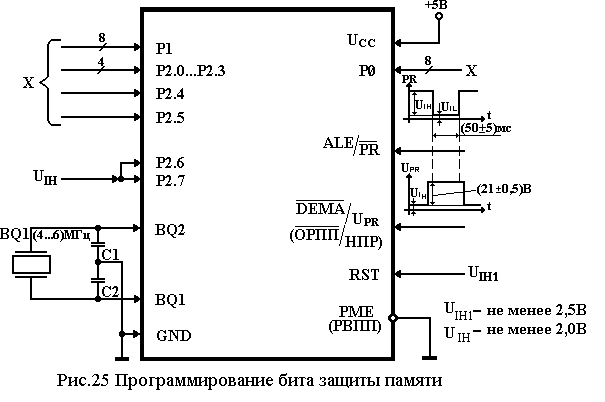

ПП доступна лише по читанню. ОЕОМ не мають команд і сигналів, що управляють, призначених для запису в пам'ять програм. Пам'ять програм має байтову організацію і загальний об'єм до 64 Кбайт. Ряд ОЕОМ (КР1816ВЕ51, КМ1816ВЕ751, КР1830ВЕ51) містять розташовану на кристалі внутрішню пам'ять програм ємкістю 4 Кбайт, яка може бути розширена до 64 Кбайт за рахунок підключення мікросхем зовнішньої пам'яті програм. Внутрішня пам'ять програм КР1816ВЕ51 і КР1830ВЕ51 є ПЗП, що формується при виготовленні ОЕОМ. Внутрішня пам'ять програм КМ1816ВЕ751 є ППЗУ з ультрафіолетовим стиранням.

Таким чином, для ОЕОМ КР1816ВЕ51, КМ1816ВЕ751 і КР1830ВЕ51 внутрішня і зовнішня пам'ять програм розділені в співвідношенні 4 К/60 До.

ОЕОМ КР1816ВЕ31 і КР1830ВЕ31 не мають внутрішньої пам'яті програм і можуть працювати лише із зовнішньою, ємкістю до 64 Кбайт.

З точки зору програміста є лише один вигляд пам'яті програм об'ємом 64 К. Тот факт, що у ряді ОЕОМ він утворюється комбінацією масивів, що знаходяться на кристалі і поза ним, в співвідношенні 4 К/60 До для програміста неощутим, оскільки ОЕОМ автоматично вибирає байт з відповідного масиву відповідно до його адреси.

Сигналом, що стробує вибірку і введення байта із зовнішньої пам'яті програм в ОЕОМ є сигнал ОЕОМ . Для ОЕОМ, що містять внутрішню пам'ять програм, формується лише в тому випадку, якщо адреса в лічильнику команд перевершує максимальну адресу внутрішньої пам'яті програм 0FFFH (тобто для вибірок з внутрішньої пам'яті програм не формується).

Для ОЕОМ, що не мають внутрішньої пам'яті програм, формується при будь-якому зверненні до пам'яті програм.

ОЕОМ сімейства МК51 мають зовнішнє виведення ОРПП (DEMA), за допомогою якого можна заборонити роботу внутрішньої пам'яті програм, для чого необхідно подати на виведення DEMA "0". При цьому внутрішня пам'ять програм відключається і, починаючи з нульової адреси, всі звернення відбуваються до зовнішньої пам'яті програм з формуванням сигналу . В разі, якщо DEMA = 1, працюють і внутрішня і зовнішня пам'ять програм. Для ОЕОМ, що не мають внутрішньої пам'яті програм, для нормальної роботи завжди необхідно задавати DEMA = 0.

Таким чином, доступ до зовнішньої пам'яті програм здійснюється в двох випадках:

1) при дії сигналу DEMA = 0 незалежно від адреси звернення

2) в будь-якому разі, якщо програмний лічильник (РС) містить число, більше чим 0FFFH.

При вибірці із зовнішньої пам'яті програм завжди використовується 16-бітова адреса, молодший байт якої видається через порт Р0, а старший байт – через порт Р2 ОЕОМ. Байт із зовнішньої пам'яті програм вводиться в ОЕОМ через порт Р0, який в цьому випадку використовується як шина адреса/данных в режимі мультиплексування.

На рисунку 24 показані молодші адреси пам'яті програм, які, як правило, відводяться під обробку переривань і початок роботи ОЕОМ після скидання

Рисунок 24 - Молодші адреси пам'яті програм

Внутрішня пам'ять даних ОЕОМ складається з двох областей: 128 байт оперативної пам'яті (ОЗУ) з адресами 0 – 7FH і області регістрів спеціальних функцій, що займає адреси 80Н, – FFH. Розподіл простору внутрішньої пам'яті даних показаний на рисунку 25.

Рисунок 25 - Адресний простір внутрішньої пам'яті даних

Фізично внутрішнє ОЗУ даних і область регістрів спеціальних функцій є окремими пристроями.

Всі вічка внутрішнього ОЗУ даних можуть адресуватися з використанням прямої і непрямої адресації (режими адресації описані в описі системи команд ОЕОМ). Крім того, внутрішнє ОЗУ даних має наступні особливості.

Молодші 32 байти внутрішнього ОЗУ даних згруповано в 4 банки по 8 регістрів в кожному (БАНК0 – БАНК3 на рисунку 25). Команди програми можуть звертатися до регістрів, використовуючи їх імена R0 – R7. Два біта PSW (Вказівники банку робочих регістрів RS0 і RS1) визначають, з регістрами якого банку проводяться маніпуляції. Наявність такого механізму роботи з вічками ОЗУ дозволяє економити пам'ять програм, оскільки команди, що працюють з регістрами R0, – R7, коротше за команди, що використовують пряму адресацію.

Наступні після банків регістрів внутрішнього ОЗУ даних 16 байт (адреси 20Н – 2FH) утворюють область вічок, до яких можлива побітова адресація. Набор команд ОЕОМ сімейства МК51 містить значну кількість інструкцій, що дозволяють працювати з окремими бітами, використовуючи при цьому пряму адресацію. 128 біт, складових дану область внутрішнього ОЗУ даних, мають адреси 00Н – 7FH і призначені для роботи з такими інструкціями. Бітова адресація ОЗУ показана на рисунку 26, де в квадратах, символізуючих біти, вказані їх адреси.

|

Адреса байта

|

ст. біт (D7) мл біт (D0)

| ||||||||

|

2FH

|

7F

|

7E

|

7D

|

7C

|

7B

|

7A

|

79 |

78 |

|

|

2EH

|

77 |

76 |

75 |

74 |

73 |

72 |

71 |

70 |

|

|

2DH

|

6F

|

6E

|

6D

|

6C

|

6B

|

6A

|

69 |

68 |

|

|

2CH

|

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 |

|

|

2BH

|

5F

|

5E

|

5D

|

5C

|

5B

|

5A

|

59 |

58 |

|

|

2AH

|

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 |

|

|

29H

|

4F

|

4E

|

4D

|

4C

|

4B

|

4A

|

49 |

48 |

|

|

28H

|

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

|

|

27H

|

3F

|

3E

|

3D

|

3C

|

3B

|

3A

|

39 |

38 |

|

|

26H

|

37 |

36 |

35 |

34 |

33 |

32 |

31 |

30 |

|

|

25H

|

2F

|

2E

|

2D

|

2C

|

2B

|

2A

|

29 |

28 |

|

|

24H

|

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

|

|

23H

|

1F

|

1E

|

1D

|

1C

|

1B

|

1A

|

19 |

18 |

|

|

22H

|

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

|

|

21H

|

0F

|

0E

|

0D

|

0C

|

0B

|

0A

|

09 |

08 |

|

|

20H

|

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

|

1FH

18H

|

БАНК 3

|

R7

R0

| |||||||

|

17H

10H

|

БАНК 2

|

R7

R0

| |||||||

|

0FH

08H

|

БАНК 1

|

R7

R0

| |||||||

|

07H

00H

|

БАНК 0

|

R7

R0

| |||||||

Рисунок 26 - Бітова адресація ОЗУ

Звернення до внутрішнього ОЗА даних завжди здійснюється з використанням 8-розрядної адреси. При включенні живлення вміст ОЗУ матиме випадкове значення.

Область регістрів спеціальних функцій містить клямки портів, регістри таймеров/счетчиков, регістри управління і тому подібне Повний список регістрів спеціальних функцій з їх адресами приведений таблиці 2. Ці регістри допускають лише пряму адресацію. Одинадцять байт в області регістрів спеціальних функцій допускають як байтову, так і побітову адресацію. Список регістрів з побітовою адресацією показаний на рисунку 27. Біти в даної області регістрів спеціальних функцій мають адреси 80Н – F7H.

|

Прямі адреси байтів

|

0F0H

|

ст. біт (D7) мл біт (D0)

| |||||||||

|

F7

|

F6

|

F5

|

F4

|

F3

|

F2

|

F1

|

F0

|

B

|

Ідентифікатори регістрів, що програмно адресуються, і бітів

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

|

0E0H

|

E7

|

E6

|

E5

|

E4

|

E3

|

E2

|

E1

|

E0

|

ACC

| ||

|

|

CV

|

AC

|

F0

|

RS1

|

RS0

|

OV

|

|

P

|

| ||

|

|

0D0H

|

D7

|

D6

|

D5

|

D4

|

D3

|

D2

|

D1

|

D0

|

PSW

|

|

|

|

|

|

|

PT2

|

PS

|

PT1

|

PX1

|

PT0

|

PX0

|

|

|

|

|

0B8H

|

–

|

–

|

BD

|

BC

|

BB

|

BA

|

B9

|

B8

|

IP

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0B0H

|

B7

|

B6

|

B5

|

B4

|

B3

|

B2

|

B1

|

B0

|

P3

|

|

|

|

|

EA

|

|

ET2

|

ES

|

ET1

|

EX1

|

ET0

|

EX0

|

|

|

|

|

0A8H

|

AF

|

–

|

AD

|

AC

|

AB

|

AA

|

A9

|

A8

|

IE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0A0H

|

A7

|

A6

|

A5

|

A4

|

A3

|

A2

|

A1

|

A0

|

P2

|

|

|

|

|

SM0

|

SM1

|

SM2

|

REN

|

TB8

|

RB8

|

TI

|

RI

|

|

|

|

|

98H

|

9F

|

9E

|

9D

|

9C

|

9B

|

9A

|

99 |

98 |

SCON

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

90H

|

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

P1

|

|

|

|

|

TF1

|

TR1

|

TE0

|

TR0

|

IE1

|

IT1

|

IE0

|

IT0

|

|

|

|

|

88H

|

8F

|

8E

|

8D

|

8C

|

8B

|

8A

|

89 |

88 |

TCON

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80H

|

87 |

86 |

85 |

84 |

83 |

82 |

81 |

80 |

P0

|

|

Рисунок 27 - Адреси бітів регістрів спеціальних функцій

Зовнішня пам'ять даних формується додатковими мікросхемами пам'яті, що підключаються до ОЕОМ, і може мати ємкість до 64 Кбайт. Простори внутрішньої і зовнішньої пам'яті даних не перетинаються, оскільки доступ до них здійснюється за допомогою різних команд. Для роботи із зовнішньою пам'яттю даних існують спеціальні команди MOVX, які не впливають на внутрішню пам'ять даних ОЕОМ. Таким чином, в системі можуть бути одночасно присутніми внутрішня пам'ять даних з адресами 00H – FFH і зовнішня пам'ять даних з адресами 0000Н – FFFFH. Звернення до вічок зовнішньої пам'яті даних здійснюється лише з використанням непрямої адресації по регістрах R0 і R1 активного банку регістрів внутрішнього ОЗУ (команди типа MOV @Ri) або по регістру спеціальних функцій DPTR (команди типа MOV @DPTR). Відповідно в першому випадку формуватиметься 8-розрядний, а в другому випадку 16-розрядний адреси зовнішньої пам'яті даних.

При зверненнях до зовнішньої пам'яті даних адреса виводиться через порт Р0 (молодший байт) і порт Р2 (старший байт) ОЕОМ. Обмін байтом даних (запис і читання) проводиться через порт Р0 ОЕОМ, тобто порт Р0 використовується як шина адреса/данных в режимі мультиплексування.

Прочитування даних із зовнішньої пам'яті даних в ОЕОМ проводиться за допомогою вихідного сигналу ОЕОМ, а запис даних з ОЕОМ в зовнішню пам'ять даних за допомогою вихідного сигналу ОЕОМ .

Кожен тип зовнішньої пам'яті (пам'ять програм, пам'ять даних) може бути доданий незалежно від іншого і кожен використовує ті ж шини адреси даних, але різні сигнали управління.

4.6.1. Особливий режим роботи пам'яті ОЕОМ

Дана ОЕОМ не є машиною класичною “фон нейманівської” архітектури, оскільки містить пам'ять даних і пам'ять програм, які логічно (програмно) розділені. Отже, оперативна пам'ять даних (резидентна або зовнішня) не можуть бути використані для зберігання код програми, оскільки вибірка команд в ОЕОМ проводиться лише з пам'яті програм (внутрішньою і зовнішньою). Це пояснюється тим, що в більшості вживань мікроконтроллера потрібна наявність однієї незмінної прикладної програми, яка записується в ПЗП на етапі розробки мікропроцесорної системи (МПС), а ОЗУ використовується для тимчасового зберігання змінних.

Проте, на етапі розробки і відладки прикладних програм машина “фон нейманівського” типа виявляється дуже зручним, оскільки дозволяє розробникові оперативно змінювати коди прикладної програми, що розміщується в ОЗУ.

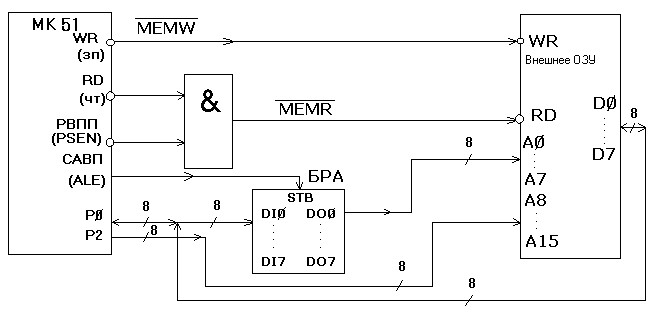

Для цього МПС з ОЕОМ може бути модифікована з метою поєднання адресних просторів ВПП і ВПД шляхом використання зовнішньої логіки, як показано на рисунку 28. ВПП і ВПД об'єднані загалом зовнішньому ОЗУ, об'ємом 64 Кбайт. Запис даних в ОЗУ стробується сигналом, формованому на виході WR (P 3.6) при виконанні команд запису у ВПД.

Рисунок 28 – Поєднання адресних просторів ВПД і ВПП в єдиному

зовнішньому ОЗУ, об'ємом 64 Кбайт

Читання ОЗУ стробується сигналом, формованому в одному з двох випадків:

- або при читанні ВПД (супроводиться сигналом (Р 3.7) при виконанні команд читання ВПД);

- або при читанні команд програми з ВПП (супроводиться сигналом, формованому при зверненні до ВПП).

Логічний елемент І (конъюнктор) реалізує функцію перемикача:

![]() (7)

(7)

де змінна А відповідає логічному сигналу на виведенні RD (Р 3.7), а змінна В – на виведенні РВПП.

Порт Р0 використовується в режимі “мультиплексування”. Спочатку через нього виводиться молодший байт адреси зовнішнього ОЗУ (ВПД або ВПП), яка запам'ятовується в зовнішньому буферному регістрі адреси (БРА). Потім по лініях Р0 здійснюється обмін даними між ОЕОМ і ОЗУ. Старший байт адреси ВПП або ВПД постійно присутній на виході порту Р2 протягом всього циклу роботи із зовнішньою пам'яттю.

При використанні описаного особливого режиму роботи пам'яті слід враховувати, що в ОЕОМ на фізичному (апаратному) рівні використовується п'ять видів пам'яті: РПД; РПП; ВПД; ВПП і блок регістрів спеціальних функцій. Внаслідок цього, переміщувана версія прикладної програми, яка відлагоджується в зовнішній поєднаній пам'яті програм і даних (у зовнішньому ОЗУ), відрізнятиметься від завантажуваної в пам'ять програм остаточної версії робочої програми.

Описаний спосіб організації управління зовнішньою пам'яттю може бути використаний в тих застосуваннях МК 51, де потрібне оперативне перезавантаження або модифікація прикладних програм за допомогою пристроїв введення-виводу (УВВ) як в ЕОМ класичної архітектури.

4.7. Розширення резидентної (внутрішньою) системи

введення-виводу (РСВВ/ВИВ)

Для сполучення даної ОЕОМ з об'єктом, що має велике число входів-виходів, можна розширити резидентну систему введення-виводу, підключивши до мікроконтроллера необхідну кількість зовнішніх портів. Таке розширення може бути виконане двома способами:

з використанням стандартного розширювача введення-виведення (РВВ) КР580ВР43;

із застосуванням інтерфейсних БІС типа КР580ВВ55, КР580ВВ51.

Перший спосіб детально описаний в [2].

Нижче зупинимося на другому.

У приведеному на рисунку 29 прикладі до ОЕОМ підключено 64 мікросхеми КР580ВВ55, що є паралельним програмованим інтерфейсом (ППІ). Кожен ППІ містить три 8-розрядні порти введення-виведення інформації: порт А (РА7.РА0); порт В (РВ7.РВ0) і порт З (РС7.РС0). Це дозволяє організувати (64 x 3)=192 8-розрядних порту введення-виводу. Для вибору (адресації) усередині ППІ одного з 3-х портів або регістра слова (РУСЯВИЙ), що управляє, використовуються два його входи: А1, А0. Переклад один з вибраних ППІ в активний стан здійснюється нульовим сигналом на вході CS (вибір кристала).

Звернення до інтерфейсів проводиться командами роботи з ВПД:

MOVX @Ri, A; ВПД (Ri) ( A – при виводі;

MOVX A @Ri; A ( ВПД (Ri) – при введенні даних.

При цьому порт Р0 ОЕОМ використовується в режимі “мультиплексування”.

Рисунок 29 - Розширення РС Вв/Вив за допомогою мікросхем КР580ВВ55

Спочатку на виходи Р0 видається вміст регістра Ri (i = 0,1), яке запам'ятовується (“замикається”) в зовнішньому буферному 8-розрядному регістрі адреси (БРА). Потім по лініях Р0 проводиться обмін інформацією між ОЕОМ і вибраним портом ППІ. Два молодші розряди адреси з виходу БРА через підсилювачі поступають на виходи А1, А0 ППІ і вибирають в нім необхідний порт або РУСЯВИЙ (при програмуванні ППІ). Що залишилися шість старших розряду з виходу БРА подаються на входи дешифратора адреси (ДША), що перетворює шестирозрядний паралельний двійковий код (ДК) в шестидесятичетырехпозиционный унітарний код. Залежно від комбінації ДК на входах ДША активний сигнал низького рівня з'являється лише на одному з виходів ДША, номер якого відповідає десятковому еквіваленту вхідного ДК. Цей сигнал подається на вхід CS вибраного ППІ і підключає його виводи D0.D7 до ліній порту Р0. Останні невибрані ППІ відключаються від Р0 (переводяться в 3-й, високоімпеданс стан). Шинний формувач (ШФ) служить для підсилювача сигналів, що знімаються з виходів порту P0.

При використанні команд MOVX @DPTR, A; MOVX A @DPTR і деякому ускладненні схеми число ППІ, що підключаються, а отже, число портів введення-виводу може бути значно збільшене.

5. Система команд

Система команд ОЕОМ надає великі можливості обробки даних, забезпечує реалізацію логічних, арифметичних операцій, а також управління в режимі реального часу. Реалізована побітова, потетрадная (4 біта), побайтова (8 біт) і 16-розрядна обробка даних.

БІС сімейства МК51 – 8-розрядна ОЕОМ: ПЗП, ОЗУ, регістри спеціального призначення, АЛУ і зовнішні шини мають байтову організацію. Двобайтові дані використовуються лише регістром-Вказівником (DPTR) і лічильником команд (РС). Слід зазначити, що регістр-Вказівник даних може бути використаний як двобайтовий регістр DPTR або як два однобайтові регістри спеціального призначення DPH і DPL. Лічильник команд завжди використовується як двобайтовий регістр.

Набор команд ОЕОМ має 42 мнемонічних позначення (абревіатур) команд для конкретизації 33 функцій цієї системи.

Синтаксис більшості команд асемблерної мови ОЕОМ складається з мнемонічного позначення функції, услід за яким йдуть операнди, вказуючі методи адресації і типів даних. Різні типи даних або режими адресації визначаються встановленими операндами, а не змінами мнемонічних позначень. Наприклад, абревіатура "MOV" використовується вісімнадцятьма різними командами для обробки трьох типів даних (бітів, байтів, адрес) в різних адресних просторах.

Мнемонічні позначення функцій однозначно пов'язані з конкретними комбинациями способів адресації і типами даних. Всього в системі команд можливо 111 таких поєднань, які залежно від їх функціонального призначення можна умовно розбити на п'ять груп:

команди передачі даних (таблиця 21);

арифметичні команди (таблиця 22);

логічні операції (таблиця 23);

операції з бітами (таблиця 24);

команди передачі управління (таблиця 25).

Названі таблиці (21.25) дають досить повну характеристику кожній з 111 базової команди:

назва команди (у короткій формі описує виконувану функцію);

мнемокод (включає мнемоніку команди і опис операндів, що беруть участь в операції);

код операції команди (КОП);

тип команди (Т);

довжину команди в байтах (Б);

кількість машинних циклів, потрібних для виконання команди (Ц);

|

коментар. Таблиця 21 – Група команд передачі даних

| |||||||

|

| |||||||

|

№

|

Назва команди

|

Мнемокод

|

КОП

|

Т

|

Би

|

Ц

|

Операція

|

|

1 |

Пересилка в акумулятор з регістра (n=0..7)

|

MOV A, Rn

|

11101rrr

|

1 |

1 |

1 |

(A) ( (Rn)

|

|

2 |

Пересилка в акумулятор прямоадресуемого байта

|

MOV A, ad

|

11100101 |

3 |

2 |

1 |

(A) ( (ad)

|

|

3 |

Пересилка в акумулятор байта з РПД (i=0,1)

|

MOV A @Ri

|

1110011i

|

1 |

1 |

1 |

(A) ( РПД(Ri)

|

|

4 |

Завантаження в акумулятор константи

|

MOV A, #D8

|

01110100 |

2 |

2 |

1 |

(A) ( D8

|

|

5 |

Пересилка в регістр (n=0..7) з акумулятора

|

MOV Rn, A

|

11111rrr

|

1 |

1 |

1 |

(Rn) ( (A)

|

|

6 |

Пересилка в регістр прямоадресуемого байта

|

MOV Rn, ad

|

10101rrr

|

3 |

2 |

2 |

(Rn) ( (ad)

|

|

7 |

Завантаження в регістр (n=0..7) константи

|

MOV Rn, #D8

|

01111rrr

|

2 |

2 |

1 |

(Rn) ( D8

|

|

8 |

Пересилка за прямою адресою акумулятора

|

MOV ad, A

|

11110101 |

3 |

2 |

1 |

(ad) ( (A)

|

|

9 |

Пересилка за прямою адресою регістра

|

MOV ad, Rn

|

10001rrr

|

3 |

2 |

2 |

(ad) ( (Rn)

|

|

10 |

Пересилка прямоадресуемого байта за прямою адресою

|

MOV add, ads

|

10000101 |

9 |

3 |

2 |

(add) ( (ads)

|

|

11 |

Пересилка байта з РПД за прямою адресою

|

MOV ad @Ri

|

1000011i

|

3 |

2 |

2 |

(ad) ( РПД(Ri)

|

|

12 |

Пересилка за прямою адресою константи

|

MOV ad, #D8

|

01110101 |

7 |

3 |

2 |

(ad) ( D8

|

|

13 |

Пересилка в РПД з акумулятора

|

MOV @Ri, A

|

1111011i

|

1 |

1 |

1 |

РПД(Ri)( (A)

|

|

14 |

Пересилка в РПД прямоадресуемого байта

|

MOV @Ri, ad

|

0110011i

|

3 |

2 |

2 |

РПД(Ri)( (ad)

|

|

15 |

Пересилка в РПД константи

|

MOV @Ri, #D8

|

0111011i

|

2 |

2 |

1 |

РПД(Ri)( D8

|

|

16 |

Завантаження регістра-Вказівника даних

|

MOV DPTR, #D16

|

10010000 |

13 |

3 |

2 |

(DPTR) ( D16

|

|

17 |

Пересилка в акумулятор байта з ПП

|

MOVC A @A+DPTR

|

10010011 |

1 |

1 |

2 |

(A) (ПП((A) + (DPTR))

|

|

18 |

Пересилка в акумулятор байта з ПП

|

MOVC A @A+PC

|

10000011 |

1 |

1 |

2 |

(РС) ( (РС) + 1

|

|

|

|

|

|

|

|

|

(A) ( ПП((A) + (РС))

|

|

19 |

Пересилка в акумулятор байта з ВПД

|

MOVX A @Ri

|

1110001i

|

1 |

1 |

2 |

(A) ( ВПД(Ri)

|

|

20 |

Пересилка в акумулятор байта з розширеної ВПД

|

MOVX A @DPTR

|

11100000 |

1 |

1 |

2 |

(A) ( ВПД(DPTR)

|

|

21 |

Пересилка у ВПД з акумулятора

|

MOVX @Ri, A

|

1111001i

|

1 |

1 |

2 |

ВПД(Ri)( (A)

|

|

22 |

Пересилка в розширену ВПД з акумулятора

|

MOVX @DPTR, A

|

11110000 |

1 |

1 |

2 |

ВПД(DPTR)( (A)

|

|

23 |

Завантаження в стек

|

PUSH ad

|

11000000 |

3 |

2 |

2 |

(SP) ( (SP) + 1

|

|

|

|

|

|

|

|

|

РПД(SP)( (ad)

|

|

24 |

Витягання із стека

|

POP ad

|

11010000 |

3 |

2 |

2 |

(ad) ( РПД(SP)

|

|

|

|

|

|

|

|

|

(SP) ( (SP) - 1

|

|

25 |

Обмін акумулятора з регістром

|

XCH A, Rn

|

11001rrr

|

1 |

1 |

1 |

(A) ( (Rn)

|

|

26 |

Обмін акумулятора з прямоадресуемым байтом

|

XCH A, ad

|

11000101 |

3 |

2 |

1 |

(A) ( (ad)

|

|

27 |

Обмін акумулятора з байтом з PПД

|

XCH A @Ri

|

1100011i

|

1 |

1 |

1 |

(A) ( РПД(Ri)

|

|

28 |

Обмін молодшої тетради акумулятора з молодшою

|

XCHD A @Ri

|

1101011i

|

1 |

1 |

1 |

(A0-3) ( РПД(Ri) 0-3

|

|

|

тетрадою байта РПД

|

|

|

|

|

|

|

|

Таблиця 22 – Група команд арифметичних операцій

| |||||||

|

| |||||||

|

№

|

Назва команди

|

Мнемокод

|

КОП

|

Т

|

Би

|

Ц

|

Операція

|

|

1 |

Складання акумулятора з регістром (n=0..7)

|

ADD A, Rn

|

00101rrr

|

1 |

1 |

1 |

(A) ( (A) + (Rn)

|

|

2 |

Складання акумулятора з прямоадресуемым байтом

|

ADD A, ad

|

00100101 |

3 |

2 |

1 |

(A) ( (A) + (ad)

|

|

3 |

Складання акумулятора з байтом з РПД (i=0,1)

|

ADD A @Ri

|

0010011i

|

1 |

1 |

1 |

(A) ( (A) + РПД(Ri)

|

|

4 |

Складання акумулятора з константою

|

ADD A, #D8

|

00100100 |

2 |

2 |

1 |

(A) ( (A) + D8

|

|

5 |

Складання акумулятора з регістром і перенесенням

|

ADDC A, Rn

|

00111rrr

|

1 |

1 |

1 |

(A) ( (A) + (Rn) + (C)

|

|

6 |

Складання акумулятора з прямоадресуемым байтом і перенесенням

|

ADDC A, ad

|

00110101 |

3 |

2 |

1 |

(A) ( (A) + (ad) + (C)

|

|

7 |

Cложение акумулятора з байтом з РПД і перенесення

|

ADDC A @Ri

|

0011011i

|

1 |

1 |

1 |

(A) ( (A) + РПД(Ri)+ (C)

|

|

8 |

Cложение акумулятора з константою і перенесенням

|

ADDC A, #D8

|

00110100 |

2 |

2 |

1 |

(A) ( (A) + D8 + (C)

|

|

9 |

Десяткова корекція акумулятора (після складання два

|

DA A

|

11010100 |

1 |

1 |

1 |

Якщо (A3-0) > 9V(AC)=1,

|

|

|

операндів, представлених в упакованому BCD-коде)

|

|

|

|

|

|

то (А7-0) ((A7-0) + 6 потім

|

|

|

|

|

|

|

|

|

якщо (A7-4) > 9V (C)=1, то

|

|

|

|

|

|

|

|

|

(A7-4) ( (A7-4) + 6

|

|

10 |

Віднімання з акумулятора регістра і позики

|

SUBB A, Rn

|

10011rrr

|

1 |

1 |

1 |

(A) ( (A) - (C) - (Rn)

|

|

11 |

Віднімання з акумулятора прямоадресуемого байта і позики

|

SUBB A, ad

|

10010101 |

3 |

2 |

1 |

(A) ( (A) - (C) - (ad)

|

|

12 |

Віднімання з акумулятора байта РПД і позики

|

SUBB A @Ri

|

1001011i

|

1 |

1 |

1 |

(A) ( (A) - (C) - РПД(Ri)

|

|

13 |

Віднімання з акумулятора константи і позики

|

SUBB A, #D8

|

10010100 |

2 |

2 |

1 |

(A) ( (A) - (C) - D8

|

|

14 |

Інкремент акумулятора

|

INC A

|

00000100 |

1 |

1 |

1 |

(A) ( (A) + 1

|

|

15 |

Інкремент регістра

|

INC Rn

|

00001rrr

|

1 |

1 |

1 |

(Rn) ( (Rn) + 1

|

|

16 |

Інкремент прямоадресуемого байта

|

INC ad

|

00000101 |

3 |

2 |

1 |

(ad) ( (ad) + 1

|

|

17 |

Інкремент байта в РПД

|

INC @Ri

|

0000011i

|

1 |

1 |

1 |

РПД(Ri)( РПД(Ri)+ 1

|

|

18 |

Інкремент Вказівника даних

|

INC DPTR

|

10100011 |

1 |

1 |

2 |

(DPTR) ( (DPTR) + 1

|

|

19 |

Декремент акумулятора

|

DEC A

|

00010100 |

1 |

1 |

1 |

(A) ( (A) - 1

|

|

20 |

Декремент регістра

|

DEC Rn

|

00011rrr

|

1 |

1 |

1 |

(Rn) ( (Rn) - 1

|

|

21 |

Декремент прямоадресуемого байта

|

DEC ad

|

00010101 |

3 |

2 |

1 |

(ad) ( (ad) - 1

|

|

22 |

Декремент байта в РПД

|

DEC @Ri

|

0001011i

|

1 |

1 |

1 |

РПД(Ri)( РПД(Ri) - 1

|

|

23 |

Множення акумулятора на регістр В

|

MUL AB

|

10100100 |

1 |

1 |

4 |

Якщо (А) х(В)> 255, то (B)(A) ( (A)x(B); якщо (А) х(В)< 255, то (A) ((A)x(B)

|

|

24 |

Ділення акумулятора на регістр В

|

DIV AB

|

10000100 |

1 |

1 |

4 |

(A)((A)/(B)—целая частина (В) ( R ((А) / (В)) — залишок від ділення

|

|

Таблиця 23 – Група команд логічних операцій

| ||||||||

|

| ||||||||

|

№

|

Назва команди

|

Мнемокод

|

КОП

|

Т

|

Би

|

Ц

|

Операція

| |

|

1 |

Логічне І акумулятора і регістра

|

ANL A, Rn

|

01011rrr

|

1 |

1 |

1 |

(A) ( (A) ( (Rn)

| |

|

2 |

Логічне І акумулятора і прямоадресуемого байта

|

ANL A, ad

|

01010101 |

3 |

2 |

1 |

(A) ( (A) ( (ad)

| |

|

3 |

Логічне І акумулятора і байта з РПД

|

ANL A @Ri

|

0101011i

|

1 |

1 |

1 |

(A) ( (A) ( РПД(Ri)

| |

|

4 |

Логічне І акумулятора і константи

|

ANL A, #D8

|

01010100 |

2 |

2 |

1 |

(A) ( (A) ( D8

| |

|

5 |

Логічне І прямоадресуемого байта і акумулятора

|

ANL ad, A

|

01010010 |

3 |

2 |

1 |

(ad) ( (ad) ( (A)

| |

|

6 |

Логічне І прямоадресуемого байта і константи

|

ANL ad, #D8

|

01010011 |

7 |

3 |

2 |

(ad) ( (ad) ( D8

| |

|

7 |

Логічне АБО акумулятора і регістра

|

ORL A, Rn

|

01001rrr

|

1 |

1 |

1 |

(A) ( (A) ( (Rn)

| |

|

8 |

Логічне АБО акумулятора і прямоадресуемого байта

|

ORL A, ad

|

01000101 |

3 |

2 |

1 |

(A) ( (A) ( (ad)

| |

|

9 |

Логічне АБО акумулятора і байта з РПД

|

ORL A @Ri

|

0100011i

|

1 |

1 |

1 |

(A) ( (A) ( РПД(Ri)

| |

|

10 |

Логічне АБО акумулятора і константи

|

ORL A, #D8

|

01000100 |

2 |

2 |

1 |

(A) ( (A) ( D8

| |

|

11 |

Логічне АБО прямоадресуемого байта і акумулятора

|

ORL ad, A

|

01000010 |

3 |

2 |

1 |

(ad) ( (ad) ( (A)

| |

|

12 |

Логічне АБО прямоадресуемого байта і константи

|

ORL ad, #D8

|

01000011 |

7 |

3 |

2 |

(ad) ( (ad) ( D8

| |

|

13 |

Що виключає АБО акумулятора і регістра

|

XRL A, Rn

|

01101rrr

|

1 |

1 |

1 |

(A) ( (A) ( (Rn)

| |

|

14 |

Що виключає АБО акумулятора і прямоадресуемого байта

|

XRL A, ad

|

01100101 |

3 |

2 |

1 |

(A) ( (A) ( (ad)

| |

|

15 |

Що виключає АБО акумулятора і байта РПД

|

XRL A @Ri

|

0110011i

|

1 |

1 |

1 |

(A) ( (A) ( РПД(Ri)

| |

|

16 |

Що виключає АБО акумулятора і константи

|

XRL A, #D8

|

01100100 |

2 |

2 |

1 |

(A) ( (A) ( D8

| |

|

17 |

Що виключає АБО прямоадресуемого байта і акумулятора

|

XRL ad, A

|

01100010 |

3 |

2 |

1 |

(ad) ( (ad) ( (A)

| |

|

18 |

Що виключає АБО прямоадресуемого байта і константи

|

XRL ad, #D8

|

01100011 |

7 |

3 |

2 |

(ad) ( (ad) ( D8

| |

|

19 |

Скидання акумулятора

|

CLR A

|

11100100 |

1 |

1 |

1 |

(A) ( 0

| |

|

20 |

Інверсія акумулятора

|

CPL A

|

11110100 |

1 |

1 |

1 |

(A) ( ( )

| |

|

21 |

Зрушення акумулятора вліво циклічне

|

|

RL A

|

00100011 |

1 |

1 |

1 |

(An+1) ( (An), n=0..6, (A0) ( (A7)

|

|

22 |

Зрушення акумулятора вліво через перенесення

|

|

RLC A

|

00110011 |

1 |

1 |

1 |

(An+1)( (An), n=0..6, (A0) ( (C), (C) ( (A7)

|

|

23 |

Зрушення акумулятора управо циклічне

|

|

RR A

|

00000011 |

1 |

1 |

1 |

(An) ( (An+1), n=0..6, (A7) ( (A0)

|

|

24 |

Зрушення акумулятора управо через перенесення

|

|

RRC A

|

00010011 |

1 |

1 |

1 |

(An) ( (An+1), n=0..6, (A7) ( (C), (C) ( (A0)

|

|

25 |

Обмін місцями тетрад в акумуляторі

|

SWAP A

|

11000100 |

1 |

1 |

1 |

(A3-0) ( (A7-4)

| |

|

Таблиця 24 – Група команд операцій з бітами

| |||||||

|

| |||||||

|

№

|

Назва команди

|

Мнемокод

|

КОП

|

Т

|

Би

|

Ц

|

Операція

|

|

1 |

Скидання перенесення

|

CLR C

|

11000011 |

1 |

1 |

1 |

(C) ( 0

|

|

2 |

Скидання біта

|

CLR bit

|

11000010 |

4 |

2 |

1 |

(b) ( 0

|

|

3 |

Установка перенесення

|

SETB C

|

11010011 |

1 |

1 |

1 |

(C) ( 1

|

|

4 |

Установка біта

|

SETB bit

|

11010010 |

4 |

2 |