- •Оглавление

- •4. Таймеры

- •5. Память пик-контроллеров

- •2.1.Регистр status

- •2.2 Регистр option_reg

- •2.3.Регистры pclath и pcl

- •2.4.Косвенная адресация, регистры indf и fsr

- •3.Порты ввода/вывода

- •3.1.Регистры porta и trisa

- •3.2.Регистры portb и trisb

- •3.3.Регистры portс и trisс

- •3.4.Регистры portd и trisd

- •4.1.Модуль таймера tmr0

- •4.2.Модуль таймера tmr1

- •4.3. Модуль таймера tmr2

- •5.1.Организация памяти программ

- •5.2.Организация памяти данных

- •5.3.Eeprom память данных. Flash память программ.

- •5.4. Регистры eecon1, eecon2

- •5.5. Eeprom память данных..

- •6.Аналого-цифровой преобразователь

- •6.1. Регистры ацп

- •6.2.Порядок работы с ацп

- •6.2.1..Выбор источника тактовых импульсов для ацп

- •6.2.2.Настройка аналоговых входов

- •6.2.3.. Аналого-цифровое преобразование

- •6.2.4. Выравнивание результата преобразования

- •7.Прерывания микроконтроллеров

- •7.1.Регистры, используемые системой прерываний.

- •7.2.Внешнее прерывание с входа rb0/int

- •7.5. Сохранение контекста при обработке прерываний

- •8.Система команд

4.3. Модуль таймера tmr2

TMR2 – 8-разрядный таймер с программируемым предделителем и выходным делителем, 8-разярдным регистром периода PR2. TMR2 может быть опорным таймером для CCP модуля в ШИМ режиме. Регистры TMR2 доступны для записи/чтения и очищаются при любом виде сброса.

Входной тактовый сигнал (Fosc/4) поступает через предделитель с программируемым коэффициентом деления (1:1, 1:4 или 1:16), определяемый битами T2CKPS1:T2CKPS0 (T2CON<1:0>)/

TMR2 cчитает, инкрементируя от 00h до значения в регистре PR2, затем сбрасывается в 00h на следующем машинном цикле. Регистр PR2 доступен для записи и чтения. После сброса значение регистра PR2 равно FFh.

Сигнал переполнения TMR2 проходит через выходной 4-разядный делитель с программируемым коэффициентом деления (от 1:1 до 1:16 включительно) для установки флага TMR2IF в регистре PIR1<1>.

Для уменьшения энергопотребления таймер TMR2 может быть выключен сбросом бита TMR2ON (T2CON<2>) в "0".

Предделитель и выходной делитель TMR2

Счетчик предделителя и выходного делителя сбрасываются в случае:

- записи в регистр TMR2; - записи в регистр T2CON; - любого вида сброса микроконтроллера (POR, BOR, сброс WDT или активный сигнал –MCLR)

Регистр TMR2 не очищается при записи в T2CON.

Сигнал TMR2

Сигнал переполнения TMR2 (до выходного предделителя) поступает в модуль SSP для управления скоростью передачи данных.

5. Память ПИК-контроллеров

Особый интерес представляет организация памяти в микроконтроллерах. В микроконтроллерах три вида памяти: память программ, память данных и ЕЕPROM памяти данных. Память программ и память данных имеют раздельные шины данных и адреса, что позволяет выполнять параллельный доступ.

5.1.Организация памяти программ

Микроконтроллеры имеют 13-разрядный счетчик команд РС, способный адресовать 8К х 14 слов памяти программ. Физически реализовано FLASH памяти 8К х 14 для PIC16F877. Обращение к физически нереализованной памяти программ приведет к адресации реализованной памяти.

Адрес вектора сброса – 0000h. Адрес вектора прерываний – 0004h.

Память программ состоит из 4-х страниц: страница 0, страница 1, страница 2, страница 3.

Страница 0 имеет адреса: 0005h-07FFh.

-

0800h-0FFFh.

-

1000h-17FFh

-

1800h-1FFFh

5.2.Организация памяти данных

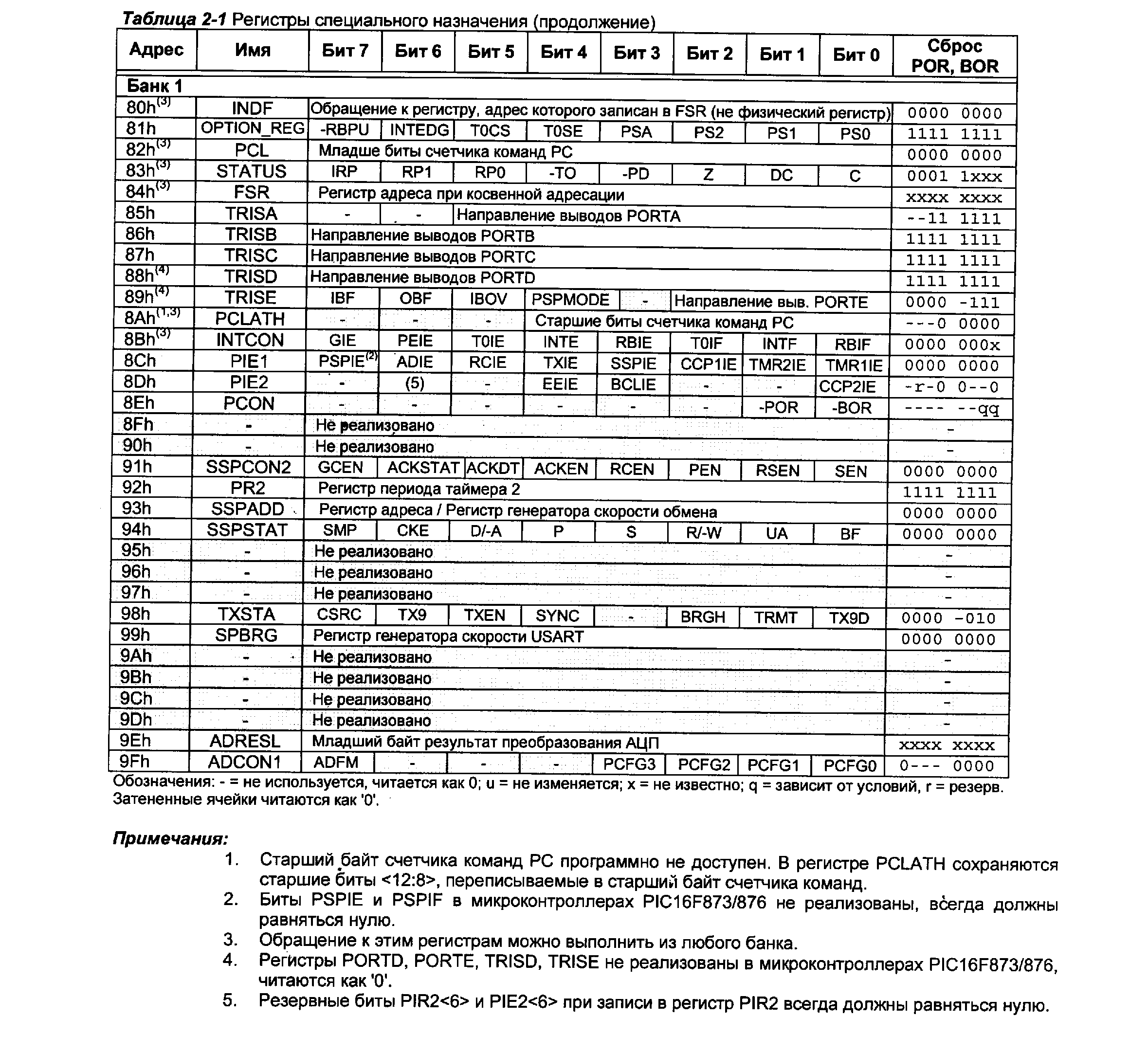

Память данных разделяется на 4 банка, которые содержат регистры общего и специального назначения (SFR). Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками. В Таблице приведено состояние управляющих битов при обращении к банкам памяти данных.

-

RP1:RP0

Банк

00

0

01

1

10

2

11

3

Объем памяти банков данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения, выполненные как статическое ОЗУ. Все реализованные банки содержат регистры специального назначения. Часто используемые регистры специального назначения могут отображаться и в других банках памяти.

Регистры общего назначения.

К регистрам общего назначения можно обращаться прямой или косвенной адресацией, через регистр FSR.

Регистры специального назначения

С помощью регистров специального назначения выполняется управления функциями ядра и периферийными модулями микроконтроллера. Регистры специального назначения реализованы как статическое ОЗУ. В этом разделе описаны регистры, управляющие функциями ядра микроконтроллера.