- •Оглавление

- •4. Таймеры

- •5. Память пик-контроллеров

- •2.1.Регистр status

- •2.2 Регистр option_reg

- •2.3.Регистры pclath и pcl

- •2.4.Косвенная адресация, регистры indf и fsr

- •3.Порты ввода/вывода

- •3.1.Регистры porta и trisa

- •3.2.Регистры portb и trisb

- •3.3.Регистры portс и trisс

- •3.4.Регистры portd и trisd

- •4.1.Модуль таймера tmr0

- •4.2.Модуль таймера tmr1

- •4.3. Модуль таймера tmr2

- •5.1.Организация памяти программ

- •5.2.Организация памяти данных

- •5.3.Eeprom память данных. Flash память программ.

- •5.4. Регистры eecon1, eecon2

- •5.5. Eeprom память данных..

- •6.Аналого-цифровой преобразователь

- •6.1. Регистры ацп

- •6.2.Порядок работы с ацп

- •6.2.1..Выбор источника тактовых импульсов для ацп

- •6.2.2.Настройка аналоговых входов

- •6.2.3.. Аналого-цифровое преобразование

- •6.2.4. Выравнивание результата преобразования

- •7.Прерывания микроконтроллеров

- •7.1.Регистры, используемые системой прерываний.

- •7.2.Внешнее прерывание с входа rb0/int

- •7.5. Сохранение контекста при обработке прерываний

- •8.Система команд

Оглавление

Введение 4

1. Микроконтроллеры. Архитектура ПИК-контроллеров

1.1. Характеристики микроконтроллеров

1.2. Устройство микроконтроллеров 1.3. Память микроконтроллеров

2. Регистры микроконтроллеров

2.1. Регистр STATUS

2.2. Регистр OPTION_REG

2.3. Регистры PCLATH и PCL

2.4.Косвенная адресация, регистры INDF и FSR

3. Порты ввода/вывода

3.1. Регистры PORTA и TRISA

3.2.Регистры PORTB и TRISB

3.3. Регистры PORTС и TRISС

3.4.Регистры PORTD и TRISD ……………………………………………

3.5.Регистры PORTE и TRISE …………………………………

4. Таймеры

4.1. Модуль таймера TMR0

4.2. Модуль таймера TMR1

4.3. Модуль таймера TMR2…………………………

5. Память пик-контроллеров

5.1. Организация памяти программ………………………………………

5.2. Организация памяти данных…………………………………………

5.3. EEPROM память данных. FLASH память программ.…………………

5.4. Регистры EECON1, EECON2……………………………………………

5.5. EEPROM память данных

5.6. FLASH память программ

6. Аналого-цифровой преобразователь.

6.1. Регистры АЦП

6.2. Порядок работы с АЦП

6.2.1. Выбор источника тактовых импульсов для АЦП

6.2.2. Настройка аналоговых входов

6.2.3. Аналого-цифровое преобразование

6.2.4. Выравнивание результата преобразования.

7. Прерывания микроконтроллеров

7.1. Регистры, используемые системой прерываний.

7.2. Внешнее прерывание с входа RB0/INT

7.3. Прерывание по переполнению таймера TMR0

7.4. Прерывание по изменению уровня сигнала на входе RB7:RB4

7.5. Сохранение контекста при обработке прерываний.

8. Система команд.

Литература

1.Микроконтроллеры. Архитектура ПИК-контроллеров.

Название PIC-контроллеры происходит от Programmable Input/output Controller. PIC16CXX – это 8-разрядные микроконтроллеры с RISC архитектурой, производимых фирмой Microchip Technology. Эти контроллеры отличаются низкой ценой, низким энергопотреблением и высокой скоростью. Микроконтроллеры имеют встроенное ЭППЗУ программы, ОЗУ данных и выпускаются в 18, 28 и 40 выводных корпусах.

Различные конструкции – однократно программируемые пользователем контроллеры, предназначенные для полностью оттестированных и законченных изделий. Выпускаются в дешевых пластмассовых корпусах с предварительно заданным типом внешнего генератора – кварцевым или RC.

Для отладки программ и макетирования выпускается вариант контроллеров с ультрафиолетовым стиранием. Допускают большое число циклов стирания/записи и имеют очень малое время стирания – 1-2 мин. Цена выше.

Для изделий, программа которых может меняться или содержит какие-либо переменные части, таблицы, параметры калибровки, ключи и т.д. выпускается электрически стираемый и перепрограммируемый контроллер. Он также содержит электрически перепрограммируемое ПЗУ данных.

Микроконтроллеры семейства PIC имеют очень эффективную систему команд, состоящую из 35 инструкций. Все инструкции выполняются за один цикл, кроме условных переходов. Один цикл выполнения инструкции состоит из 4 периодов тактовой частоты. Каждая инструкция состоит из 14 бит, делящихся на код операции и операнд.

Высокая скорость выполнения команд достигается за счет использования двухшинной Гарвардской архитектуры вместо одношинной Фон-Неймановской. Гарвардская архитектура основывается на наборе регистров с разделенными шинами и адресным пространством для команд и для данных. Набор регистров означает, что все программные объекты, такие как порты ввода/вывода, ячейки памяти и таймер, представляют собой физически реализованные аппаратные регистры.

Память данных (ОЗУ) имеет разрядность 8 бит, память программ (ППЗУ) имеет разрядность 12 или 14 бит. Использование Гарвардской архитектуры позволяет достичь высокой скорости выполнения битовых, байтовых и регистровых операций. Кроме того, Гарвардская архитектура допускает конвейерное выполнение инструкций, когда одновременно выполняется текущая инструкция и считывается следующая.

1.1.Характеристики микроконтроллеров.

Высокоскоростная RISC архитектура с набором команд из 35 инструкций.

Все команды выполнятся за один цикл, кроме команд переходов

Тактовая частота – 20 МГц, тактовый сигнал 200 нс, один машинный цикл.

До 8К х 14 слов FLASH памяти программ

До 368 х 8 байт памяти данных (ОЗУ) До 256 х 8 байт ЕЕPROM памяти данных

Система прерываний – до 14 источников

8-уровневый аппаратный стек

Прямой, косвенный и относительный режим адресации

Сброс по включению питания (POR)

Таймер сброса (PWRT) и таймер ожидания запуска генератора (OST) после включения питания

Сторожевой таймер WDT с собственным RC генератором Программируемая защита памяти программ

Режим энергосбережения SLEEP Выбор параметров тактового генератора Высокоскоростная, энергосберегающая CMOS FLASH/EEPROM технология

Полностью статическая архитектура

Программирование в готовом устройстве

Режим внутрисхемной отладки

Широкий диапазон напряжений питания от 2 до 5 В Повышенная нагрузочная способность портов ввода/вывода 25 мА.

Малое энергопотребление

Периферийные модули: Таймер 0: 8-разрядный таймер/счетчик с 8-разрядным программируемым предделителем

Таймер 1: 16-разрядный таймер/счетчик с 8 разрядным программируемым предделителем и выходным делителем

Таймер 2: 8-разрядный таймер/счетчик с 8-разрядным программируемым предделителем и выходным делителем

Два модуля сравнение/захват/ ШИМ (ССР)

Многоканальное 10-разрядное АЦП

Последовательный синхронный порт MSSP

- ведущий/ведомый режим SPI - ведущий/ведомый режим I2C

Последовательный синхронно-асинхронный приемопередатчик USART с поддержкой детектирования адреса

Ведомый 8-разрядный параллельный порт PSP с поддержкой внешних сигналов RD, WR, CS

Детектор пониженного напряжения (BOD) для сброса по снижению напряжения питания (BOR)

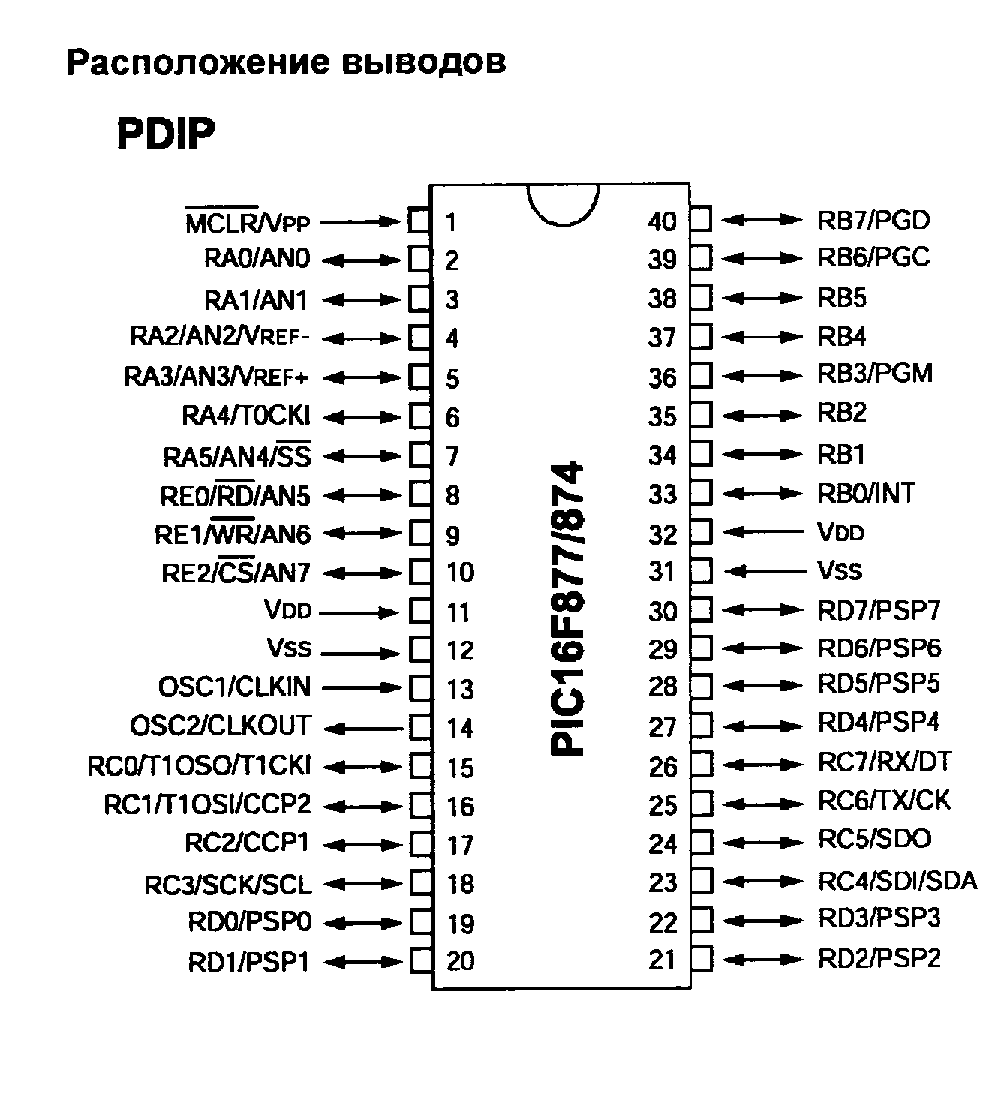

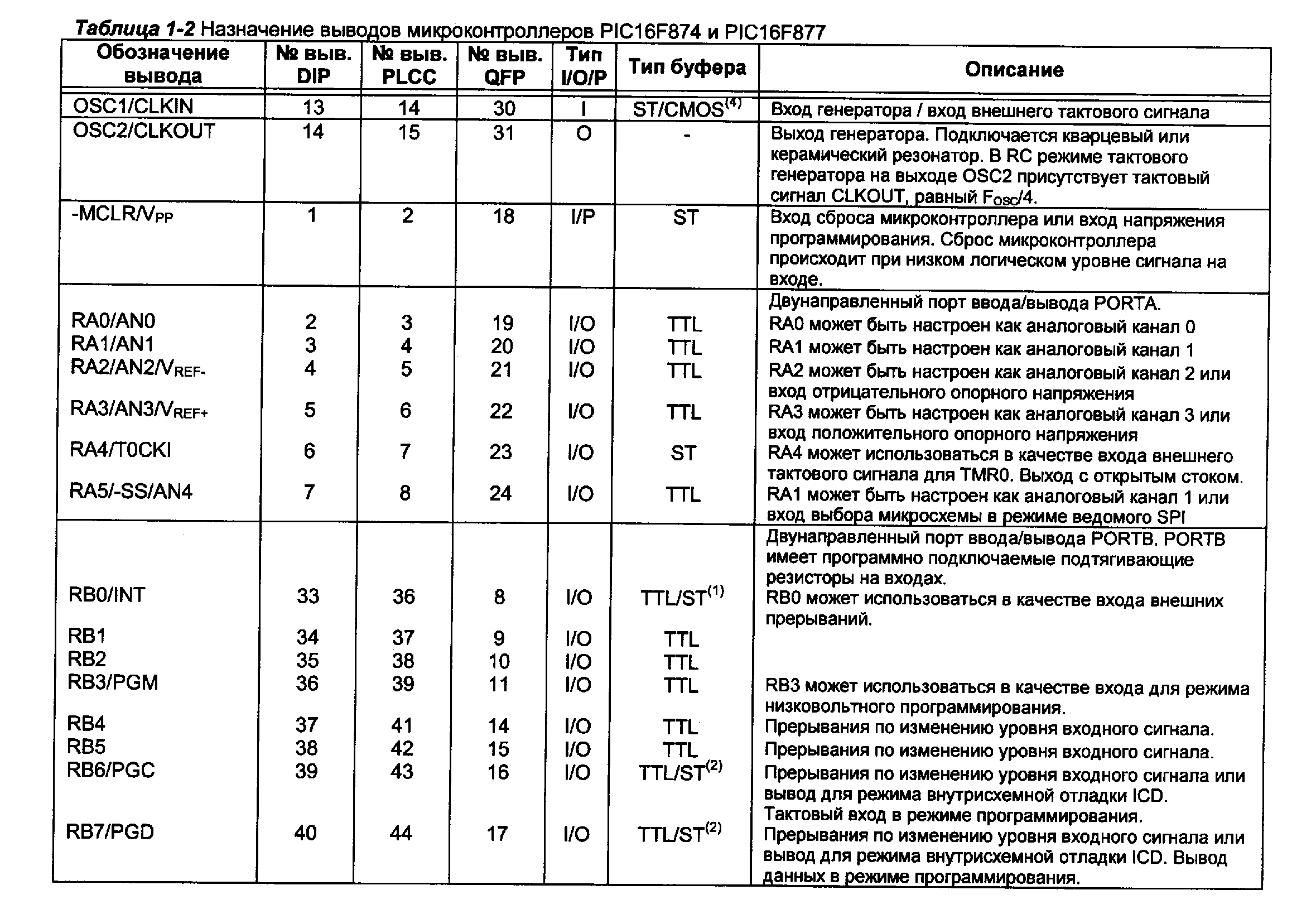

Рис.1.1. Схема расположения

выводов микроконтроллера.

Рис.1.1. Схема расположения

выводов микроконтроллера.

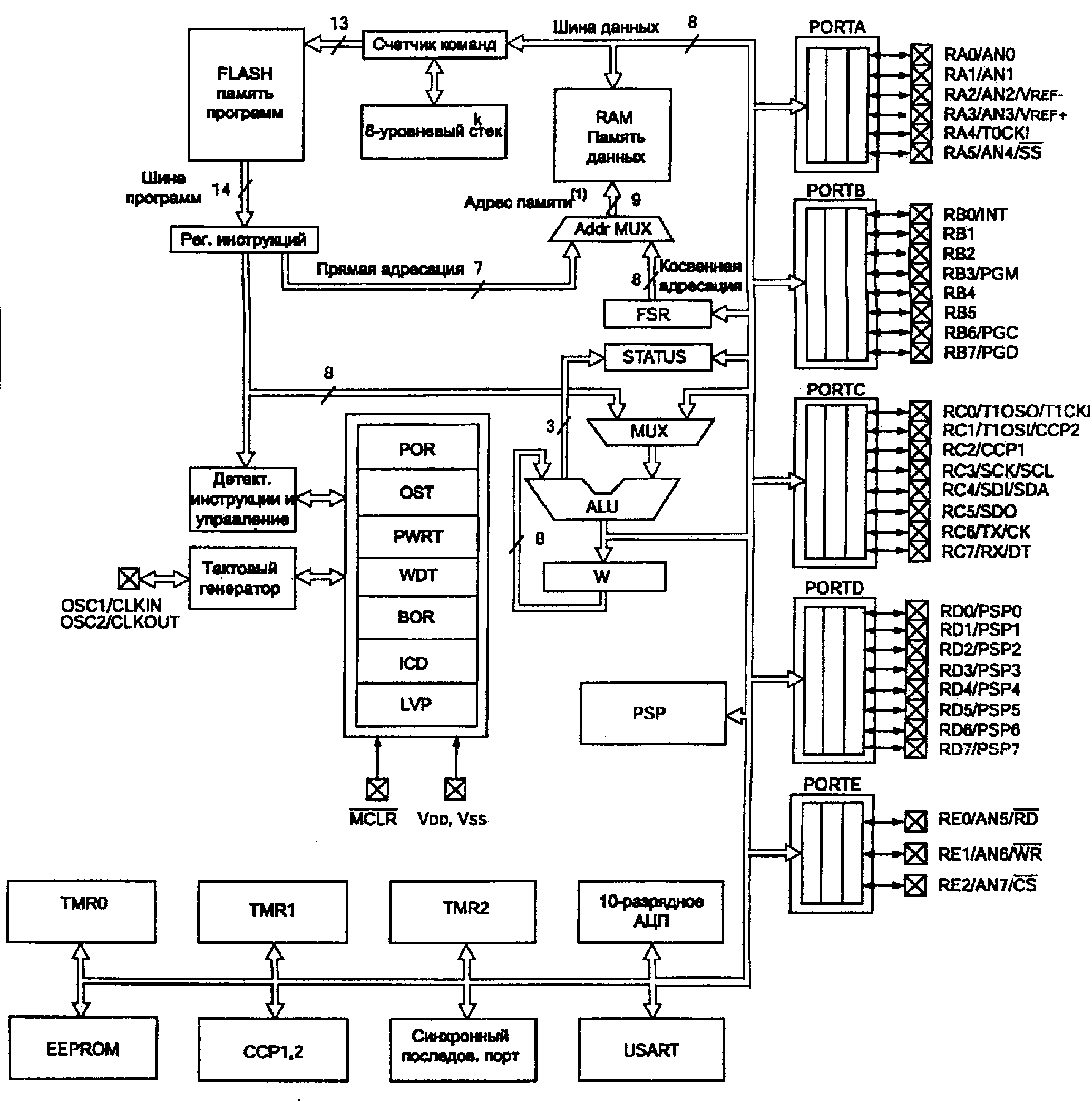

1.2.Устройство микроконтроллера

Микроконтроллер состоит из регистров, 8-разрядной шины данных, 13-разрядной адресной шины, 14-разрядной шины программ, арифметико-логического устройства, регистра аккумулятора W, памяти программ, памяти данных, которая состоит из регистров общего назначения и регистров специального назначения, регистра инструкций, регистра признаков STATUS, регистра косвенной адресации FSR, дешифратора инструкций и устройства управления, тактового генератора, портов ввода/вывода A,B,C,D,E, таймеров, АЦП, последовательных и параллельных портов, перепрограммируемой памяти данных, 8-уровневого стека данных.

Рис.1.2. Блок-схема микроконтроллера.

Принцип работы микроконтроллера аналогичен работе микропроцессоров. В счетчик команд загружается адрес ячейки памяти, где находится первая команда программы. Адрес по 13-разрядной шине адреса поступает в память программ. Первая команда извлекается из памяти и по шине программ поступает в регистр инструкций. Из регистра инструкций код операции поступает в детектор инструкций и устройство управления. Инструкция декодируется и устройство управления начинает ее выполнять.

1.3. Память микроконтроллеров.

Особый интерес представляет организация памяти в микроконтроллерах. В микроконтроллерах три вида памяти: память программ, память данных и ЕЕPROM памяти данных. Память программ и память данных имеют раздельные шины данных и адреса, что позволяет выполнять параллельный доступ.

Организация памяти программ

Микроконтроллеры имеют 13-разрядный счетчик команд РС, способный адресовать 8К х 14 слов памяти программ. Физически реализовано FLASH памяти 8К х 14 для PIC16F877. Обращение к физически нереализованной памяти программ приведет к адресации реализованной памяти.

Адрес вектора сброса – 0000h. Адрес вектора прерываний – 0004h.

Память программ состоит из 4-х страниц: страница 0, страница 1, страница 2, страница 3.

Страница 0 имеет адреса: 0005h-07FFh.

-

0800h-0FFFh.

-

1000h-17FFh

-

1800h-1FFFh

Рис.1.3. Организация памяти программ.

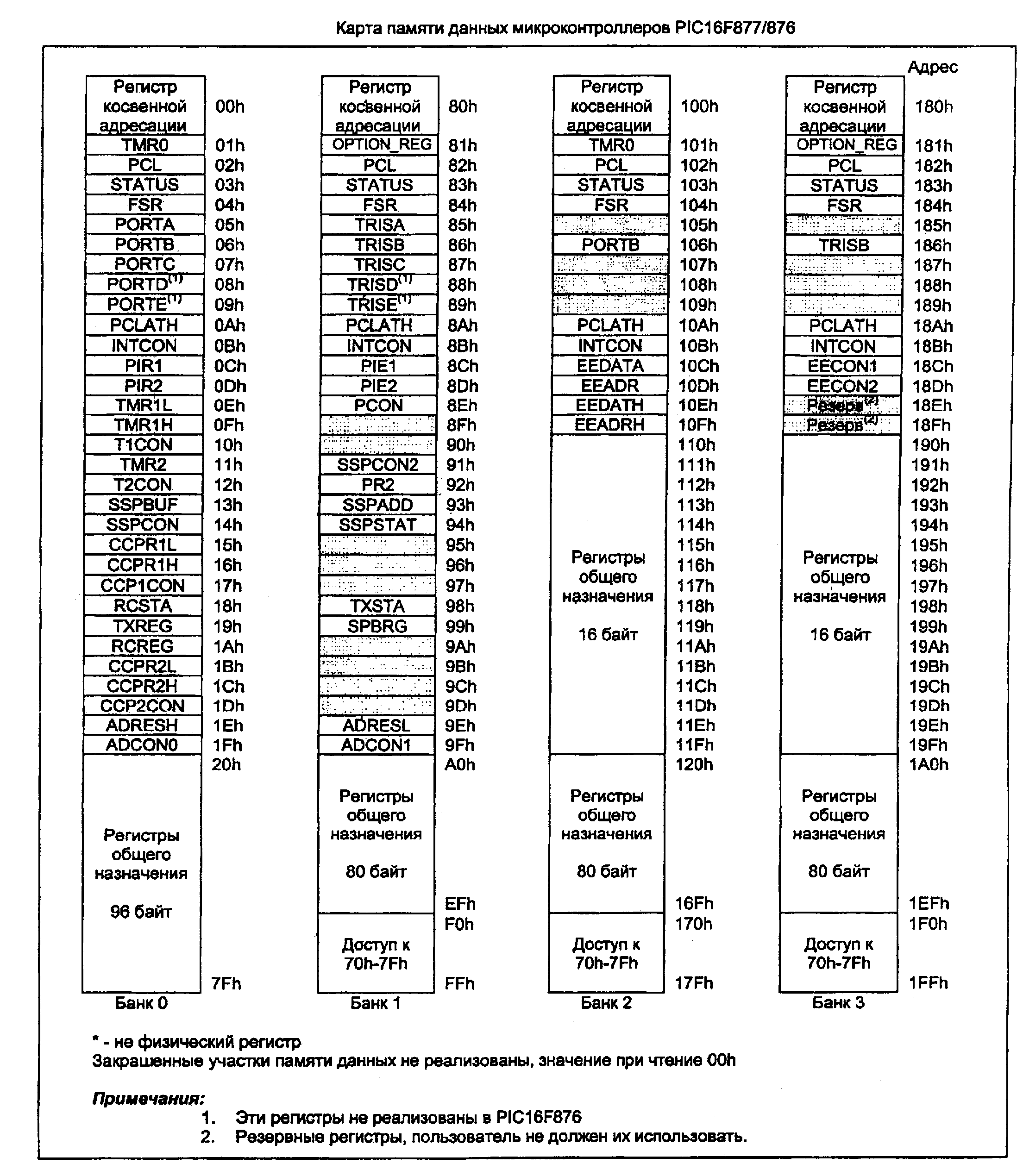

Организация памяти данных

Память данных разделяется на 4 банка, которые содержат регистры общего и специального назначения (SFR). Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками. В Таблице приведено состояние управляющих битов при обращении к банкам памяти данных.

-

RP1:RP0

Банк

00

0

01

1

10

2

11

3

Объем памяти банков данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения, выполненные как статическое ОЗУ. Все реализованные банки содержат регистры специального назначения. Часто используемые регистры специального назначения могут отображаться и в других банках памяти.

Регистры общего назначения.

К регистрам общего назначения можно обращаться прямой или косвенной адресацией, через регистр FSR.

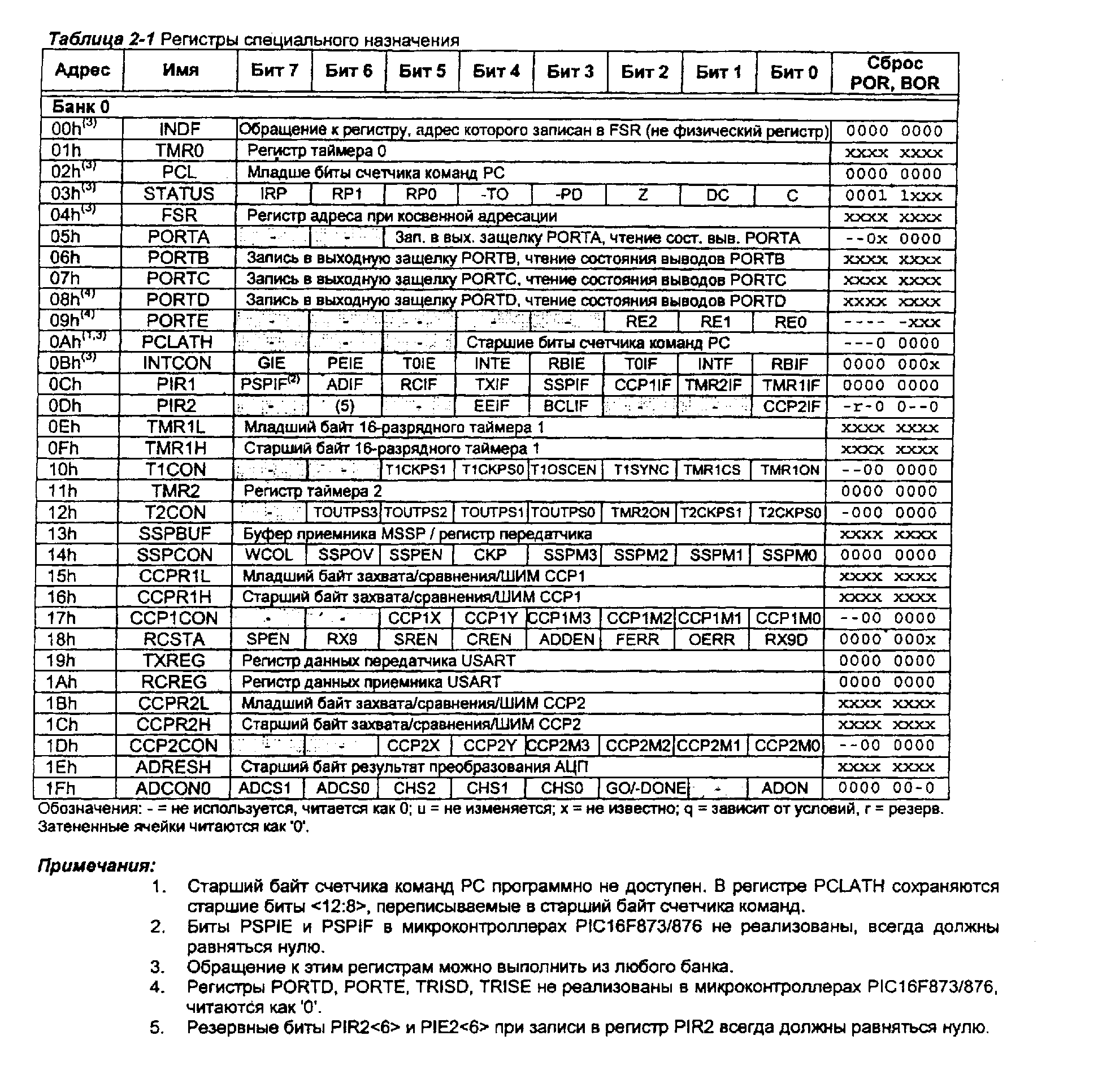

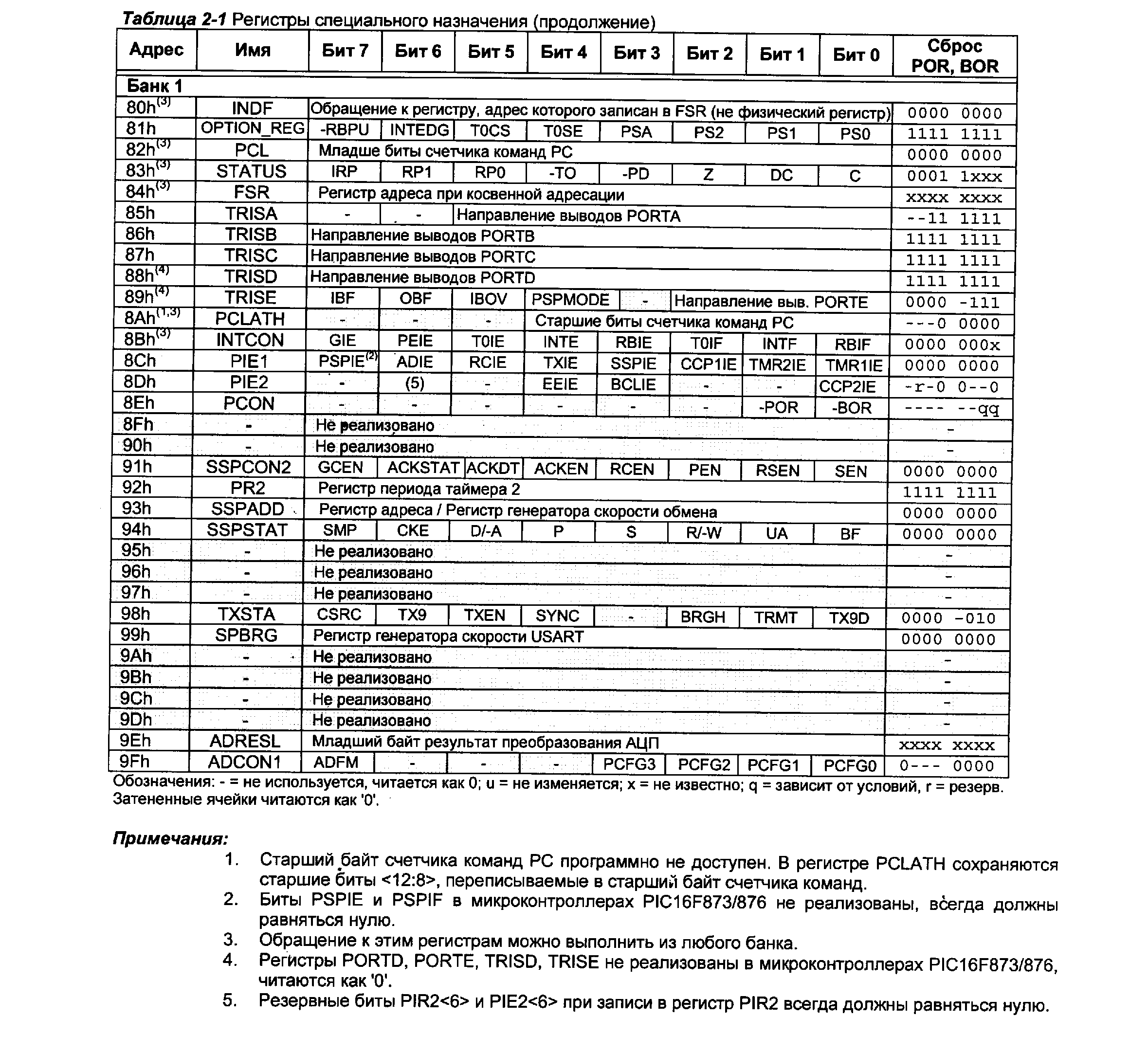

Регистры специального назначения

С помощью регистров специального назначения выполняется управления функциями ядра и периферийными модулями микроконтроллера. Регистры специального назначения реализованы как статическое ОЗУ. В этом разделе описаны регистры, управляющие функциями ядра микроконтроллера.

2.Регистры ПИК-контроллера