- •ADSP-TS101S

- •KEY FEATURES

- •KEY BENEFITS

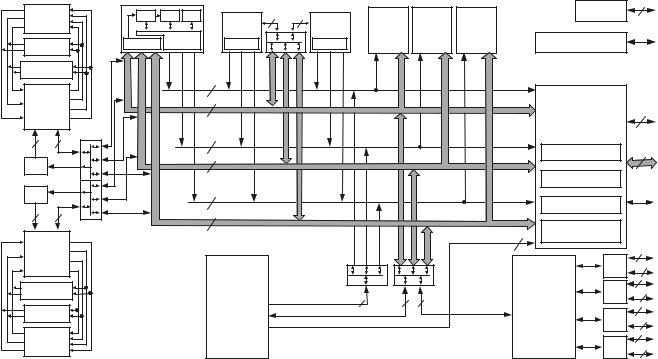

- •FUNCTIONAL BLOCK DIAGRAM

- •TABLE OF CONTENTS

- •GENERAL DESCRIPTION

- •Figure 1. Single Processor System with External SDRAM

- •Dual Compute Blocks

- •Data Alignment Buffer (DAB)

- •Dual Integer ALUs (IALUs)

- •Program Sequencer

- •Interrupt Controller

- •Flexible Instruction Set

- •On-Chip SRAM Memory

- •Figure 2. Memory Map

- •External Port (Off-Chip Memory/Peripherals Interface)

- •Host Interface

- •Multiprocessor Interface

- •Figure 3. Shared Memory Multiprocessing System

- •SDRAM Controller

- •EPROM Interface

- •DMA Controller

- •Link Ports

- •Timer and General-Purpose I/O

- •Reset and Booting

- •Figure 4. Power-up Reset Waveform

- •Low Power Operation

- •Clock Domains

- •Power Supplies

- •Filtering Reference Voltage and Clocks

- •Figure 5. VREF, SCLK_N, and LCLK_N Filter

- •Development Tools

- •Target Board Header

- •Figure 6. JTAG Target Board Connector for JTAG Equipped Analog Devices DSP (Jumpers in Place)

- •Figure 7. JTAG Target Board Connector with No Local Boundary Scan

- •JTAG Emulator Pod Connector

- •Figure 8. JTAG Pod Connector Dimensions

- •Figure 9. JTAG Pod Connector Keep-Out Area

- •Design for Emulation Circuit Information

- •Additional Information

- •PIN FUNCTION DESCRIPTIONS

- •STRAP PIN FUNCTION DESCRIPTIONS

- •SPECIFICATIONS

- •RECOMMENDED OPERATING CONDITIONS

- •ELECTRICAL CHARACTERISTICS

- •ABSOLUTE MAXIMUM RATINGS

- •ESD SENSITIVITY

- •TIMING SPECIFICATIONS

- •General AC Timing

- •Figure 10. General AC Parameters Timing

- •Link Ports Data Transfer and Token Switch Timing

- •Figure 11. Link Ports—Transmit

- •Figure 12. Link Ports—Receive

- •Figure 13. Link Ports—Token Switch, Token Master

- •Figure 14. Link Ports—Token Switch, Token Requester

- •Output Drive Currents

- •Power Dissipation

- •Test Conditions

- •Figure 24. Output Enable/Disable

- •Output Disable Time

- •Output Enable Time

- •Capacitive Loading

- •Figure 25. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

- •Environmental Conditions

- •Thermal Characteristics

- •OUTLINE DIMENSIONS

- •484-Ball PBGA (B-484)

- •625-Ball PBGA (B-625)

- •ORDERING GUIDE

- •484-BALL PBGA PIN CONFIGURATIONS

- •484-Ball PBGA Pin Configurations (Top View, Summary)

- •625-BALL PBGA PIN CONFIGURATIONS

- •625-Ball PBGA Pin Configurations (Top View, Summary)

a |

DSP MicrocomputerT |

|

ADSP-TS101S |

KEY FEATURES |

KEY BENEFITS |

250 MHz, 4.0 ns Instruction Cycle Rate |

Provides High Performance Static Superscalar DSP |

6M Bits of Internal—On-Chip—SRAM Memory |

Operations, Optimized for Telecommunications |

19 19 mm (484-Ball) or 27 27 mm (625-Ball) PBGA |

Infrastructure and Other Large, Demanding |

Package |

Multiprocessor DSP Applications |

Dual Computation Blocks—Each Containing an ALU, a |

Performs Exceptionally Well on DSP Algorithm and I/O |

Multiplier, a Shifter, and a Register File |

Benchmarks (See Benchmarks in Table 1 and Table 2) |

Dual Integer ALUs, Providing Data Addressing and |

Supports Low Overhead DMA Transfers Between |

Pointer Manipulation |

Internal Memory, External Memory, Memory-Mapped |

Integrated I/O Includes 14 Channel DMA Controller, |

Peripherals, Link Ports, Host Processors, and Other |

External Port, Four Link Ports, SDRAM Controller, |

(Multiprocessor) DSPs |

Programmable Flag Pins, Two Timers, and Timer |

Eases DSP Programming Through Extremely Flexible |

Expired Pin for System Integration |

Instruction Set and High Level Language Friendly DSP |

1149.1 IEEE Compliant JTAG Test Access Port for |

Architecture |

On-Chip Emulation |

Enables Scalable Multiprocessing Systems with Low |

On-Chip Arbitration for Glueless Multiprocessing with |

Communications Overhead |

up to Eight TigerSHARC® DSPs on a Common Bus |

|

FUNCTIONAL BLOCK DIAGRAM

COMPUTATIONAL BLOCKS

SHIFTER |

ALU |

MULTIPLIER |

X |

REGISTER |

FILE |

32x32 |

128 |

128 |

DAB |

|

DAB |

|

128 |

128 |

Y |

|

REGISTER |

|

FILE |

|

32x32 |

|

MULTIPLIER |

|

ALU |

|

SHIFTER |

|

PROGRAM SEQUENCER |

DATA ADDRESS GENERATION |

|

INTERNAL MEMORY |

|

|

|

|

6 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

JTAG PORT |

||

PC |

BTB IRQ |

INTEGER |

32 |

32 |

INTEGER |

MEMORY |

MEMORY |

MEMORY |

|

|

|||||

|

|

|

|

||||||||||||

|

|

|

|

|

M0 |

|

M1 |

|

M2 |

|

|

|

|

||

|

|

J ALU |

|

|

K ALU |

|

|

|

|

|

|

|

|||

|

ADDR |

|

|

64Kx32 |

64Kx32 |

64Kx32 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||||

IAB |

32x32 |

|

|

32x32 |

|

|

|

|

|

|

|

SDRAM CONTROLLER |

|

||

FETCH |

|

|

A |

D |

A |

D |

A |

D |

|

|

|||||

|

|

32 |

|

|

|

|

|

|

|

|

M0 ADDR |

EXTERNAL PORT |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

128 |

|

|

|

|

|

|

|

|

M0 DATA |

MULTIPROCESSOR |

|

|||

|

|

|

|

|

|

|

|

|

INTERFACE |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HOST INTERFACE |

|

|

|

|

32 |

|

|

|

|

|

|

|

|

M1 ADDR |

|

|

ADDR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

128 |

|

|

|

|

|

|

|

|

M1 DATA |

INPUT FIFO |

|

64 |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT BUFFER |

DATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

32 |

|

|

|

|

|

|

|

|

M2 ADDR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

M2 DATA |

OUTPUT FIFO |

|

|

|

|

128 |

|

|

|

|

|

|

|

|

|

|

CNTRL |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O ADDRESS |

32 |

CLUSTER BUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

ARBITER |

|

|

|||

|

|

I/O PROCESSOR |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DMA |

|

|

|

|

|

|

|

|

|

LINK PORT |

L0 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|||

|

|

CONTROLLER |

|

|

|

|

|

|

|

|

|

CONTROLLER |

|

||

|

|

|

|

DMA ADDRESS |

|

|

|

|

|

|

|

|

L1 |

8 |

|

|

|

|

|

32 |

256 |

|

256 |

LINK DATA |

|

LINK |

|

3 |

|||

|

|

|

|

DMA DATA |

|

|

|

|

|

PORTS |

|

||||

|

|

|

|

|

|

|

|

|

|

|

L2 |

8 |

|||

|

|

CONTROL/ |

|

|

|

|

|

|

|

|

|

CONTROL/ |

|||

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|||

|

|

STATUS/ |

|

|

|

|

|

|

|

|

|

STATUS/ |

|

||

|

|

TCBs |

|

|

|

|

|

|

|

|

|

BUFFERS |

L3 |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

TigerSHARC and the TigerSHARC logo are registered trademarks of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O.Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel:781/329-4700 |

www.analog.com |

Fax:781/326-8703 |

© Analog Devices, Inc., 2002 |