TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

H 3

H1

1 |

2 |

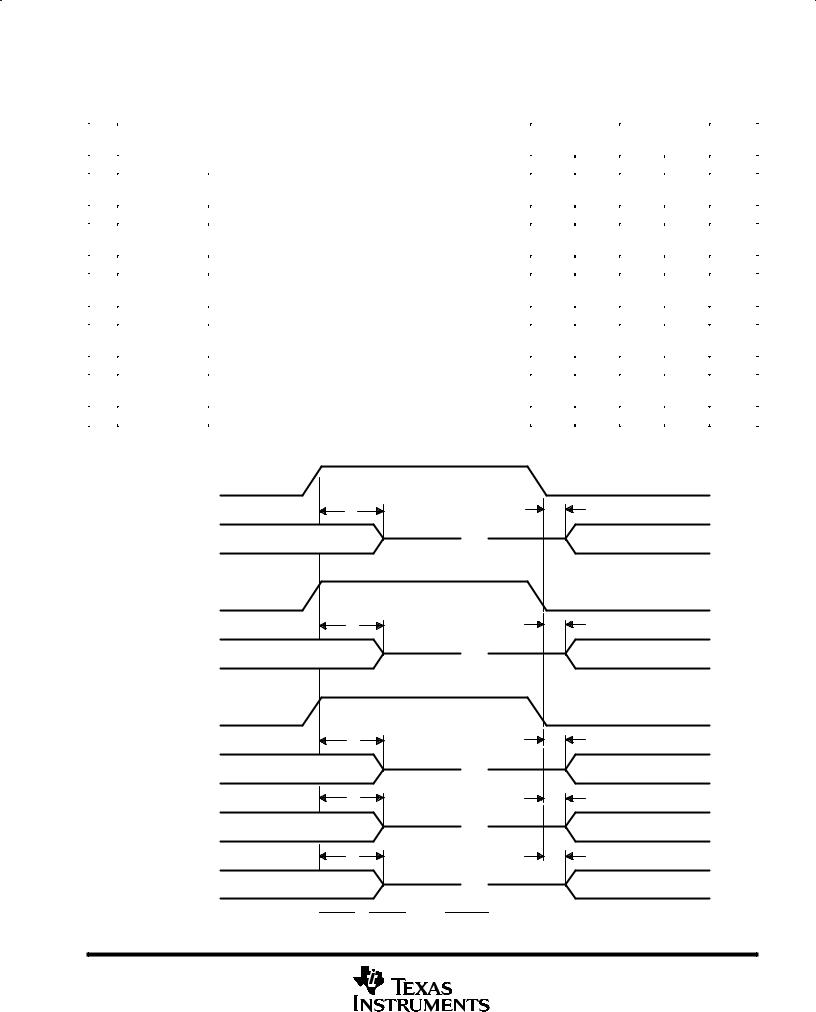

(L)STRBx

(L)R / Wx |

5 |

|

4 |

3

(L)Ax

6

(L)Dx

8

7

(L)RDYx

8.1

(L)STATx

Figure 9. Memory-Read-Cycle Timing [(L)STRBx = 0]

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

21 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

H3

H1 |

|

1 |

2 |

|

|

(L)STRBx |

|

3 |

9 |

(L)R / Wx |

|

4 |

12 |

(L)Ax |

|

10 |

11 |

(L)Dx |

|

|

8 |

(L)RDYx |

|

|

7 |

(L)STATx

Figure 10. Memory-Write-Cycle Timing [(L)STRBx = 0]

22 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPRS038 ± JANUARY 1996 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-, |

|

|

|

-, and |

|

|

|

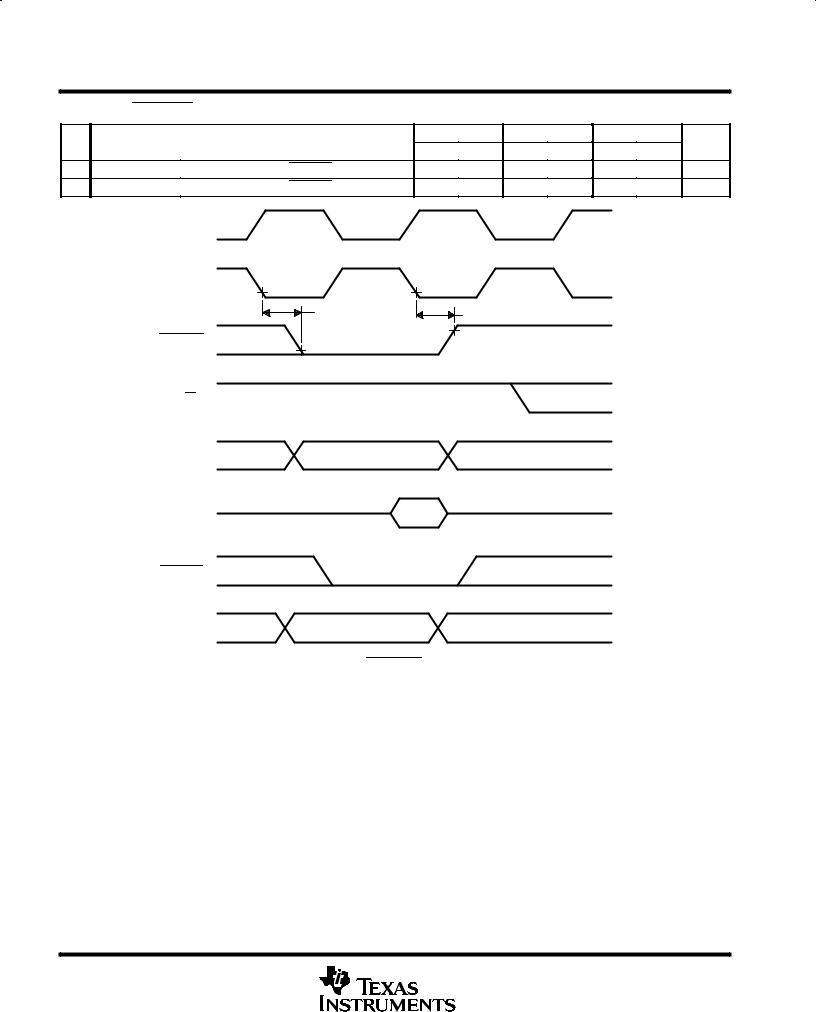

-enable timing (see Figure 11) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

(L)DE |

(L)AE |

(L)CEx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS320C40 - 40 |

TMS320C40 - 60 |

|

|

||||||||||

|

|

NO. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS320C40 - 50 |

UNIT |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MIN |

MAX |

MIN |

MAX |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Delay time, |

|

|

|

|

high to (L)D0 ± (L)D31 in the high-impedance |

|

|

0² |

|

|

15³ |

0² |

15³ |

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

1 |

t |

(L)DE |

|

|

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

d(DEH - DZ) |

state |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

2 |

td(DEL - DV) |

Delay time, |

|

|

|

|

low to (L)D0 ± (L)D31 valid |

|

|

|

|

0² |

|

|

21 |

0² |

16 |

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||

|

|

(L)DE |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Delay time, |

|

|

|

|

high to (L)A0 ± (L)A30 in the high-impedance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

3 |

td(AEH - AZ) |

(L)AE |

|

|

0² |

|

|

15³ |

0² |

15³ |

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

state |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

4 |

t |

Delay time, |

|

|

low to (L)A0 ± (L)A30 valid |

|

|

|

|

0² |

|

|

18 |

0² |

16 |

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

|

(L)AE |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

d(AEL - AV) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Delay time, |

|

|

|

|

|

|

high to (L)R / |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

5 |

td(CEH - RWZ) |

(L)CEx |

|

W0, (L)R / W1 in the |

|

|

|

|

0² |

|

|

15³ |

0² |

15³ |

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||

|

|

high-impedance state |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

6 |

td(CEL - RWV) |

Delay time, |

|

|

|

|

|

|

low to (L)R / |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0² |

|

|

21 |

0² |

16 |

ns |

|

|||||||||||||||||||||||||||

|

|

(L)CEx |

W0, (L)R / W1 valid |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Delay time, |

|

|

|

|

|

|

high to |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

in the |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

7 |

td(CEH - SZ) |

(L)CEx |

(L)STRB0, |

|

|

|

(L)STRB1 |

|

|

0² |

|

|

15³ |

0² |

15³ |

ns |

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

|

high-impedance state |

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

8 |

td(CEL - SV) |

Delay time, |

|

|

|

|

|

|

low to |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

valid |

|

|

|

|

0² |

|

|

21 |

0² |

16 |

ns |

|

||||||||||||||||||||||

|

|

(L)CEx |

(L)STRB0, |

|

|

(L)STRB1 |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Delay time, |

|

|

|

|

|

|

high to (L)PAGE0, (L)PAGE1 in the |

|

|

0² |

|

|

15³ |

0² |

15³ |

|

|

|||||||||||||||||||||||||||||||||||||

|

|

9 |

t |

(L)CEx |

|

|

|

|

ns |

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

d(CEH - PAGEZ) |

high-impedance state |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

10 |

td(CEL - PAGEV) |

Delay time, |

|

|

|

|

|

|

low to (L)PAGE0, (L)PAGE1 valid |

|

|

|

|

0² |

|

|

21 |

0² |

16 |

ns |

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

(L)CEx |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

² |

This value is specified by design but not tested. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||

³ |

This value is characterized but not tested. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(L)DE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

(L)Dx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hi-Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(L)AE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

(L)Ax |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hi-Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(L)CEx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

(L)R / |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Wx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hi-Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(L)STRBx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hi-Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

(L)PAGEx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Hi-Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

Figure 11. (L)DE -, (L)AE -, and (L)CEx-Enable Timings

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

23 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

timing for (L)LOCK when executing LDFI or LDII (see Figure 12)

NO. |

|

|

|

TMS320C40 - 40 |

TMS320C40 - 50 |

TMS320C40 - 60 |

UNIT |

|

|

|

|

|

|

|

|

||

|

|

|

MIN |

MAX |

MIN MAX |

MIN MAX |

||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

1 |

td(H1L - LOCKL) Delay time, H1 low to |

|

low |

|

11 |

8 |

8 |

ns |

(L)LOCK |

|

|||||||

LDFI or LDII

External Access

H3

H1

(L)STRBx

(L)R / Wx

(L)Ax

(L)Dx

(L)RDYx

1

(L)LOCK

Figure 12. Timing for (L)LOCK When Executing LDFI or LDII

24 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

timing for (L)LOCK when executing STFI or STII (see Figure 13)

NO. |

|

|

|

TMS320C40 - 40 |

TMS320C40 - 50 |

TMS320C40 - 60 |

UNIT |

|

|

|

|

|

|

|

|

||

|

|

|

MIN |

MAX |

MIN MAX |

MIN MAX |

||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

1 |

td(H1L - LOCKH) Delay time, H1 low to |

|

high |

|

11 |

8 |

8 |

ns |

(L)LOCK |

|

|||||||

STFI or STII

External Access

H3

H1

(L)STRBx

(L)R / Wx

(L)Ax

(L)Dx

(L)RDYx

1

(L)LOCK

Figure 13. Timing for (L)LOCK When Executing STFI or STII

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

25 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

timing for (L)LOCK when executing SIGI (see Figure 14)

NO. |

|

TMS320C40 - 40 TMS320C40 - 50 |

TMS320C40 - 60 |

UNIT |

||||

|

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

||

|

|

|

||||||

1 |

td(H1L - LOCKL) |

Delay time, H1 low to (L)LOCK low |

11 |

|

8 |

|

8 |

ns |

2 |

td(H1L - LOCKH) |

Delay time, H1 low to (L)LOCK high |

11 |

|

8 |

|

8 |

|

|

|

H 3 |

|

|

|

|

|

|

|

|

H1 |

|

|

|

|

|

|

|

|

1 |

2 |

|

|

|

|

|

(L)LOCK

(L)R / Wx

(L)Ax

(L)Dx

(L)RDYx

(L)STATx

Figure 14. Timing for (L)LOCK When Executing SIGI

26 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

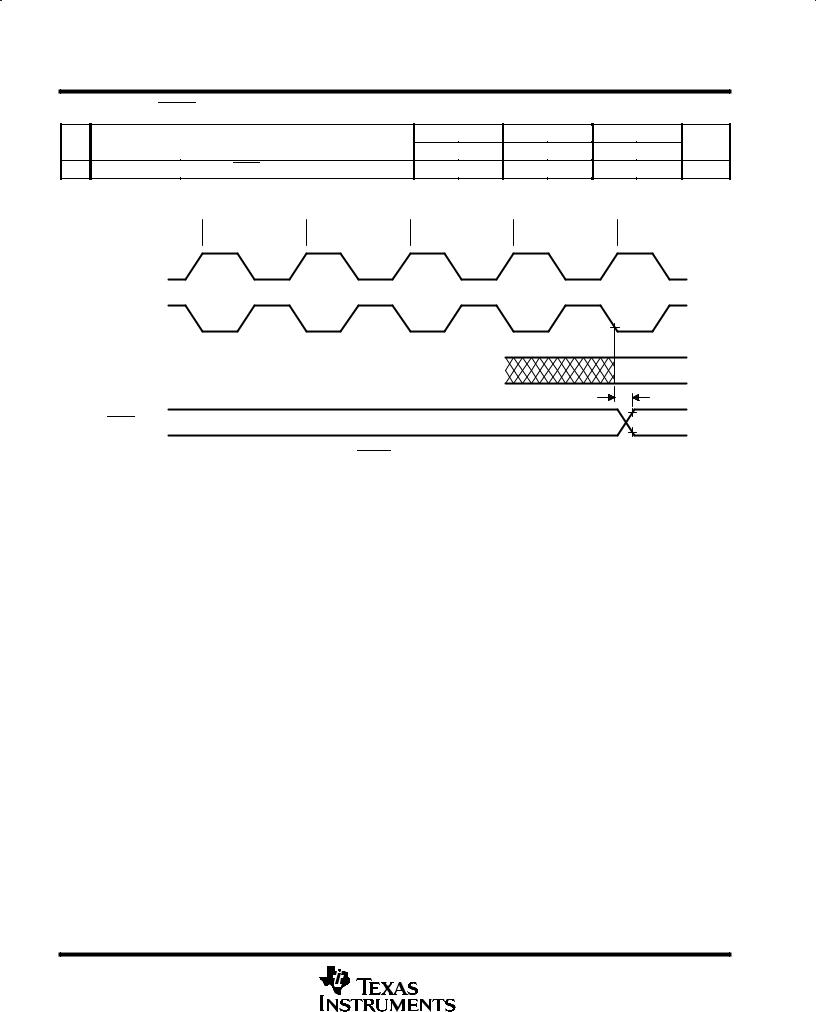

timing for (L)PAGE0, (L)PAGE1 during memory access to a different page (see Figure 15)

|

|

TMS320C40 - 40 |

TMS320C40 - 60 |

|

||

NO. |

|

TMS320C40 - 50 |

UNIT |

|||

|

|

|

||||

|

|

|

|

|

||

|

|

MIN |

MAX |

MIN |

MAX |

|

1 td(H1L - PAGEH) |

Delay time, H1 low to (L)PAGEx high for access to different page |

0 |

9 |

0 |

8 |

ns |

2 td(H1L - PAGEL) |

Delay time, H1 low to (L)PAGEx low for access to different page |

0 |

9 |

0 |

8 |

ns |

H1 |

|

|

|

|

|

|

(L)R / Wx |

|

|

|

|

|

|

(L)STRBx |

|

|

|

|

|

|

(L)RDYx

1 |

2 |

1 |

2 |

(L)PAGEx

(L)Dx

(L)Ax

(L)STATx |

(L)STRB1 write to a different page |

(L)STRB1 read from a different page |

Figure 15. (L)PAGE0, (L)PAGE1 Timing Cycle, Memory Access to a Different Page

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

27 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

timing for the IIOFx when configured as an output (see Figure 16)

NO. |

|

TMS320C40 - 40 TMS320C40 - 50 |

TMS320C40 - 60 |

UNIT |

||||

|

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

||

|

|

|

||||||

1 tv(H1L - IIOF) |

H1 low to IIOFx valid |

|

16 |

|

14 |

|

14 |

ns |

|

Fetch Load |

Decode |

Read |

|

Execute |

|

|

|

|

Instruction |

|

|

|

|

|||

H3 |

|

|

|

|

|

|

|

|

H1 |

|

|

|

|

|

|

|

|

FLAGx (IIF Register) |

|

|

|

|

|

|

1 or 0 |

|

|

|

|

|

|

|

|

1 |

|

IIOFx Pins |

|

|

|

|

|

|

|

|

Figure 16. Timing for the IIOFx When Configured as an Output

28 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

|

|

|

|

|

SPRS038 ± JANUARY 1996 |

|

timing of IIOFx changing from output to input mode (see Figure 17) |

|

|

||||

|

|

|

|

TMS320C40 - 40 |

TMS320C40 - 60 |

|

NO. |

|

|

|

TMS320C40 - 50 |

UNIT |

|

|

|

|

|

|||

|

|

|

|

|

||

|

|

|

|

MIN MAX |

MIN MAX |

|

1 |

th(H1L - IIOF) |

Hold time, IIOFx after H1 low |

|

14² |

14² |

ns |

2 |

tsu(IIOF-H1L) |

Setup time, IIOFx before H1 low |

|

11 |

11 |

ns |

3 |

th(H1L-IIOF) |

Hold time, IIOFx after H1 low |

|

0 |

0 |

ns |

² This value is specified by design but not tested. |

|

|

|

|

||

|

|

Execute |

Buffers Go |

Synchronizer |

Value on IIOF |

|

|

|

Load of IIF |

From Output |

|

||

|

|

Delay |

Seen in IIF |

|

||

|

|

Register |

to Input |

|

||

|

|

|

|

|

||

|

H3 |

|

|

|

|

|

|

H1 |

|

|

|

|

|

|

|

|

|

2 |

|

|

|

TYPEx |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

(IIF Register) |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

IIOFx |

Output |

|

|

|

|

|

FLAGx |

|

Data |

|

|

|

|

(IIF Register) |

|

|

|

|

|

|

|

Sampled |

|

|

|

|

Data

Seen

Figure 17. Change of IIOFx From Output to Input Mode

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

29 |

TMS320C40

DIGITAL SIGNAL PROCESSOR

SPRS038 ± JANUARY 1996

timing of IIOFx changing from input to output mode (see Figure 18)

NO. |

|

|

|

|

|

|

|

|

|

|

|

TMS320C40 - 40 |

TMS320C40 - 50 |

TMS320C40 - 60 |

UNIT |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Delay time, H1 low to |

|

|

switching from input to |

|

|

|

|

|

|

|

||||||

1 |

td(H1L - IFIO) |

IIOFx |

|

16 |

|

14 |

|

14 |

ns |

|||||||||

output |

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Execution of |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Load of IIF |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

H3 |

|

|

|

|

|

|

|

|

|

|||||||

H1

TYPEx

(IIF Register)

1

IIOFx

Figure 18. Change of IIOFx From Input to Output Mode

RESET timing (see Figure 19)

NO. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS320C40 - 40 |

TMS320C40 - 50 |

TMS320C40 - 60 |

UNIT |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

1 |

tsu(RESET-C1L) |

Setup time for |

|

|

|

|

before CLKIN low |

11 |

tc(CI)² |

11 |

tc(CI)² |

11 |

tc(CI)² |

ns |

||||||||

RESET |

||||||||||||||||||||||

2.1 |

td(CIH - H1H) |

Delay time, CLKIN high to H1 high |

|

3 |

10 |

2 |

10 |

2 |

10 |

ns |

||||||||||||

2.2 |

td(CIH - H1L) |

Delay time, CLKIN high to H1 low |

|

|

3 |

10 |

2 |

10 |

2 |

10 |

ns |

|||||||||||

|

|

Setup time for |

|

|

|

|

high before H1 low |

|

|

|

|

|

|

|

||||||||

3 |

tsu(RESETH - H1L) |

RESET |

13 |

|

13 |

|

13 |

|

ns |

|||||||||||||

and after ten H1 clock cycles |

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

4.1 |

td(CIH - H3L) |

Delay time, CLKIN high to H3 low |

|

|

3 |

10 |

2 |

10 |

2 |

10 |

ns |

|||||||||||

4.2 |

td(CIH - H3H) |

Delay time, CLKIN high to H3 high |

|

3 |

10 |

2 |

10 |

2 |

10 |

ns |

||||||||||||

5 |

t |

Delay time, H1 high |

to |

(L)Dx |

in |

the |

|

13³ |

|

13³ |

|

13³ |

ns |

|||||||||

|

d(H1H - DZ) |

high-impedance state |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

6 |

td(H3H - AZ) |

Delay time, H3 high |

to |

(L)Ax |

in |

the |

|

9³ |

|

9³ |

|

9³ |

ns |

|||||||||

high-impedance state |

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

7 |

td(H3H - CONTROLH) |

Delay time, H3 high to control signals high |

|

9³ |

|

9³ |

|

9³ |

ns |

|||||||||||||

[low for (L)PAGE] |

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

9³ |

|

9³ |

|

9³ |

|

|||||||

8 |

td(H1H - IACKH) |

Delay time, H1 high to |

IACK |

high |

|

|

|

|

|

ns |

||||||||||||

|

|

Delay time, |

|

|

|

|

low to asynchronous |

|

|

|

|

|

|

|

||||||||

9 |

td(RESETL - ASYNCH) |

RESET |

|

21³ |

|

21³ |

|

21³ |

ns |

|||||||||||||

reset signals in the high-impedance state |

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

Delay time, |

|

|

|

|

high to asynchronous |

|

15³ |

|

15³ |

|

15³ |

|

||||||||

10 |

t |

RESET |

|

|

|

ns |

||||||||||||||||

|

d(RESETH - COMMH) |

reset signals high |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

² tc(CI), the CLKIN period as shown in Figure 7 ³ This value is characterized but not tested.

30 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |