Методичка КР ПТЦА

.pdf

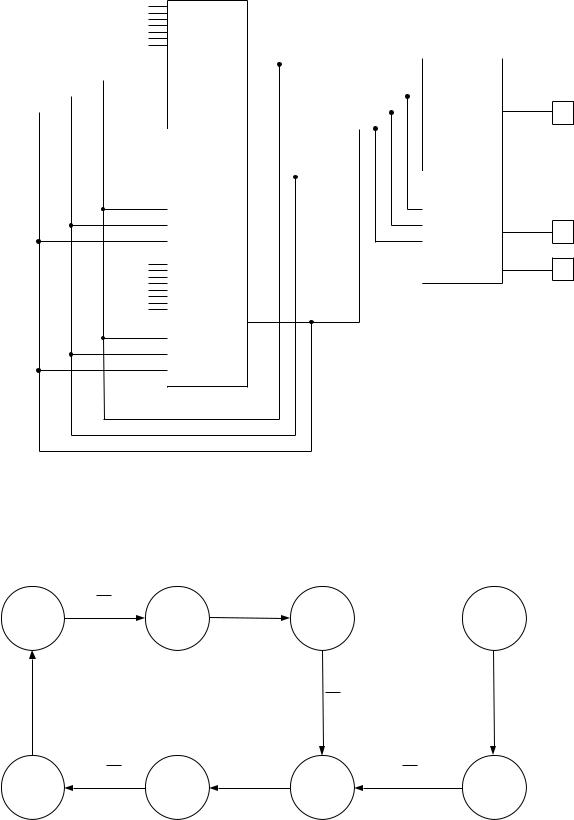

1.3 Структурна ЦА

Коди станів є водночас і адресами ПЗУ.

X (0,1)

|

|

|

|

|

MUX 1 |

|

QA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

A2 |

|

|

|

|

|

|

З |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

A1 |

|

|

|

|

DC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

A0 |

|

|

|

|

|

Ж |

||

|

|

|

|

|

|

|

|

|

|

|

головний |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X (0,1) |

|

|

|

|

QB |

|

|

|

|

|

Ч |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MUX 2 |

|

|

|

|

|

|

З |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A2

A1 DC Ж боковий

A0

Ч

X (0,1)

MUX 3 QC

A2

A1

A0

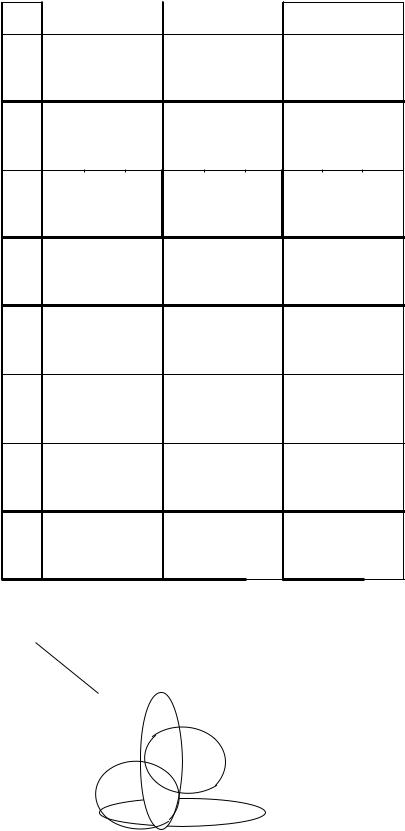

1.4 Орієнтований граф ЦА

За відміченою ГСА складаємо орієнтовний граф ЦА (автомата Мілі):

000 |

X |

Yг=11 |

|

Yб=00 |

|

X

100 |

X |

Yг=00 |

|

Yб=00 |

|

001

Yг=10

Yб=00

101

Yг=00

Yб=10

X |

011 |

|

010 |

Yг=00 |

|

||

|

|

||

|

Yб=00 |

|

|

|

X |

|

1 |

X |

111 |

X |

110 |

Yг=00 |

Yб=11

31

1.5 Абстрактний синтез на мультиплексах Складаємо таблицю істинності використовуючи орієнтовний граф ЦА:

|

|

t |

|

|

t+1 |

|

|

|

|

|

X |

QA |

QB |

Qc |

QA |

QB |

Qc |

|

DA |

DB |

DC |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

x |

x |

x |

|

x |

x |

x |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

Проведемо мінімізацію функцій, використовуючи карти Карно

DA |

x |

|

|

|

|

|

|

|

|

|

|

||

QB QA |

|

|

|

|

||

|

QC |

00 |

01 |

11 |

10 |

|

|

00 |

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

01 |

|

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

11 |

|

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

10 |

|

X |

1 |

1 |

1 |

|

|

|

|

|

|

|

32

DA=XQA+QBQC+QAQC+XQB

DB |

x |

|

|

|

|

|

|

|

|

|

|

||

QB QA |

|

|

|

|

||

|

QC |

00 |

01 |

11 |

10 |

|

|

00 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

01 |

|

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

11 |

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

10 |

|

X |

1 |

1 |

1 |

|

|

|

|

|

|

|

DB=XQB+QBQC+XQA

DC |

x |

|

|

|

|

|

|

|

|

|

|

||

QB QA |

|

|

|

|

||

|

QC |

00 |

01 |

11 |

10 |

|

|

00 |

|

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

01 |

|

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

11 |

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

10 |

|

X |

1 |

0 |

0 |

|

|

|

|

|

|

|

DC=QAQB+XQA+XQC+XQB

Зробили мінімізацію цих функцій збудження для Д-тригерів на картах Карно показують, що потрібна велика кількість логічних елементів для реалізації цих функцій. Подальший структурний синтез будемо робити на КЛС - мультиплексах.

Складемо таблицю істинності, на якій наглядно видно, зміну сигналів:

|

X |

QA |

QB |

QC |

QA |

QB |

QC |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

3 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

6 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

2 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

3 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

4 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

33

5 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

6 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

Складемо матричне рівняння ЦА, де кожен рядок матриці Х(t) вхідні сигнали відповідного мультиплекса. Зворотній зв’язок, що визначає S (t) – організовано відповідним поєднанням виходів мультиплексів з їх адресними входами

[St+1 ] = [St ][X t ]

éQA ùé |

0 |

0 |

1 |

|

|

|

|

1 |

1 |

1 |

ù |

||||

X |

X |

||||||||||||||

ê |

úê |

0 |

X 1 |

1 |

0 |

0 |

1 |

|

|

ú |

|||||

|

|

||||||||||||||

St+1 = êQB úê |

X ú |

||||||||||||||

êQ |

úêX 1 |

|

X |

1 |

0 |

X |

X |

1 |

ú |

||||||

ë C ûë |

|

|

|

|

|

|

|

|

|

|

|

|

|

û |

|

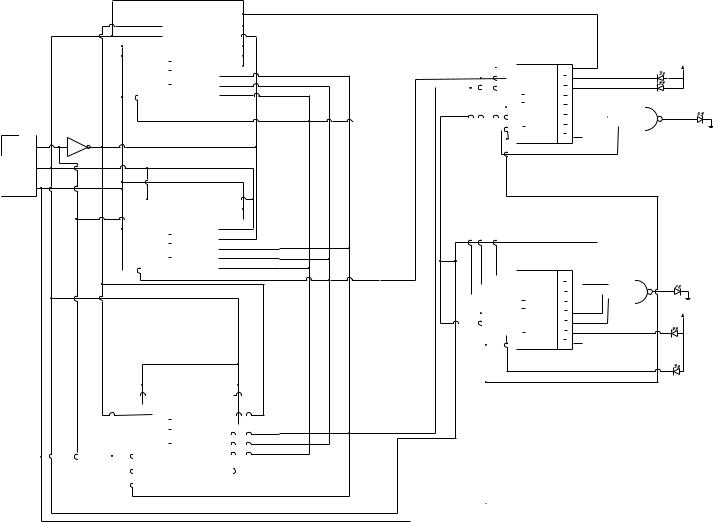

Визначаємо функції вихідних сигналів. Так як абстрактний синтез ми виконуємо на декодерах, а цифровий автомат Moore, то код St з виходів мультиплексів подається на адресні входи декодера. Відповідний унітарний код мультиплекса включає світло діод відповідного кольору для головної магістралі - декодер 1, та бокової – декодер 2.

QA |

|

DC |

7 |

|

|

|

|

|

|

|

|

|

|||

A2 |

головний |

|

|

|

|

|

|

|

|

Ч |

|||||

6 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||||

QB |

|

A1 |

|

5 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

4 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

QC |

|

|

A0 |

3 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

2 |

|

|

|

|

|

|

|

|

Ж |

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

З |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DC |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

З |

||

|

|

|

|

|

боковий |

|

|

|

|

|

|

|

|

||

|

|

|

|

A2 |

6 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

Ж |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

A1 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ч |

|

|

|

|

|

A0 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34

2 СТРУКТУРНИЙ СИНТЕЗ ЦА

Так як в процесі абстрактного синтезу ми використовуємо три мультиплекса для фіксації трьох розрядного коду стану S (t) цифрового автомату, то для реалізації вибираємо мультиплекс К155КП7 (8 х 1) .

Для реалізації вихідних сигналів вибираємо декодер К155ІД 7 (1 х 8), та логічний елемент К155ЛА1.

Для формування Х - інвертор К155ЛН1.

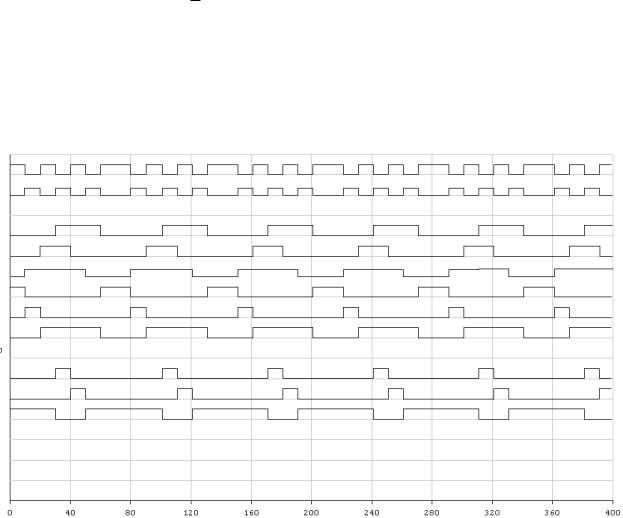

3 МОДЕЛЮВАННЯ ЦА

Оскільки, в даному пакеті немає вітчизняної елементної бази КЛС, то замість необхідних елементів візьмемо їх зарубіжні аналоги.

Рис.2 Часова діаграма ЦА

ВИСНОВОК

Спроектовано цифровий автомат світлофору. Перевірена його працездатність у пакеті Electronic Workbench. СЕП працює відповідно ТЗ, що

35

підтверджено часовими діаграмами. Габарити, монтажу будуть кращими якщо ми використаємо ПЛМ.

XS

CLK 1

Vcc 2

GND 3

DD6 |

DD1

1 |

I4 |

|

Vcc |

16 |

|

||

|

|

|

|||||

2 |

I3 |

|

I5 |

15 |

|

||

3 |

I2 |

К155КП7 |

I6 |

14 |

|

||

5 |

12 |

|

|||||

Y |

I8 |

|

|||||

4 |

I1 |

|

I7 |

13 |

|

||

|

|

|

|

|

|

||

|

|

6 |

Y |

|

S0 |

11 |

|

|

|

|

|||||

|

|

7 |

E |

|

S1 |

10 |

|

|

8 |

|

S2 |

9 |

|

||

|

GND |

|

|

|

|||

|

|

|

|

|

|||

DD2

|

|

|

1 |

I4 |

|

Vcc |

16 |

|

|

|

|

|

2 |

I3 |

|

I5 |

15 |

|

|

|

|

|

3 |

|

14 |

|

|||

|

|

|

I2 |

К155КП7 |

I6 |

|

|||

|

|

|

5 |

12 |

|

||||

|

|

|

Y |

I8 |

|

||||

|

|

|

4 |

I1 |

|

I7 |

13 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

6 |

Y |

|

S0 |

11 |

|

|

|

|

|

|

|

||||

|

|

|

|

7 |

E |

|

S1 |

10 |

|

|

|

|

8 |

GND |

|

S2 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD3

|

|

|

|

|

1 |

I4 |

|

Vcc |

16 |

|

|

|

|||

|

|

|

|

|

|

|

2 |

|

15 |

|

|

|

|||

|

|

|

|

|

|

|

I3 |

|

I5 |

|

|

|

|||

|

|

|

|

|

|

3 |

I2 |

|

I6 |

14 |

|

|

|

||

|

|

|

|

|

|

4 |

I1 |

К155КП7 |

I7 |

13 |

|

|

|

||

|

|

|

|

|

5 |

Y |

I8 |

12 |

|

|

|

||||

|

|

|

|

|

|

6 |

Y |

|

S0 |

11 |

|

|

|

||

|

|

|

|

|

7 |

E |

|

S1 |

10 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

||

|

|

|

|

|

8 |

|

S2 |

|

|

|

|||||

|

|

|

|

|

GND |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

DD4 |

|||

|

|

|

|

|

|

|

|

|

|

|

2 |

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

||

|

|

|

|

|

|

|

|

|

3 |

A2 |

К155ИД7 |

|||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

5 |

E2 |

|||||

|

|

|

|

|

|

|

|

|

|

4 |

E1 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

E3 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

7 |

|

||

|

|

|

|

|

|

|

|

|

7 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

||

|

|

|

|

|

|

|

|

|

GND |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD5

|

|

|

|

|

1 |

A0 |

|

|

|

|

|

|

|

2 |

|

||

|

|

|

|

|

A1 |

|

||

|

|

|

|

|

3 |

|

||

|

|

|

|

|

A2 |

|

||

|

|

|

|

|

4 |

К155ИД7 |

||

|

|

|

|

|

E1 |

|||

|

|

|

|

|

5 |

E2 |

|

|

|

|

|

|

|

|

6 |

E3 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

7 |

|

||

|

|

|

|

|

8 |

|

||

|

|

|

|

|

GND |

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vcc 16

0 15

1 14

2 |

13 |

|

|

|

DD4 |

|

12 |

|

|

|

|||

3 |

|

|

|

|||

4 |

11 |

|

|

|

|

|

|

|

|

|

|

||

10 |

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

||

69

Vcc |

16 |

|

|

|

|

DD8 |

|

15 |

|

||||||

0 |

|

|

|

|

|

|

|

14 |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

13 |

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

312

411

5 10

69

Примітка. Вивід DD4 та DD5 з’єднати з Vcc. Вивід DD6 та DD7 з’єднати з GND.

36

Література:

1.Электротехника и электроника в экспериментах и упражнениях. Практикум на Electronics Workbench том 2. Электроника М. 2000г.

2.Р. Токхейм Основы цифровой электроники. М. Мир 1993(1988).

3.В.П. Миловзоров. Элементы информационных систем. М. 1989г.

4.Джон Гленн Брукшир. Введение в компьютерные науки. К., 2001.

5.Самофалов К.Г., Романкевич А.Н., Валуйский В.Н., Каневский Ю.С., Пиневич М.М. Прикладная теория цифровых автоматов. - К.: Вища школа, 1987. – 375 с.

6.Сенько В.І. та ін. / Під ред. Сенько В.І. Електроніка і мікросхемотехніка. Підручник для вузів у 4-х томах. – К.: Обереги, 200. – 299 с.

7.Руденко В.С., Ромашко В.Я., Трифонюк В.В. Промислова електроніка. – К.: Либідь., 1993. – 432 с.

8.Малахов В.П. Электронные цепи непрерывного и импульсного действия. – К.; О.: Лыбидь, 1991. – 256 с.

9.Китаєв В.Є. Електроніка і мікросхемотехніка. – 1994

10.John Wakerly. Digital design. Principles and Practices, 2000, 1048 с.

11.Allen Dewey/ Analysis and digital systems with VHDL. – PWS Publishing Company, 1997. - 987 c.

12.Джонс С. Электроника. Практический курс. – М.: Постмаркет, 1999.

– 419 c.

13.Прянишников В.А., Электроника. Полный курс лекций. – СПб.: Корона-принт, 2003. – 416 с.

14.Портал О.Н. Цифровая электроника. – СПб.: БХВ-Петербург, 2001.

– 442 с.

15.Угрюмов Е. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2001.

– 518 с.

16.Шило В.Л. Популярные цифровые микросхемы. – М.: радио и связь, 1988. – 349 с.

17.Г. Хоуп. Проектирование цифровых вычислительных устройств на интегральных схемах. – М.: Мир, 1984. – 400 с.

37