Методичка КР ПТЦА

.pdfМІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ ОДЕСЬКИЙ НАЦІОНАЛЬНИЙ ПОЛІТЕХНІЧНИЙ УНІВЕРСИТЕТ

ІНСТИТУТ КОМП’ЮТЕРНИХ СИСТЕМ

Методичні вказівки до курсової роботи з дисципліни

«Прикладна теорія цифрових автоматів»

Укладач: |

Богатова О. О. |

студентка групи АЭ-041 Дікусар К. В.

Одеса

2007

Метою курсової роботи є розвиток у студентів самостійності в вирішенні фахових задач та придбання практичних навичок проектування цифрових автоматів (ЦА).

Докладний зміст курсової роботи характеризується наступним типовим завданням (ТЗ).

Типове завдання

1.Постанова задачі:

1.1.Опис праці ЦА або змістовна (ГСА) граф схема алгоритму ЦА.

1.2.Опис вхідних сигналів.

1.3.Опис вихідних сигналів.

1.4.Елементна база.

2.Графічна частина: креслення СЕП формат А1 або А2 або А3.

Курсова робота включає в себе наступні етапи внутрішнього проектування:

∙Вступ;

∙Складання змістовної ГСА (якщо її нема в ТЗ);

∙Складання відзначеної ГСА (кодування ГСА ЦА);

∙Складання орієнтованого графу ЦА;

∙Абстрактний синтез ЦА;

∙Структурний синтез ЦА;

∙Складання переліку елементів та СЕП;

∙Виконання графічної частини;

∙Моделювання ЦА;

∙Скласти схему дослідження моделі ЦА;

∙Дослідити модель ЦА й одержати часові діаграми праці ЦА;

∙Висновки.

Приведемо приклади проектування нескладних цифрових автоматів із області обчислювальної техніки та з систем цифрової автоматики.

Технічне завдання №1

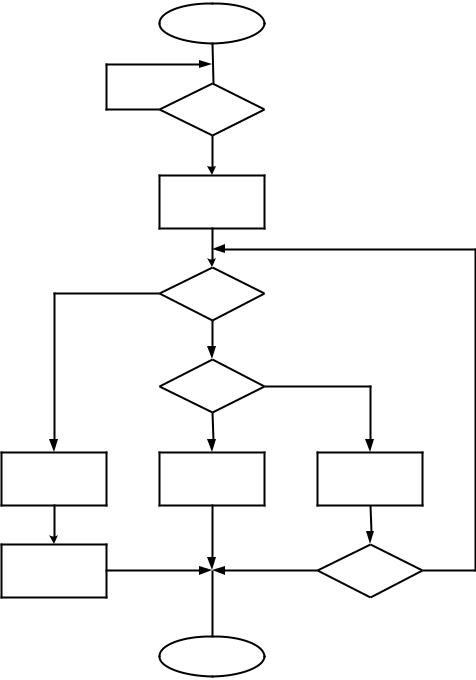

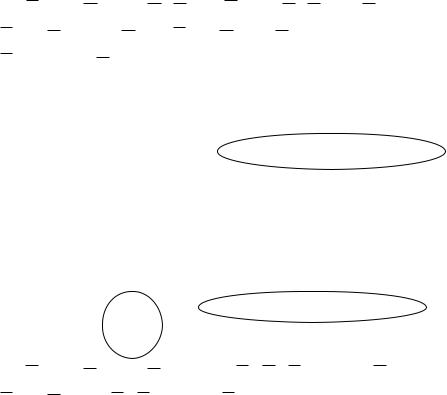

Постанова задачі: спроектувати керуючий ЦА для операційного пристрою (ОП) з використанням ПЗУ мікрокоманд. ЦА при конкретних логічних умовах входу Х, відповідно мікропрограмі, виробляє послідовність керуючих команд Y для ОП. ГСА приведена на мал. 1.1.

Вхідні сигнали: множина Х = {х0, х1, х2, х3}.

Вихідні сигнали: множина Y = {Y0, Y1, Y2, Y3, Y4, Y5}, записаних у ПЗУ, Yi – 8 - ми розрядний двійковий код.

Елементна база: ЦІМС СЩІ.

2

1. АБСТРАКТНИЙ СИНТЕЗ |

||

|

Змістовна ГСА |

|

|

ПОЧАТОК |

|

S0 |

|

|

0 |

X0 |

|

|

|

|

|

1 |

|

S1 |

АДРЕСА 1 |

|

|

1 |

|

|

X1 |

|

|

0 |

|

|

1 |

|

|

X2 |

|

S2 |

0 |

S5 |

S4 |

||

АДРЕСА 2 |

АДРЕСА 4 |

АДРЕСА 5 |

S3 |

|

|

АДРЕСА 3 |

0 |

1 |

|

X3 |

|

|

КІНЕЦЬ |

|

|

Рис. 1.1 |

|

3

Кодування: логічні умови для визначення адреси, за якою написано керуючі команди, кодуються одно розрядними двійковими кодами (хі) і створюють паралельний 4-х – розрядний код.

Внутрішні стани ЦА S = {S0, S1, S2, S3, S4, S5} за ГСА.

Кодуємо стани трьох розрядним двійковим кодом відповідно:

S0 – 000;

S1 – 001;

S2 – 010;

S3 – 011;

S4 – 100;

S5 – 101.

Коди станів є водночас і адресами ПЗУ.

ПЗУ – це матриця 6х8, де записані 6 восьми розрядних керуючих наборів сигналів керування операційним автоматом.

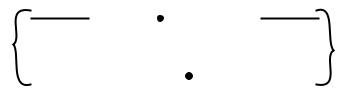

Структура ЦА подана на рис. 1.2. Відмічена ГСА подана на рис. 1.3.

|

. |

1 |

|

|

|

2 |

. |

|

|

|

|

|

|

|

A |

|

|||

X |

. |

S |

|

|

|

. |

Y |

||

|

. |

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1.2

1 – схема формування адреси;

2 – формувач вихідних сигналів.

4

|

Відмічена ГСА |

|

|

000 |

|

Y0 |

|

|

0 |

X0 |

|

|

|

|

|

1 |

|

S1 |

001 |

|

|

1 |

|

|

X1 |

|

|

0 |

|

|

1 |

|

|

X2 |

|

Y2 |

0 |

Y5 |

Y4 |

||

010 |

100 |

101 |

Y3 |

|

|

011 |

0 |

1 |

|

X3 |

|

|

000 |

|

|

Рис. 1.3 |

|

5

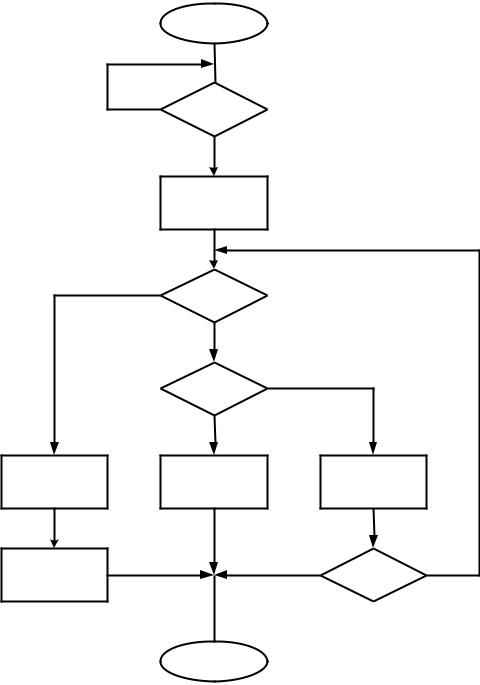

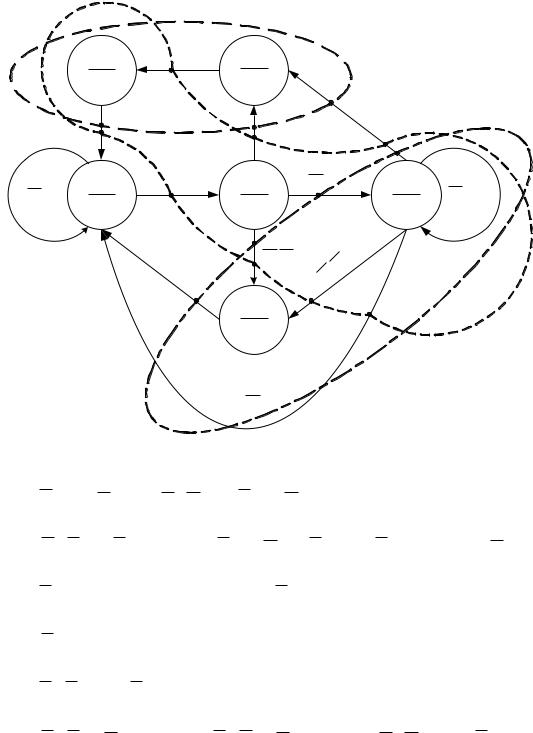

Складаємо за відзначеною ГСА орієнтований граф ЦА (автомату Мура).

011 |

1 |

010 |

Y3 |

|

Y2 |

|

|

|

|

X |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

X |

|

|

|

|

1 |

|

3 |

|

|

|

|

X1 |

|

|

|

|

|

|

|

|

|

|

|

X0 |

000 |

X0 |

001 |

X1X2 |

101 |

X1X2X3 |

Y0 |

|

Y1 |

|

Y5 |

||

|

|

|

|

1X1X2

100 Y4

3 2X 1X X

X3

Складаємо таблицю переходів та виходів.

Таблиця №1.

Входи |

Х0 |

Х1 |

|

|

1X2 |

|

|

|

|

|

|

|

|

|

2Х3 |

Х1Х3 |

|

|

|

|

|

1Х2Х3 |

1 |

|

Вихідний |

|

Х |

|

X |

1 |

X |

2 |

|

X |

1 |

X |

|

X |

3 |

|

X |

||||||||

стан |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y0 |

S0 |

S1 |

- |

- |

- |

|

- |

|

- |

- |

|

- |

- |

|||||||||||

Y1 |

S1 |

- |

S2 |

|

S5 |

|

|

S4 |

- |

|

- |

- |

|

- |

- |

|||||||||

Y2 |

S2 |

- |

- |

- |

- |

|

- |

|

- |

- |

|

- |

S3 |

|||||||||||

Y3 |

S3 |

- |

- |

- |

- |

|

- |

|

- |

- |

|

- |

S0 |

|||||||||||

Y4 |

S4 |

- |

- |

- |

- |

|

- |

|

- |

- |

|

- |

S0 |

|||||||||||

Y5 |

S5 |

- |

- |

- |

- |

|

|

|

S4 |

S2 |

|

S0 |

|

|

S5 |

- |

||||||||

Абстрактний синтез ЦА на Д-тригерах.

|

|

|

|

Таблиця № 2 Часові функції збудження для Д-тригерів |

|

|

||||||||

X |

|

t |

|

|

t+1 |

|

|

t |

|

|||||

QA |

QB |

QC |

QA |

QB |

QC |

DA |

DB |

DC |

||||||

|

|

|

|

|

||||||||||

|

|

0 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

Х |

|||||||||||||

Х0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|||||

Х1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|||||

|

|

1 |

|

2 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

|

Х |

Х |

||||||||||||

|

Х 1Х2 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

||||

1 |

|

|

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

||

6

1 |

|

|

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

|

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

3 |

|

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Х |

||||||||||||

Х1Х3 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

||||

|

|

1 |

|

2Х3 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

Х |

Х |

|||||||||||

|

Х 1Х2Х3 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

|||

Проведемо мінімізацію функцій збудження Д-тригерів,

використовуючи карти Карно. |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DA |

QAQB |

00 |

|

|

|

01 |

11 |

10 |

|

|

|||||||

|

QC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

|

|

0 |

* |

0 |

|

|

||||||||

1 |

|

|

1Х2+ |

|

1 |

|

2 |

0 |

* |

|

|

1 |

|

2Х3+ |

|

1Х2Х3 |

|

|

Х |

Х |

Х |

Х |

Х |

Х |

|||||||||||

DA = Q BQC ( Х 1Х2 + Х 1 Х 2) + Q BQC ( Х 1 Х 2Х3+ Х 1Х2Х3) =

=Q BQC Х 1 (Х2 + Х 2) + Q BQC Х 1Х3 ( Х 2+Х2) =

=Q BQC (Х1 + Х 1Х3)

DB |

QAQB |

00 |

|

|

|

01 |

11 |

10 |

||||||

|

QC |

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

|

|

0 |

|

|

|

1 |

* |

0 |

||||

|

1 |

|

|

|

Х1 |

|

|

|

0 |

* |

|

Х1Х3 |

||

|

DB = |

|

BQC (Х1 + Х1Х3) + QB |

|

C |

|

|

|

|

|

||||

|

Q |

Q |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

DC |

QAQB |

00 |

|

|

|

01 |

11 |

10 |

||||||

|

QC |

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

|

|

|

Х0 |

|

1 |

* |

0 |

|||||

|

1 |

|

|

|

|

1Х2 |

|

0 |

* |

|

|

1Х2Х3 |

||

|

|

|

|

Х |

|

|

|

Х |

||||||

DC = Q BQC ( Х 1Х2 + Х 1Х2Х3) + Q A Q B Q CХ0 + QB Q C = = Q BQC Х 1Х2 + Q A Q BХ0 + QB Q C

Абстрактний синтез на RS – тригерах.

7

1 X 3

X0 |

0 |

X0 |

001 |

X1X2 |

Y0 |

|

1 |

|

|

|

|

|

1 |

X1X2 |

|

1 Y4

X3

3 2X

Рис. 1.4

SA = Q BQC ( Х 1Х2 + Х 1 Х 2) = Q BQC Х 1

RA = Q B Q C + Q BQCХ1Х3 + Q BQC Х 3 = Q BQC + Q BQC (Х1Х3 + Х 3)

SB = Q AQCХ1 + QAQCХ1Х3 = QCХ1 (Q A + QAХ3)

RB = Q AQC

SC = Q A Q BХ0 + Q AQB

RC = Q A Q B ( Х 1Х2 + Х1) + Q A Q B ( Х 3 + Х1Х3 + Х 1 Х 2Х3) + Q AQB

Абстрактний синтез на тригерах свідчить про складні логічні функції збудження, а тому складні КЛС.

Проаналізуємо варіант синтезу ЦА на мультиплексорах. Абстрактний синтез на мультиплексорах – це аналіз таблиці переходів.

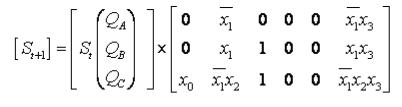

На основі аналізу складаємо матричне рівняння ЦА.

8

Кожна строка матриці входів визначає відповідні стани S(t) вхідних сигналів.

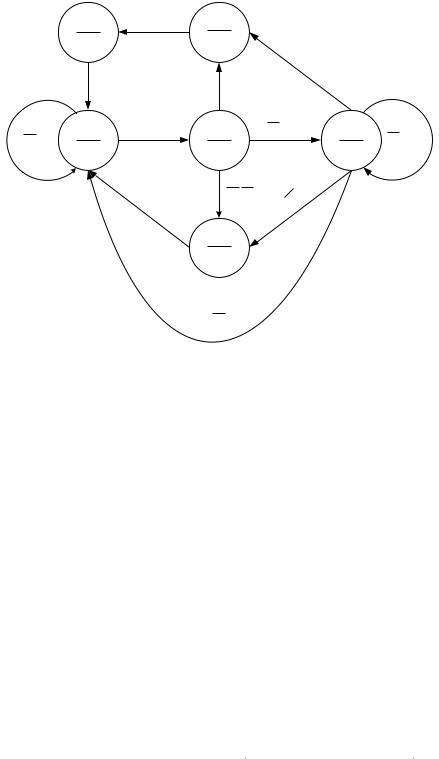

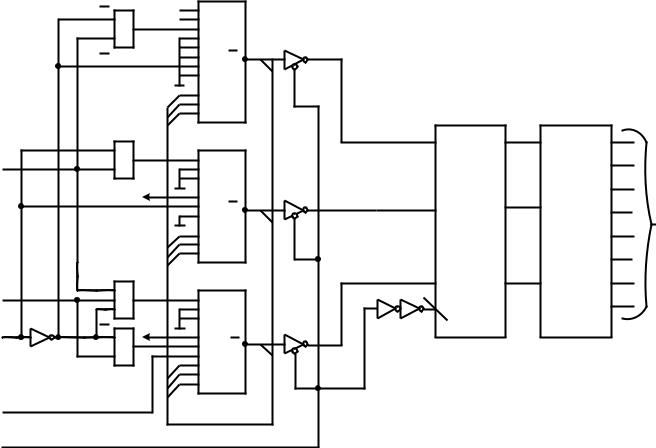

2. СТРУКТУРНИЙ СИНТЕЗ

Проведемо структурний синтез на мультиплексорах з буфером інвертуючим з третім станом, використовуючи входи дозволу по виходу як тактові за умовою достатньо невеликої частоти: Т < 1/2fT

Синтезуємо СЕС на мультиплексорах та ПЗУ. Так як на входи мультиплексорів подаються кон’юнкціі або інверсії відповідних сигналів, використовуємо ЛE інвертори та відповідні кон’юнктори 2І та 3І.

Так як стани закодовано 3х розрядним кодом (St), а всього станів 6 – використовуємо 3 мультиплексори (8 х 1 – К155КП7 – 74151). Для запобігання появи хибних адрес на входах ПЗУ, а як слідство хибних вихідних сигналів треба синхронізувати виходи MUX з адресними входами ПЗУ. Адреса фіксується у регістрі (К155ТМ8) у час паузи імпульсів clk. Необхідно, щоб

ti clk ≥ tзсп MUX + tзсп ЛЕ,

tп clk ≥ tспр Тр + tспр ROM,

а буфером, що з’єднують виходи MUX з входами RG, запобігають появі хибних адрес.

СЕС наведена на рис. 1.5.

9

|

X1 |

|

7 |

MUX |

|

|

|

|

|

|

|

|

& |

6 |

|

|

|

|

|

|

|

|

X3 |

5 |

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

X1 |

|

3 |

Y |

QA |

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|||

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

2 |

1 |

|

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

|

X1 |

|

|

|

|

A2 |

RG |

A2 |

A2ROM b7 |

|

X3 |

X3 |

& |

5 |

MUX |

|

|

|

|

|

b6 |

|

4 |

|

|

|

|

|

|

|||

|

|

Vcc |

3 |

|

|

|

|

|

|

b5 |

|

X1 |

2 |

|

QB |

|

|

|

|

||

|

|

Y |

A1 |

|

A1 |

A1 |

b4 |

|||

|

|

|

1 |

|

|

|||||

|

|

|

0 |

|

|

|

|

|

|

Yi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

|

|

|

b3 |

|

|

|

|

2 |

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

|

|

|

|

|

b2 |

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

A0 |

|

A0 |

A0 |

b1 |

X2 |

X |

|

|

|

|

|

|

|

|

|

|

& |

5 |

MUX |

|

C |

|

|

|

b0 |

|

|

|

|

|

|

|

|||||

|

|

|

4 |

|

|

|

|

|

||

X1 |

X1 |

Vcc |

3 |

|

|

|

|

|

|

|

2 |

|

QC |

|

|

|

|

|

|||

|

Y |

|

|

|

|

|

||||

|

X2 |

& |

1 |

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

X0 |

22 |

|

|

|

|

|

|

|

|

|

2 |

1 |

|

|

|

|

|

|

|

|

|

|

20 |

|

|

|

|

|

|

|

X0 |

|

|

|

|

|

|

|

|

|

|

clk (fT) |

|

|

|

|

|

Рис. 1.5. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10