Лекция 9

Методы обеспечения контролепригодности.

Методы контролепригодности дискретных приборов.

Наиболее важная характеристика качества диагностического обслуживания —способность локализации неисправности в приемлемом объеме аппаратуры диагностируемого устройства, чаще всего в съемном блоке, Решение этой задачи в большинстве существующих функциональных устройствах встречает ряд принципиальных затруднений. Остановимся на основных из них и определим наметившиеся в настоящее время подходы их преодоления.

Наиболее общей и определяющей все другие особенности процессора как цифрового устройства являются исключительная его сложность, наличие значительного количества элементов памяти, сложная взаимосвязь различных частей процессора, операционный принцип работы, т. е. минимальное законченное действие есть операция. С другой стороны, диагностика процессора во многому аналогична задаче самодиагностики и вследствие этого при диагностике процессора возникает проблема аппаратурного ядра.

В общем случае аппаратурное ядро представляет собой ту часть аппаратуры процессора, наличие неисправности в которой лишает процессор возможности выполнять диагностические программы, т. е. это та часть аппаратуры, которая должна быть проверена до выполнения обычных диагностических процедур. Уже само четкое определение аппаратурного ядра встречает затруднение, В зависимости от особенностей и конструкции процессора объем аппаратурного ядра может изменяться в широких пределах, достигая 50 - 60%. Кроме того, вследствие значительного объема диагностических программ хранение их осуществляется на различного типа внешних носителях. Это обстоятельство добавляет к аппаратурному ядру схемы и устройства, которые осуществляют загрузку в процессор (оперативную память) диагностических программ. Таким образом, необходимо учитывать также и ядро системы.

Проверка аппаратурного ядра, если не предприняты специальные меры (вынесенное ядро-тестер, различные удобные пультовые режимы проверок), представляет собой трудоемкие и не всегда однозначные ручные процедуры. Диагностика ЭВМ в настоящее время предполагает сочетание процедур автоматических, выполняемых самой ЭВМ, и ручных с использованием контрольно-измерительной аппаратуры. При требовании эффективности диагностики очевидно стремление к сокращению ручных процедур за счет автоматизации процесса обнаружения и локализации неисправностей., поэтому важнейшим требованием для эффективности организации диагностики является сокращение аппаратурного ядра системы.

Решают проблемы ядра системы в двух направлениях:

1) создание простых и специальных средств, легко контролируемых, для ввода диагностических программ;

2) максимальное сокращение аппаратурного ядра процессора. Наиболее эффективное сокращение аппаратурного ядра в настоящее время достигается за счет применения микродиагностики. Так, реализация этого принципа в модели 30 системы/360 дала возможность сократить объем ядра до 1%.

Следующая проблема, общая для диагностики всех программно-управляемых цифровых устройств, была определена в как проблема разрешающей способности по адресам и времени, Проблема разрешающей способности по адресам заключается в ограниченном программном доступе к элементам схем устройства. Решение этой проблемы—в обеспечении возможности устанавливать процессор в необходимое состояние и считывать это состояние в специально выделенную область памяти. Эта способность в настоящее время реализуется выполнением двух функций: «опрос» и «установка» . Выполнение «опроса» вызывает запись состояния большинства триггерных элементов процессора в специальную зону оперативной памяти. «Установка» реализует обратную функцию: данные, расположенные в специальной зоне оперативной памяти, используют для принудительной установки процессора в фиксированное состояние.

Указанная способность—мощное и полезное средство, существенно расширяющее возможности диагностики и одновременно упрощающее не только сам процесс диагностики, но и процесс построения диагностических тестов. Процессор получает возможность при обнаружении схемами контроля или контролирующими тестами сохранить истинное свое состояние для последующего его анализа программными средствами или обслуживающим персоналом. Это позволяет организовать диагностический поиск трудно поддающихся диагностике перемежающихся неисправностей.

Далее, создается возможность перед реализацией тестовых процедур устанавливать процессор в предопределенное состояние иначе говоря, осуществлять установочную процедуру. При этом не только значительно упрощается посылка желаемых стимулов в процессор, но и создается принципиальная возможность посылать стимулы в определенные части (схемы процессора). Это обстоятельство дает возможность разбивать аппаратуру процессора на сравнительно простые участки и отдельно или последовательно производить их диагностику:

Проблема разрешающей способности по времени заключается в ограничении программного доступа к реакциям устройства на тестовые стимулы интервалом времени, соответствующим циклу процессора. Такая ситуация затрудняет выявление истинной реакции схем, отделяет анализ реакций от действительного момента проявления неисправности. При пультовых режимах анализа работы системы возникают затруднения в выделении минимальной по длине цепочки изменения состояния системы. Эту проблему в настоящее время решают сокращением программно доступных интервалов времени путем придания процессору возможности работать под управлением специальных команд на небольших интервалах времени, которые могут составлять отдельные части машинной, операции или даже такты работы процессора. Проблема решается, за счет ввода специальной аппаратуры, пультовых переключателей, чувствительных к результату выполнения не только одной машинной операции, но и тактов работы машины. В процедурах диагностики увеличение разрешающей способности по времени достигают за счет реализации специальных диагностических команд и микро диагностики. В итоге создается возможность наблюдать, анализировать небольшие элементарные процессы, прежде чем они будут замаскированы или запутаны другими действиями процессора, и сокращать время диагностики, особенно при наличии перемежающихся неисправностей.

Реализация новых возможностей рассмотренных выше и достигаемых за счёт дополнительной диагностической аппаратуры существенно сокращает процедуру диагностики, способствует ещё большей ее автоматизации и упрощает непосредственно процесс построения последовательности диагностических процедур. Это достигается прежде всего за счет расчленения всего объема аппаратура процессора на диагностируемые участки. Кроме того, эффективная реализация этих возможностей выдвигает дополнительные требования и к конструктивной реализации аппаратуры процессора, в частности в достижении максимальной модульности т. е. выделение в процессе проектирования и конструирование отдельных независимых (с минимальным количеством взаимных связей и функциональной автономностью) частей схемы процессора и последующего размещения их в сменные блоки. При этом возникает новая задача эффектного разбиения аппаратуры процессора с размещением схем с различными неисправностями в общем сменные блоки.

СТРУКТУРНЫЕ МЕТОДЫ ПОВЫШЕНИЯ НАДЕЖНОСТИ ЭВМ

Значительного повышения надежности ЭВМ достигают созданием новых элементов. Так, применение ИС для построения основных узлов ЭВМ (регистров, сумматоров и др.) привело r значительному повышению надежности машин третьего и четвертого поколений.

Однако повышением надежности элементов рассмотренными выше методами не удается в настоящее время полностью решить проблему построения надежных ЭВМ, что вызвано значительным опережением роста сложности вновь разрабатываемых ЭВМ, большими затратами при получении элементов высокой надежности, а также существованием элементов, надежность которых довольно низка и трудно поддается повышению (устройства ввода и вывода информации и др.). Поэтому один из путей повышения надежности ЭВМ — введение схемной избыточности. Разработка методов синтеза ЭВМ, обладающих заданной надежностью, сводится к нахождению оптимальной избыточности. При этом основное — согласование метода повышения достоверности с наиболее вероятными ошибками, появляющимися в различных устройствах ЭВМ. Полные и достоверные сведения об ошибках могут быть получены при эксплуатации машин, но проведение подобных испытаний связано с большими затратами времени и не всегда возможно при эксплуатации. Кроме того, такие сведения зависят от конкретного конструктивного выполнения ЭВМ и конкретных условий ее эксплуатации, в связи с этим они частично теряют свою ценность при проектировании новых вычислительных устройств. Поэтому на практике сведения об ошибках получают приближенно по результатам специальных статистических испытаний, проводимых на установках, которые содержат испытуемое устройство (контрольное устройство работает так же, как и испытуемое, однако в нем приняты специальные меры по повышению надежности) и устройство автоматической обработки результатов.

При обработке статистических данных определяют вероятностные характеристики ошибок как функции времени работы устройств. К этим характеристикам относят вид распределения, среднее время между отказами или сбоями, кратность ошибок, наличие пачек и др. Эти характеристики являются исходными данными для выбора метода введения избыточности и расчета надежности проектируемой ЭВМ.

Так как увеличение надежности отдельных элементов есть предел, обусловливающий современный уровень развития технологии их изготовления, а сложность устройств стремительно возрастает, то введение схемной избыточности имеет все большее значение при построении надежных ЭВМ.

Один из видов схемной избыточности — структурное резервирование, предполагающее включение в схему устройства дополнительных элементов, которые позволяют скомпенсировать отказы отдельных частей устройств и обеспечить его надежную работу. Но резервирование эффективно только в том случае, когда неисправности являются статистически независимыми.

![]()

![]()

![]()

![]()

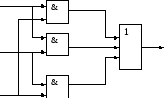

Рис. 7.4 Схема мажоритарного элемента «2 из 3»

В ЭВМ ввод структурной избыточности производят по следующей схеме: входные сигналы поступают на n логических схем, причем п> к, где k— число логических схем в нерезервированной схеме Выходные сигналы всех п логических схем далее подают на решающий элемент, который согласно функции решения по этим си- чалам определяет значения выходных сигналов всей схемы.

Функция решения

— правило отображения входных состояний

решающего элемента на множество его

выходных состояний. Простейший и наиболее

распространенный вид функции решения—«закон

большинства», или мажоритарный закон.

В таком случае решающий элемент обычно

называют мажоритарным элементом. Работа

мажоритарного элемента состоит в

следующем: на входы элемента поступают

двоичные сигналы oт нечетного

количества идентичных элементов;

выходной сигнал элемента принимает

значение, равное значению, которое

принимает большинство входных сигналов.

Наиболее широко используют мажоритарные

элементы, работающие по закону «2 из 3».

В этих элементах значение выходного

сигнала равно значению двух одинаковых

входных сигналов. Кроме того, известны

мажоритарные элементы, работающие по

закону «3 из 5», «4 из 7» и т. д. Схема

мажоритарного элемента, работающего

по закону «2 из 3» и построенного из

логических элементов И и ИЛИ, основана

на выражении

![]() и имеет вид. изображенный на рис. 7.4.

и имеет вид. изображенный на рис. 7.4.

Вероятность безотказной работы мажоритарной схемы «2 и 3» приведенной на рис. 7.4, можно рассчитать по формуле

![]()

где Pu(t) — вероятность безотказной работы схемы И.

Вероятность безотказной работы мажоритарной схемы при k=(n—l)/2 определяется соотношением

где n - число входов

мажоритарного элемента: р — вероятность

безотказной работы одного элемента

схемы;

![]() вероятно безотказной работы мажоритарного

элемента.

вероятно безотказной работы мажоритарного

элемента.

Для повышения надежности схемы могут быть введены избыточные мажоритарные элементы. В этом случае при выходе одного или нескольких мажоритарных элементов из строя схема продолжает работать безотказно за счет большинства исправно работающих мажоритарных элементов. Вероятность безотказной работы такой схемы определяется как

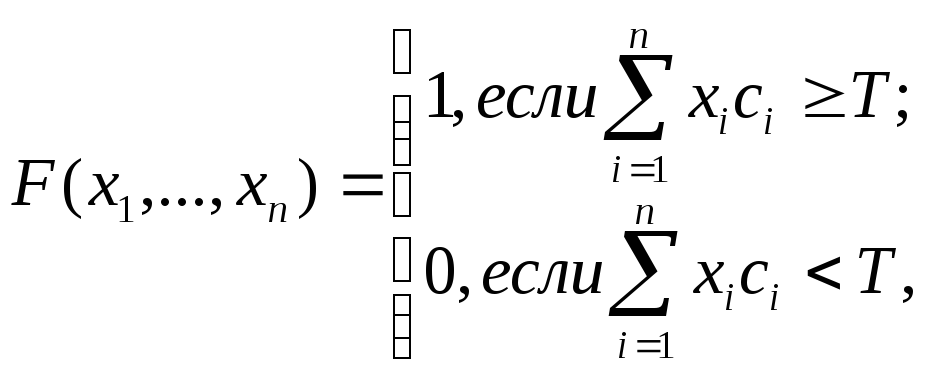

Однако если

логические схемы не идентичны, «закон

большинства» неприменим. В таких

случаях используют взвешенные входы

решающего элемента. Работу такого

решающего элемента описывают пороговой

функцией. Функцию алгебры логики

р(х),...,х„) называют пороговой, если

существует ряд таких действительных

чисел с,, с2 с„ и

![]() для которых выполняется условие

для которых выполняется условие

где

![]() - независимые переменные, принимающие

значения 0 или 1;

- независимые переменные, принимающие

значения 0 или 1;

![]() - вес (положительный или отрицательный),

соответствующий

- вес (положительный или отрицательный),

соответствующий

![]() ; Т - порог функции.

; Т - порог функции.

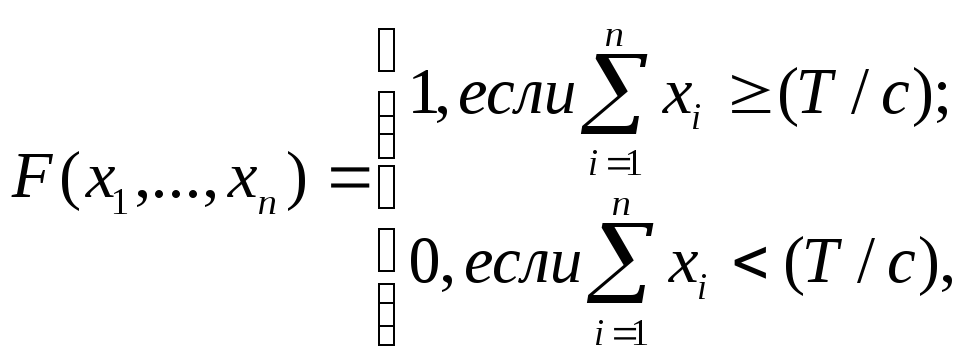

Наиболее часто в ЭВМ используют пороговые функции у которых с,= с2=... = с„ = с>0 и Т^-0. Следовательно,

Если

![]() 1, если k или большее число переменных

равно 1;

1, если k или большее число переменных

равно 1;

То

![]() 0. если k —1 или меньшее число

переменных равно 1,

0. если k —1 или меньшее число

переменных равно 1,

Решающий элемент, работающий согласно этим выражениям, называют пороговым элементом. Схема порогового элемента показана на рис. 7.5.

Веса входов порогового элемента выбирают в зависимости от вероятности ошибок в соответствующей логической схеме. Логической схеме с большей вероятностью ошибки соответствует меньший вес, а более надежной схеме - больший вес.

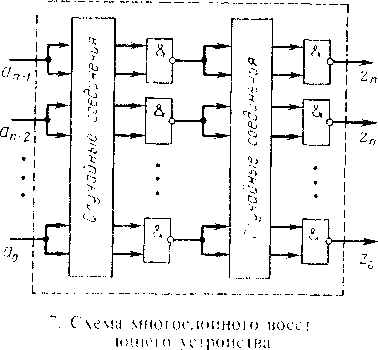

Схемы, преобразующие r избыточных входных сигналов, часть из которых может быть ошибочными, в r безошибочных сигналов, называют восстанавливающими устройствами. Простейший вид восстанавливающего устройства представлен на рис. 7.6. В таких схемах в качестве решающего элементa используют мажоритарный элемент, пороговый элемент и др. Кроме того, имеются устройства, в которых соединение входов произведено случайным образом. Такие восстанавливающие устройства называют однослойными.

+1

Вход Z Выход

Рис. 7.5 Схема порогового элемента

Рис. 7.6. Схема восстанавливающего устройства со ciporo oi:r. деленными соединениями

Восстанавливающие устройства могут быть построены также из двух слоев логических элементов с использованием двухвходовых элементов И —НЕ и случайных соединений входов. Схема такого устройства представлена на рис. 7.7. Здесь одиночная ошибка на входе вида 0 - 1 исправляется первым слоем. Одиночная ошибка вида 1 -0 вызывает двойную ошибку на выходе первого слоя, которая исправляется вторым слоем. Двойная ошибка на выходе первого слоя будет исправлен, всегда, когда на каждую пару входов И —НЕ второго слоя поступит хотя бы один безошибочный сигнал. Если на оба входа некоторого элементам И - НЕ поступят ошибочные сигналь то на выходе восстанавливающего устройства соответствующие сигнал будет ошибочным. При большом r, когда в основном применяют случайные соединения входов, вероятность такого совпадения очень мал; При небольшом r эта вероятность увеличиваете и поэтому вместо случайных соединений применяют соединения, соответствующие определен ному закону. Законы определяющие порядок соединения входов, исследуют избыточной логикой с переплетением.