Теория управления / Л4-Миль-Мур-СА / pics / 6-sequential logic-31

.pdf

D flip-flop with reset (or set)

|

|

|

|

|

R |

D |

Q |

|

|

|

|

|

|

0 |

1 |

||

|

|

|

|

||

|

|

|

|

|

|

clk |

Q‘ |

D 0 |

0 |

0 |

|

|

|

|

|

||

|

|

1 |

0 |

1 |

|

|

|

||||

|

|

|

|

|

|

Q

R(eset)

Note: this option is useful when we use D flip-flops in counters

A.J. Han Vinck |

51 |

|

|

|

|

|

|

|

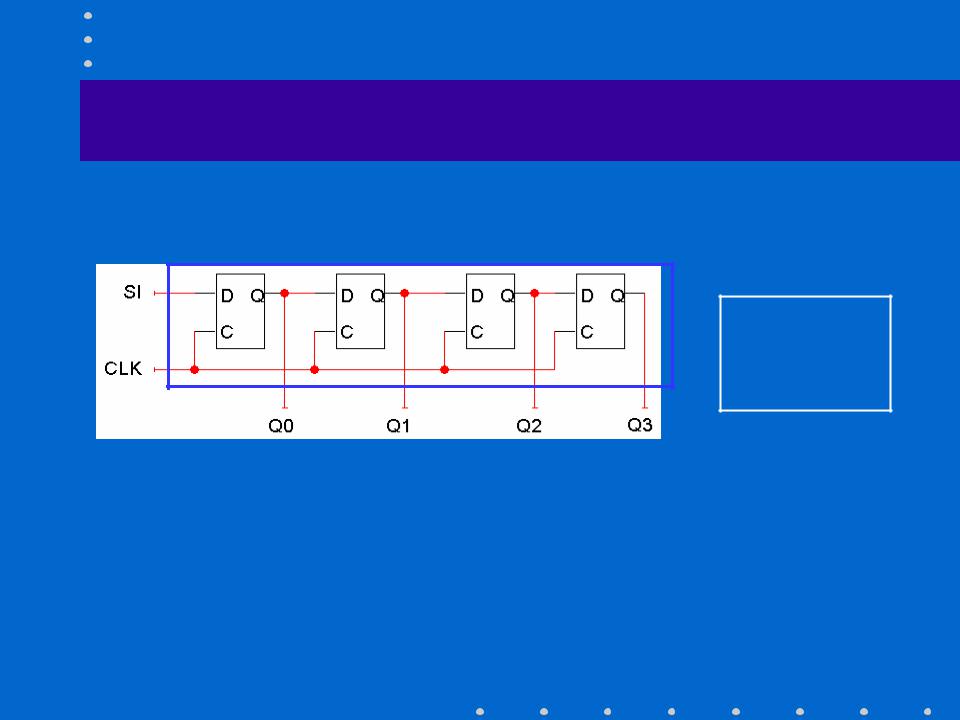

A shift register

•A shift register “shifts” its output once every clock cycle.

Q0(t+1) = SI

Q1(t+1) = Q0(t)

Q2(t+1) = Q1(t)

Q3(t+1) = Q2(t)

A.J. Han Vinck |

52 |

|

|

|

|

|

|

|

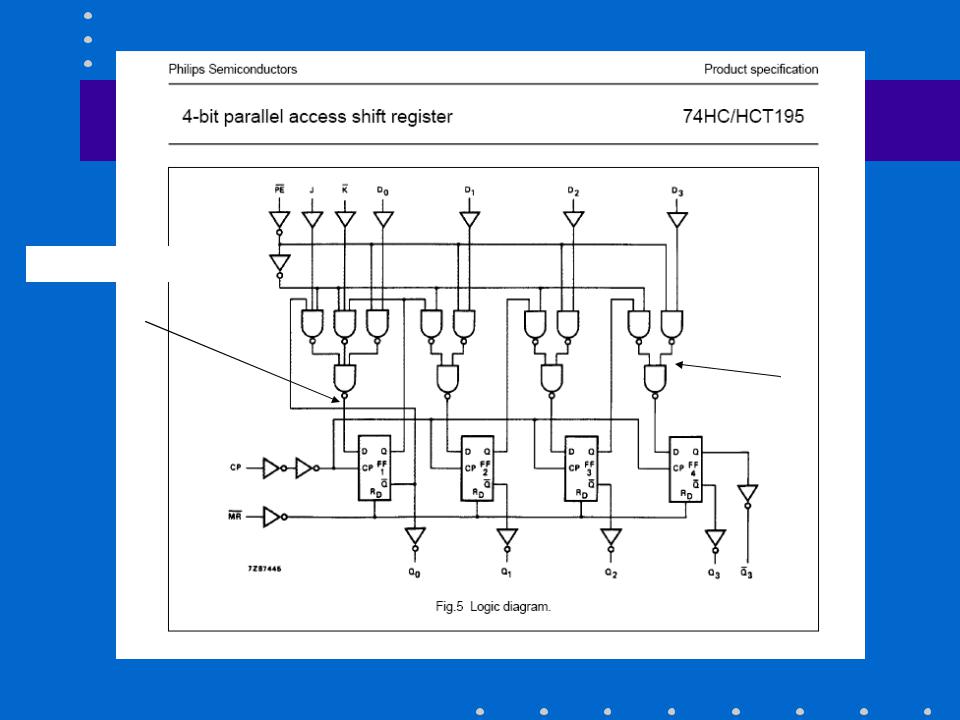

Shift registers with parallel load

•We can add a parallel load, just like we did for regular registers.

–When LD = 0, the flip-flop inputs will be SIQ0Q1Q2, so the register shifts on the next positive clock edge.

–When LD = 1, the flip-flop inputs are D0-D3, and a new value is loaded into the shift register, on the next positive clock edge.

53

Keep the content: A better parallel load

-When LD = 0, the flip-flop inputs are Q3-Q0, so each flipflop just keeps its current value.

-When LD = 1, the flip-flop inputs are D3-D0, and this new value is “loaded” into the register.

54

S

S(JQ‘+K‘Q)+S‘D0)

multiplex

A.J. Han Vinck |

55 |

|

|

|

|

|

|

|

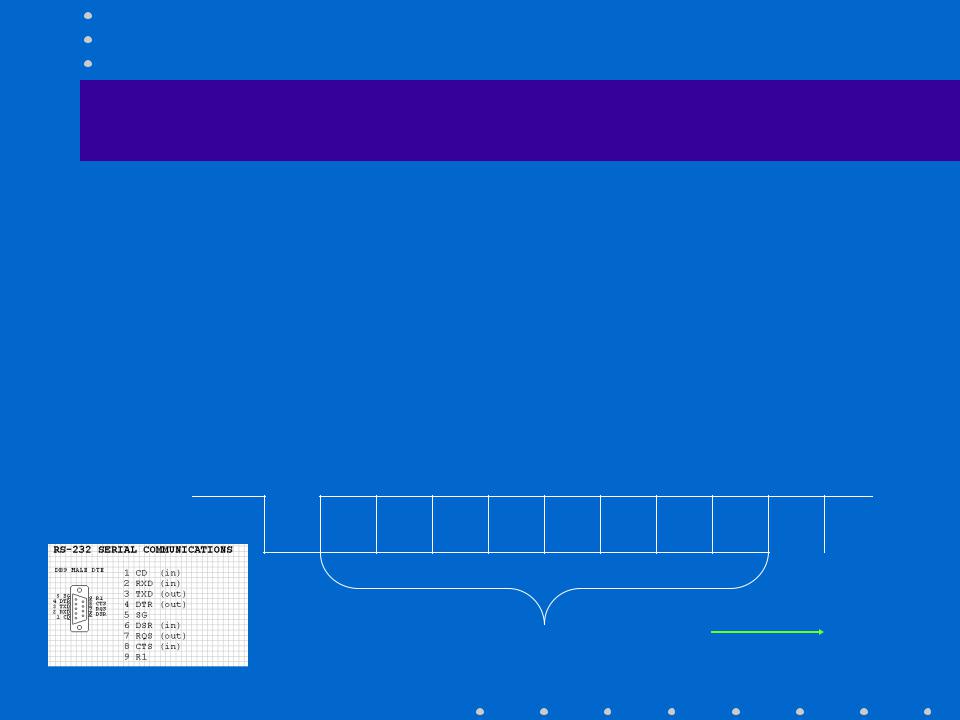

application

•Sampled speech: 8k samples/sec of 8 bit each

–converted into serial stream of 64 kbit/s

•Computer serial output bus (e.g. RS-232)

0 |

1 |

|

time

data

A.J. Han Vinck |

56 |

|

|

|

|

|

|

|

binary Linear Feedback Shift Register

• application in cryptography

2 delay elements or flip-flops (we do not draw the clock anymore)

1 0 output

|

XOR or modulo 2 |

• Homework: |

calculations |

–what is in general the maximum period of the output

–Calculate the output sequence

A.J. Han Vinck |

57 |

|

|

|

|

|

|

|

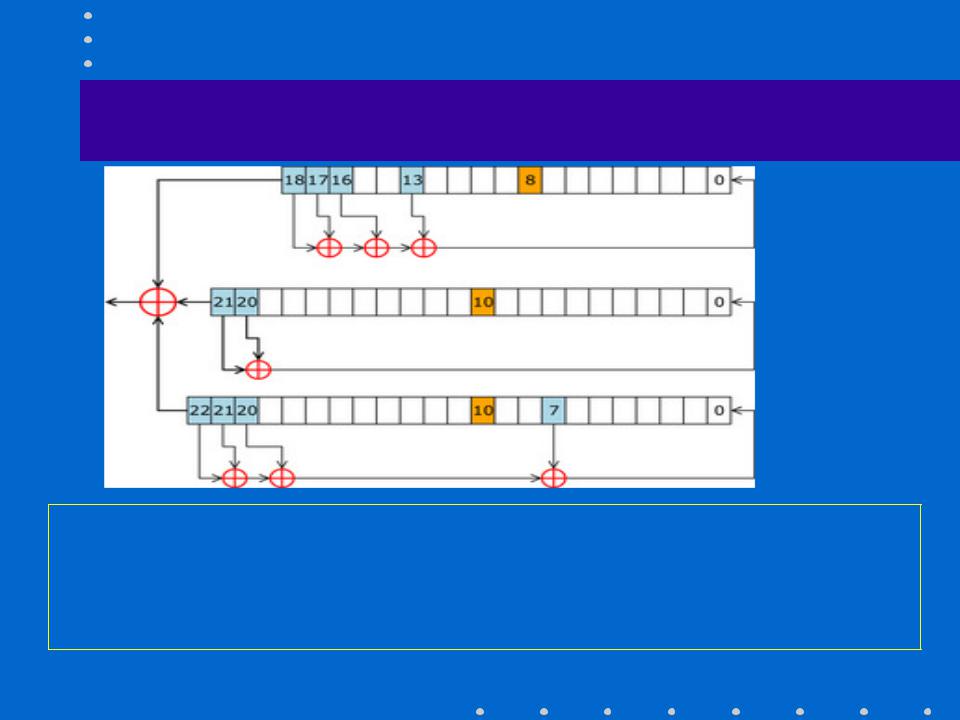

GSM randomizer A5/1

http://en.wikipedia.org/wiki/A5/1

The A5/1 stream cipher uses three LFSRs. A register is clocked if its clocking bit (orange) agrees with the majority of the clocking bits of all three registers.

Hence at each step two or three registers are clocked, and each register steps with probability 3/4.

Ekdahl and Johannson (2003) published an attack on the initialisation procedure which breaks A5/1 in a few minutes using 2–5 minutes of conversation plaintext.

A.J. Han Vinck |

58 |

|

|

|

|

|

|

|

Multiplication (basic version)

Multiplicand (32 bits)

Register 64 bits

1 1 0 1 multiplicand

Shift left

1 0 1 1 multiplier

64 bits adder |

|

Multiplier(32 bits) |

1 1 0 1 |

|

|

|

Register 32 bits |

|

|

|

|

|

|

|

1 1 0 1 0 |

shift +1 |

|

|

|

last bit |

|

||

|

|

|

|

|

|

|

|

Shift right |

|

1 1 0 1 0 0 0 |

shift +3 |

|

|

|

|

||

Intermediate result |

|

control |

1 0 0 0 1 1 1 1 |

sum |

|

Register 64 bits |

save |

|

|||

A.J. Han Vinck |

59 |

|

|

|

|

|

|

|

What good are counters?

•Counters can act as simple clocks to keep track of “time.”

•You may need to record how many times something has happened.

–How many bits have been sent or received?

–How many steps have been performed in some computation?

•All processors contain a program counter, or PC.

–Programs consist of a list of instructions that are to be executed one after another (for the most part).

–The PC keeps track of the instruction currently being executed.

–The PC increments once on each clock cycle, and the next program instruction is then executed.

A.J. Han Vinck |

60 |

|

|

|

|

|

|

|