dsd1-10 / dsd-07=Verilog / Лабораторная работа2

.docЛабораторная работа №2

Поведенческое описание цифрового компаратора и мажоритарного элемента.

Целью данной работы является получение начальных навыков проектирования простейших элементов цифровых устройств посредством описания их на языке VerilogHDL на примере простых устройств.

Работа выполняется на рабочей станции SUN под операционной системой Solaris.

Задание на выполнение работы:

Составить таблицу истинности на устройство указанное в вариантах лабораторной работы №1.

Осуществить вход на рабочую станцию введением login и password.

Создать рабочую папку verilog_lab2 в директории project.

>cd project

>mkdir verilog_lab2

>cd verilog_lab2

Открыть в терминале текстовый редактор nedit.

>nedit my_file.v

В ходе выполнения работы необходимо написать Verilog файл цифрового устройства по варианту используя таблицу истинности, а также Verilog файл test bench для проведения функционально-логического моделирования.

Моделирование производится в среде CADENCE ncverilog. Для этого в командной строке терминала вводится следующее:

> ncverilog +gui +access+rwc my_file.v test_bench.v

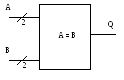

Цифровой компаратор – комбинационная схема, которая выполняет функцию сравнения (равно, больше, меньше) двух входных сигналов данных. Входным сигналом могут являться любые два числа одинаковой разрядности, представленные в бинарном виде. Выходом компаратора обычно является однобитное число, которое принимает, например значение «1» если утверждение истинно и значение «0», если утверждение ложно.

Пример описания компаратора двух двухразрядных чисел, выход компаратора принимает значение «1», когда А и В равны:

m odule

COMP (A, B, Q);

odule

COMP (A, B, Q);

input [1:0] A,B;

output Q;

assign Q=(A= =B) ? 1:0;

endmodule

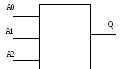

Мажоритарный элемент – комбинационная схема, которая выполняет функцию «голосования», т.е. данное устройство выдает на выходе значение «1» в случае если во входном слове больше единиц, или наоборот выдает на выходе значение «0» в случае если во входном слове больше нулей. Данный Элемент имеет одну особенность, а именно входное слово должно имен нечетное число разрядов

module MAJOR (A, Q);

i nput

[2:0] A;

nput

[2:0] A;

output Q;

assign Q=(A=3’b111|

A=3’b110|

A=3’b011|

A=3’b101) ? 1:0;

endmodule

|

№ |

Описание задания |

|

1 |

Устройство, которое выдает на выходе наибольшее из 3-х входных десяти разрядных чисел |

|

2 |

наибольшее из 4-х входных десяти разрядных чисел |

|

3 |

наибольшее из 5-х входных десяти разрядных чисел |

|

4 |

Устройство, которое выдает на выходе наименьшее из 3-х входных десяти разрядных чисел |

|

5 |

наименьшее из 4-х входных десятиразрядных чисел |

|

6 |

наименьшее из 5-х входных десятиразрядных чисел |

|

7 |

Устройство, которое выдает на выходе наибольшее из 3-х входных десяти старших разрядов двадцатитрех рядных чисел |

|

8 |

наибольшее из 4-х входных десяти старших разрядов двадцатитрех рядных чисел |

|

9 |

наибольшее из 5-х входных десяти старших разрядов двадцатитрех рядных чисел |

|

0 |

Устройство, которое выдает на выходе наименьшее из 3-х входных десяти старших разрядов двадцатитрех рядных чисел |

|

11 |

наименьшее из 4-х входных десяти старших разрядов двадцатитрех рядных чисел |

|

12 |

Наименьшее из 5-х входных десяти старших разрядов двадцатитрех рядных чисел |

|

13 |

Устройство, которое выдает на выходе наибольшее из 3-х входных двадцатитрех рядных чисел |

|

14 |

наибольшее из 4-х входных двадцатитрех рядных чисел |

|

15 |

наибольшее из 5-х входных двадцатитрех рядных чисел |

|

16 |

Устройство, которое выдает на выходе наименьшее из 3-х входных двадцатитрех рядных чисел |

|

17 |

наименьшее из 4-х входных двадцатитрех рядных чисел |

|

18 |

Наименьшее из 5-х входных двадцатитрех рядных чисел |

|

19 |

Устройство, которое выдает на выходе наибольшее из дополнительных кодов 3-х входных десяти разрядных чисел |

|

20 |

наибольшее из дополнительных кодов 4-х входных чисел десяти разрядных чисел |

|

21 |

наибольшее из дополнительных кодов 5-х входных чисел десяти разрядных чисел |

|

22 |

Устройство, которое выдает на выходе наименьшее из дополнительных кодов 3-х входных чисел десяти разрядных чисел |

|

23 |

наименьшее из дополнительных кодов 4-х входных чисел десяти разрядных чисел |

|

24 |

Наименьшее из дополнительных кодов 5-х входных чисел десяти разрядных чисел |

|

25 |

Устройство, которое выдает на выходе наибольшее из дополнительных кодов 3-х входных двадцати трех разрядных чисел |

|

26 |

наибольшее из дополнительных кодов 4-х входных чисел двадцати трех разрядных чисел |

|

26 |

наибольшее из дополнительных кодов 5-х входных чисел двадцати трех разрядных чисел |

|

№ |

Описание задания |

|

1-6 |

Описать мажоритарный элемент на 11 входов |

|

7-13 |

Описать мажоритарный элемент на 13 входов |

|

14-20 |

Описать мажоритарный элемент на 15 входов |

|

21-26 |

Описать мажоритарный элемент на 17 входов |