- •Глава 6. Примеры проектирования цифровых устройств с использованием языков описания аппаратуры vhdLиVerilog.

- •6.1. Общие сведения

- •6.2. Триггеры и регистры (Flip-Flops, Registers)

- •6.3. Построение устройств потоковой обработки данных (Datapath logic)

- •6.4. Счетчики

- •6.5. Арифметические устройства

- •6.6.Конечные автоматы (Finite State Machine)

- •6.7. Элементы ввода – вывода

- •6.8.Параметризация

- •6.9. Спрецифика проектирования устройств с учетом архитектурных особенностей плис

- •6.10. Совместное использование ресурсов

- •6.12. Дублирование регистра.

- •6.13.Создание описаний с учетом особенностей архитектуры плис (Technology Specific Coding Techniques).

Глава 6. Примеры проектирования цифровых устройств с использованием языков описания аппаратуры vhdLиVerilog.

6.1. Общие сведения

Языки описания аппаратуры VHDL и Verilog HDL представляют собой языки высокого уровня (в отличие от AHDL и ABEL HDL) и предназначены для описания цифровых схем и их элементов в первую очередь на поведенческом уровне.

Эти языки поддерживают различные уровни абстракции проекта, включая поддержку особенностей архитектуры ПЛИС, под которую выполняется проект (architecture-specific design). Использование языков описания аппаратуры высокого уровня позволяет проектировать цифровые системы, обладающие высокой мобильностью, то есть возможностью переносимости на другую элементную базу. Для создания законченного проекта необходимо только лишь произвести компиляцию в соответствующей системе в элементную базу выбранного производителя. Но в этом и основной недостаток языков высокого уровня – недостаточный учет специфических архитектурных особенностей используемой элементной базы (specific target technology). В этом разделе мы попытаемся рассмотреть некоторые примеры использования языков описания аппаратуры для создания проектов различного уровня сложности.

При проведении синтеза логической структуры ПЛИС с использованием языков описания аппаратуры (HDL synthesis-based design flow) различают четыре основных стадии проектирования:

Создание и функциональная верификация проекта;

Реализация проекта в САПР ПЛИС;

Программирование ПЛИС

Верификация всей системы

При функциональной верификации проекта ввод описания проекта осуществляется на регистровом уровне (RTL-level) в поведенческой области (behavioral). После ввода описания проекта поведенческое (функциональное) моделирование (верификация) позволяют оценить степень правильности функционирования алгоритма. После проведения функционального моделирования, описание синтезируется в список цепей на вентильном уровне (gate-level) в структурной области (structural). После осуществленимя синтеза можно выполнеть структурное (временное и функциональное) моделирование устройства. В результате мы получаем список цепей (как правило, в формате EDIF) для временной верификации проекта.

Рассмотрим применение языков описания аппаратуры высокого уровня (VHDL и Verilog HDL) для описания различных цифровых устройств. Данные описания, если не указывается особо, не ориентированы на какую-либо конкретную систему проектирования или семейство ПЛИС и могут быть воплощены в различных базисах. Такой тип описаний получил название независимого от технологии стиля описания устройств (Technology Independent Coding Styles). Начнем рассмотрение способов описания независимых от технологии устройств с последовательностных устройств (Sequential Devices). В англоязычной литературе приняты термины защелка (latch) для устройств, тактируемых уровнем, и триггер (flip-flop) для устройств, тактируемым фронтом тактового импульса.

6.2. Триггеры и регистры (Flip-Flops, Registers)

Для описания триггерных схем в VHDL используются операторы wait и if вместе с процессом, использующим аттрибуты переднего или заднего фронтов синхроимпульса (см. Главу 4).

Ниже приведены примеры создания описаний срабатывания по фронту:

(clk'event and clk='1') –аттрибут срабатывания по переднему фронту

(clk'event and clk='0') -- аттрибут срабатывания по заднему фронту

rising_edge(clock) –вызов функции по переднему фронту

falling_edge(clock) -- вызов функции по заднему фронту

В этих примерах иллюстрируется применение аттрибута переднего фронта (rising edge 'event attribute). Использование аттрибутов следует рекомендовать в тех случаях, когда система проектирования не поддерживает вызов функции по событию. Однако , использование функций позволяет избежать коллизий, связанных с переходом из неопределенного состояния, поскольку функция определяет только переходы уровней (из 0 в 1 или из 1 в 0), не не переход из неопределенного состояния в 1 или 0. Это становиться достаточно важным в случае использования многозначных типов данных, например std_logic, который имеет 9 возможных значений(U, X, 0, 1, Z, W, L, H, -). Далее рассмотрим основные типы триггеров.

Триггеры, тактируемые передним фронтом (Rising Edge Flip-Flop)

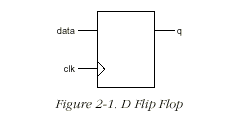

Ниже приводиться пример описания D триггера без цепей асинхронного сброса (reset) или предустановки (preset). На Рис. 1 приведено схемное обозначение рассматриваемого триггера.

Рис.6.1

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff is

port (data, clk : in std_logic;

q :out std_logic);

end dff;

architecture behav of dff is

begin

process (clk) begin

if (clk'event and clk = '1') then

q <= data;

end if;

end process;

end behav;

Описание на Verilog

module dff (data, clk, q);

input data, clk;

output q;

reg q;

always @(posedge clk)

q = data;

endmodule

Триггеры, тактируемые передним фронтом с асинхронным сбросом (Rising Edge Flip-Flop with Asynchronous Reset)

Обозначение устройства приведено на Рис.6.2

Рис.6.2.

Пример описания на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff_async_rst is

port (data, clk, reset : in std_logic;

q :out std_logic);

end dff_async_rst;

architecture behav of dff_async_rst is

begin

process (clk, reset) begin

if (reset = '0') then

q <= '0';

elsif (clk'event and clk = '1') then

q <= data;

end if;

end process;

end behav;

Пример описания на Verilog

module dff_async_rst (data, clk, reset, q);

input data, clk, reset;

output q;

reg q;

always @(posedge clk or negedge reset)

if (~reset)

q = 1'b0;

else

q = data;

endmodule

Триггеры, тактируемые передним фронтом с асинхронной предустановкой (Rising Edge Filp-Flop with Asynchronous Preset)

Обозначение устройства на схеме приведено на Рис.6.3

Рис.6.3

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff_async_pre is

port (data, clk, preset : in std_logic;

q :out std_logic);

end dff_async_pre;

architecture behav of dff_async_pre is

begin

process (clk, preset) begin

if (preset = '0') then

q <= '1';

elsif (clk'event and clk = '1') then

q <= data;

end if;

end process;

end behav;

Описание на Verilog

module dff_async_pre (data, clk, preset, q);

input data, clk, preset;

output q;

reg q;

always @(posedge clk or negedge preset)

if (~preset)

q = 1'b1;

else

q = data;

endmodule

Триггеры, тактируемые передним фронтом с асинхронным сбросом и предустановкой (Rising Edge Filp-Flop with Asynchronous Reset and Preset)

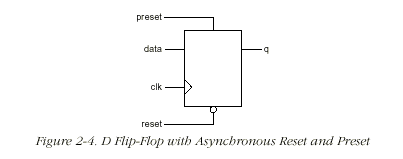

Обозначение на схеме приведено на Рис.6.4

Рис.6.4

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff_async is

port (data, clk, reset, preset : in std_logic;

q :out std_logic);

end dff_async;

architecture behav of dff_async is

begin

process (clk, reset, preset) begin

if (reset = '0') then

q <= '0';

elsif (preset = '1') then

q <= '1';

elsif (clk'event and clk = '1') then

q <= data;

end if;

end process;

end behav;

Описание на Verilog

module dff_async (reset, preset, data, q, clk);

input clk;

input reset, preset, data;

output q;

reg q;

always @(posedge clk or negedge reset or posedge preset)

if (~reset)

q = 1'b0;

else if (preset)

q = 1'b1;

else q = data;

endmodule

Триггеры, тактируемые передним фронтом с синхронным сбросом (Rising Edge Filp-Flop with Synchronous Reset)

Обозначение на схеме приведено на Рис.6.5

Рис.6.5.

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff_sync_rst is

port (data, clk, reset : in std_logic;

q :out std_logic);

end dff_sync_rst;

architecture behav of dff_sync_rst is

begin

process (clk) begin

if (clk'event and clk = '1') then

if (reset = '0') then

q <= '0';

else q <= data;

end if;

end if;

end process;

end behav;

Описание на Verilog

module dff_sync_rst (data, clk, reset, q);

input data, clk, reset;

output q;

reg q;

always @(posedge clk)

if (~reset)

q = 1'b0;

else q = data;

endmodule

Триггеры, тактируемые передним фронтом с синхронной предустановкой (Rising Edge Filp-Flop with Synchronous Preset)

Обозначение на схеме приведено на Рис.6.6

Рис.6.6

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff_sync_pre is

port (data, clk, preset : in std_logic;

q :out std_logic);

end dff_sync_pre;

architecture behav of dff_sync_pre is

begin

process (clk) begin

if (clk'event and clk = '1') then

if (preset = '0') then

q <= '1';

else q <= data;

end if;

end if;

end process;

end behav;

Описание на Verilog

module dff_sync_pre (data, clk, preset, q);

input data, clk, preset;

output q;

reg q;

always @(posedge clk)

if (~preset)

q = 1'b1;

else q = data;

endmodule

Триггеры, тактируемые передним фронтом с асинхронным сбросом и разрешением тактового сигнала (Rising Edge Filp-Flop with Asynchronous Reset and Clock Enable)

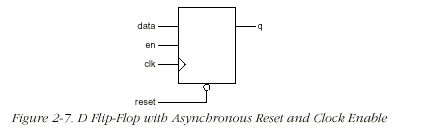

Пример схемного обозначения приведен на Рис.6.7

Рис.6. 7.

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff_ck_en is

port (data, clk, reset, en : in std_logic;

q :out std_logic);

end dff_ck_en;

architecture behav of dff_ck_en is

begin

process (clk, reset) begin

if (reset = '0') then

q <= '0';

elsif (clk'event and clk = '1') then

if (en = '1') then

q <= data;

end if;

end if;

end process;

end behav;

Описание на Verilog

module dff_ck_en (data, clk, reset, en, q);

input data, clk, reset, en;

output q;

reg q;

always @(posedge clk or negedge reset)

if (~reset)

q = 1'b0;

else if (en)

q = data;

endmodule

Далее рассмотрим защелки на основе D-триггеров (D-Latches)

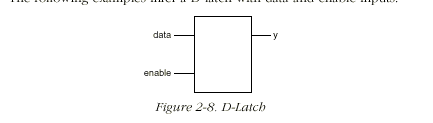

Защелка с разрешением выхода (D-Latch with Data and Enable)

Обозначение на схеме приведено на Рис.6.8

Рис.6.8

Описание на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity d_latch is

port(enable, data: in std_logic;

y :out std_logic);

end d_latch;

architecture behave of d_latch is

begin

process (enable, data)

begin

if (enable = '1') then

y <= data;

end if;

end process;

end behave;

Описание на Verilog

module d_latch (enable, data, y);

input enable, data;

output y;

reg y;

always @(enable or data)

if (enable)

y = data;

endmodule

Защелка с входом данных с разрешением (D-Latch with Gated Asynchronous Data)

Пример обозначения приведен на Рис.6.9

Рис.6.9.

Пример на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity d_latch_e is

port (enable, gate, data : in std_logic;

q :out std_logic);

end d_latch_e;

architecture behave of d_latch_e is

begin

process (enable, gate, data) begin

if (enable = '1') then

q <= data and gate;

end if;

end process;

end behave;

Пример на Verilog

module d_latch_e(enable, gate, data, q);

input enable, gate, data;

output q;

reg q;

always @ (enable or data or gate)

if (enable)

q = (data & gate);

endmodule

Защелка с входом разрешения (D-Latch with Gated Enable) (Рис.6.10)

Рис.6.10

Пример на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity d_latch_en is

port (enable, gate, d: in std_logic;

q :out std_logic);

end d_latch_en;

architecture behave of d_latch_en is

begin

process (enable, gate, d) begin

if ((enable and gate) = '1') then

q <=d;

end if;

end process;

end behave;

Пример на Verilog

module d_latch_en(enable, gate, d, q);

input enable, gate, d;

output q;

reg q;

always @ (enable or d or gate)

if (enable & gate)

q =d;

endmodule

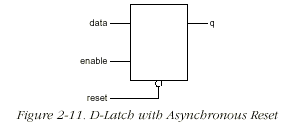

Защелка с асинхронным сбросом (D-Latch with Asynchronous Reset) (Рис.6.11)

Рис.6.11.

Пример описания на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity d_latch_rst is

port (enable, data, reset: in std_logic;

q :out std_logic);

end d_latch_rst;

architecture behav of d_latch_rst is

begin

process (enable, data, reset) begin

if (reset = '0') then

q <= '0';

elsif (enable = '1') then

q <= data;

end if;

end process;

end behav;

Пример описания на Verilog

module d_latch_rst (reset, enable, data, q);

input reset, enable, data;

output q;

reg q;

always @ (reset or enable or data)

if (~reset)

q = 1'b0;

else if (enable)

q = data;

endmodule