- •Глава 6. Примеры проектирования цифровых устройств с использованием языков описания аппаратуры vhdLиVerilog.

- •6.1. Общие сведения

- •6.2. Триггеры и регистры (Flip-Flops, Registers)

- •6.3. Построение устройств потоковой обработки данных (Datapath logic)

- •6.4. Счетчики

- •6.5. Арифметические устройства

- •6.6.Конечные автоматы (Finite State Machine)

- •6.7. Элементы ввода – вывода

- •6.8.Параметризация

- •6.9. Спрецифика проектирования устройств с учетом архитектурных особенностей плис

- •6.10. Совместное использование ресурсов

- •6.12. Дублирование регистра.

- •6.13.Создание описаний с учетом особенностей архитектуры плис (Technology Specific Coding Techniques).

6.10. Совместное использование ресурсов

Другим путем повышения эффективности описаний цифровых устройств является совместное использование ресурсов (Resource Sharing). Совместное использование ресурсов позволяет снизить число логических элементов для реализации операторов на языках описания аппаратуры. Ниже приводяться два примера совместного использования ресурсов. Примеры написаны на

Пример 1. Реализация четырех сумматоров (счетчиков)

if (...(siz == 1)...)

count = count + 1;

else if (...((siz ==2)...)

count = count + 2;

else if (...(siz == 3)...)

count = count + 3;

else if (...(siz == 0)...)

count = count + 4;

Покажем, как можно избавиться от двух «лишних» счетчиков

if (...(siz == 0)...)

count = count + 4;

else if (...)

count = count + siz

Пример 2. В данном примере используется неполное совместное использование ресурсов для реализации сумматоров (Рис.6.23).

Рис.6.23.

if (select)

sum<=A +B;

else

sum<=C +D;

Сумматоры занимают значительные ресурсы, для их уменьшения переписываем код с целью ввести два мультиплексора и один сумматор, как показано ниже (Рис.6.24).

Рис.6. 24.

if (sel)

temp1 <= A;

temp2 <= B;

else

temp1 <= C;

temp2 <= D;

sum <= temp1 + temp2;

Следует помнить, что в данном примере сигнал выбора «sel» не является запаздывающим сигналом

Еще одним способом организации совместного использования ресурсов является использование операторов цикла

Арифметические операторы и мультиплексоры занимают значительные ресурсы. Если имеется оператор внутри цикла, программа синтеза должна оценить все состояния. В следующем примере на языке VHDL описываются четыре сумматора и один мультиплексор. Такая реализация может быть рекомендована только, если сигнал выбора "req" – запаздывающий сигнал (Рис.6.25).

Рис.6.25.

vsum := sum;

for i in 0 to 3 loop

if (req(i)='1') then

vsum <= vsum + offset(i);

end if;

end loop;

Если сигнал выбора “req” не является критическим, оператор может быть вынесен за пределы цикла, что приведет к тому, что вместо четырех сумматоров будет использован один (Рис.6.26)

Рис.6.26

Пример описания приведен ниже

vsum := sum;

for i in 0 to 3 loop

if (req(i)='1') then

offset_1 <= offset(i);

end if;

end loop;

vsum <= vsum + offset_1;

Использование кодирования для сочетаемости (Coding for Combinability)

Использование кодирования для сочетаемости (Coding for Combinability) также позволяет выкроить ресурсы ПЛИС.

Для ПЛИС некоторых архитектур возможно выполнение всей логики работы, как комбинационной, так и последовательностной в пределах одного логического элемента (ячейки), что значительно снижает задержки по критическим путям и экономит ресурсы.

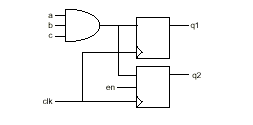

Однако следует помнить, что такое объединение возможно только в том случае, если комбинационная схема управляет только одним триггером. В приведенном примере описания на VHDL элемент AND формирует управляющий сигнал для двух триггеров (Рис.6.27), что препятствует введению элемента AND в последовательностный модуль

Рис.6.27

one :process (clk, a, b, c, en) begin

if (clk'event and clk ='1') then

if (en = '1') then

q2 <= a and b and c;

end if;

q1 <= a and b and c;

end if;

end process one;

Для того, чтобы объединить схему внутри одного элемента и убрать внешние цепи удобно использовать дублирование логического элемента AND, уменьшая тем самым критические пути распространения сигнала (Рис.6.28).

Рис.6.28.

part_one: process (clk, a, b, c, en) begin

if (clk'event and clk ='1') then

if (en = '1') then

q2 <= a and b and c;

end if;

end if;

end process part_one;

part_two: process (clk, a, b, c) begin

if (clk'event and clk ='1') then

q1 <= a and b and c;

end if;

end process part_two;