- •Интегральная микросхема. Определение виды и типы имс. Способы их изготовления. Степень интеграции.

- •Фоторезистор, назначение, структура. Вольтамперная характеристика.

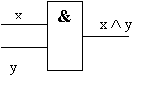

- •3. Таблица истинности логического элемента и.

- •4. Операционный усилитель в схеме инвертирующего усилителя. Схема , коэффициент усиления. Вид обратной связи. Передаточная характеристика.

- •Неинвертирующая схема оу. Схема, коэф.Усиления. Передаточная хар-ка. Вид обратной связи

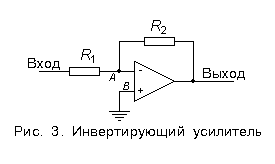

- •Синхронный триггер сrs (rst)-типа на базе лэ и-не

- •Дифференциальная схема выполнения оу. Назначение. Коэффициент усиления.

- •Релейно-контакторный эквивалент логического элемента и.

- •Дифференциатор на базе оу. Назначение. Привести диаграмму выходного напряжения если на вход подано напряжение типа треугольник.

- •Светодиод, назначение, схема включения в электрическую цепь, яркостная характеристика.

- •Оптрон. Назначение. Блок схема простейшего оптрона.

- •Преобразоватеь напряжения в напряжение на базе инвертирующей схемы оу. Входные выходные сопротивления, коэффициент усиления.

- •Тиристор, назначение, структура, Схема включения, вах, способ управления.

- •Релейно-контакторная схема логического элемента или

- •Преобразователь тока в напряжение на оу. Схема пояснения. Передаточная характеристика.

- •Фоторезисторный оптрон

- •Релейно-контакторный эквивалент логического элемента и-не

- •Усилитель мощности на базе инвертирующего оу и усилителя тока на комплементарных транзисторах. Назначение элементов схемы. Назначение обратной связи. Передаточная характеристика.

- •Логические переменные и логические функции. Способы их задания.

- •Счетчик импульсов с модулем счета 2 на базе т-триггера

- •Составные транзисторы. Схема. Назначение. Коэффициент усиления.

- •Основной логический базис для построения логических схем.

- •Шифратор. Назначение. Принцип построения.

- •Счетчики импульсов. Назначение. Коэффициент счета.

- •Релейно-контакторный эквивалент логического элемента или – не.

- •Регистр сдвига. Назначение. Схема трехразрядного сдвигового регистра вправо.

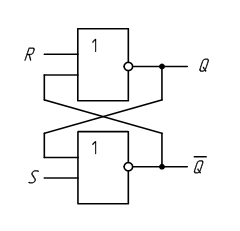

- •Обозначение и структурная формула логического элемента и.

- •Фотодиодный оптрон.

- •Операционные усилители. Обозначение, маркировки. Достоинства и недостатки

- •Интегральная микросхема. Определение виды и типы имс. Способы их изготовления. Степень интеграции.

3. Таблица истинности логического элемента и.

Схема

И реализует конъюнкцию (логическое

умножение) двух или более логических

значений.

Эл схема

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет нуль, на выходе также будет нуль. Связь между выходом z этой схемы и входами х и у описывается соотношением z = х ^ у (читается как «х и у»). Операция конъюнкции на функциональных схемах обозначается знаком & (читается как «амперсэнд»

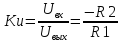

4. Операционный усилитель в схеме инвертирующего усилителя. Схема , коэффициент усиления. Вид обратной связи. Передаточная характеристика.

Операционным усилителем (ОУ) называют усилитель напряжения, предназначенный для выполнения различных операций с аналоговыми сигналами: их усиление или ослабление, сложение или вычитание, интегрирование или дифференцирование, логарифмирование или потенцирование, преобразование их формы и др. Все эти операции ОУ выполняет с помощью цепей положительной и отрицательной обратной связи, в состав которых могут входить сопротивления, емкости и индуктивности, диоды, стабилитроны, транзисторы и некоторые другие электронные элементы. Поскольку все операции, выполняемые при помощи ОУ, могут иметь нормированную погрешность, то к его характеристикам предъявляются определенные требования.

Схема инвертирующего усилителя приведена на рис. 8.6 а. На инвертирующий вход ОУ в этой схеме подается сигнал, определяемый суммой входного и выходного напряжений и делителем на сопротивлениях R1 и R2. Так как неинвертирующий вход ОУ соединен с общим выводом, a Uдиф=0, то напряжение на инвертирующем входе также будет равно нулю. В результате для схемы рис. 8.6 а можно записать уравнение:

откуда находим коэффициент усиления усилителя:

-

RS-триггер на элементах ИЛИ-НЕ Логическая структура. Таблица переключений триггера. Запрещенная комбинация

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

-

R - установка 0 (от слова reset);

-

S - установка 1 (от слова set).

RS-триггер имеет два выхода:

-

Q - прямой;

-

Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью (рисунок 2.1).

Рисунок 2.1 - Схема простейшего RS- триггера

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль - со входа R, другой - с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

-

Q(t) - состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

-

Q(t+1) - состояние триггера после изменения на входах R и S.

Таблица 2.1 - Таблица переходов RS триггера в базисе ИЛИ-НЕ

|

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

0 |

0 |

0 |

Режим хранения информации R=S=0 |

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

Режим установки нуля R=1 |

|

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

* |

R=S=1 запрещённая комбинация |

|

1 |

1 |

1 |

* |

-

Таблица истинности логического элемента ИЛИ.

Схема ИЛИ реализует дизъюнкцию (логическое сложение) двух или более логических значений.

|

|

Эл. схема

|

|

Таблица истинности |

||

|

х |

y |

х или у |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

10 |

|

1 |

1 |

1 |

Когда хотя бы на одном входе схемы ИЛИ будет единица, на ее выходе также будет единица. Знак «1» на схеме — от устаревшего обозначения дизъюнкции как «>=!» (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами х и у описывается соотношением z = х или у.