1.4 Перетворювачі кодів

Перетворювачі кодів використовуються для шифрації та дешифрації цифрової інформації і перетворюють n-елементний код в m-елементний. Співвідношення між числами n та m можуть бути різними: n=m, n>m, n<m.

Перетворювач кодів – це комбінаційна схема , яка перетворює вхідний код Х у вихідний У.

Існують такі перетворювачі кодів:

1.Шифратори;

2.Дешифратори;

3.Перетворювачі кодів для управління семисегментним індикатором.

Перетворювач двійкового чотири розрядного коду в код Грея

Недоліком деяких перетворень є наявність переходів типу 1000-0111-1000, котрі збільшують час перетворення, а також затримується знімання інформації. Від цього недоліку озбавлені перетворювачі працюючі в коді Грея. Він характерезуються тим, що кожна слідуюча його кодова комбінація відрізняється від попередньої в одному розряді, при цьому перша і остання кодова операція відрізняється також одним розрядом. Циклічним кодом Грея можно закодувати тільки парну кількість цифр. Цей код можна побудувати використовуючи карту Карно:

y1=f1(x1,x2,x3,x4) y2=f2(x1,x2,x3,x4)

y3=f3(x1,x2,x3,x4) y4=f4(x1,x2,x3,x4)

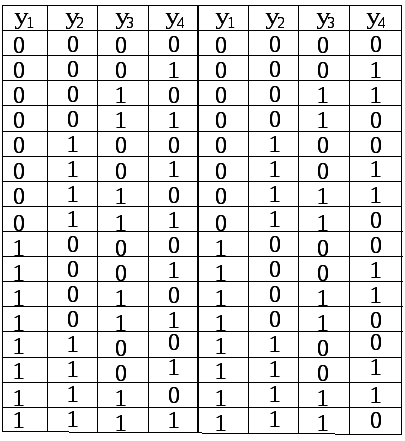

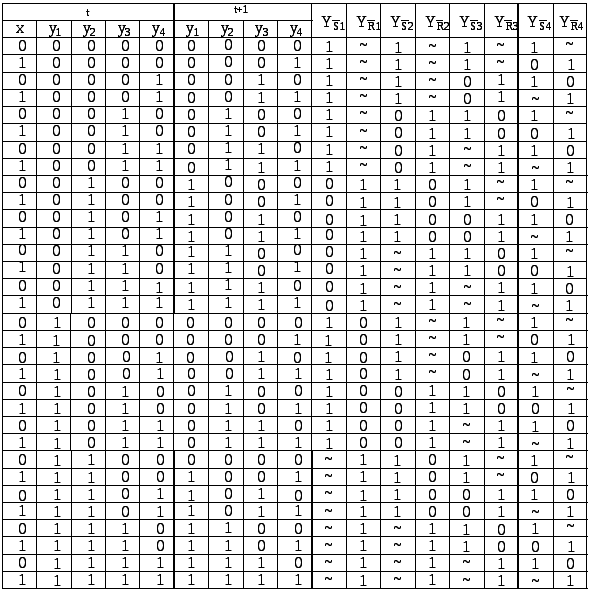

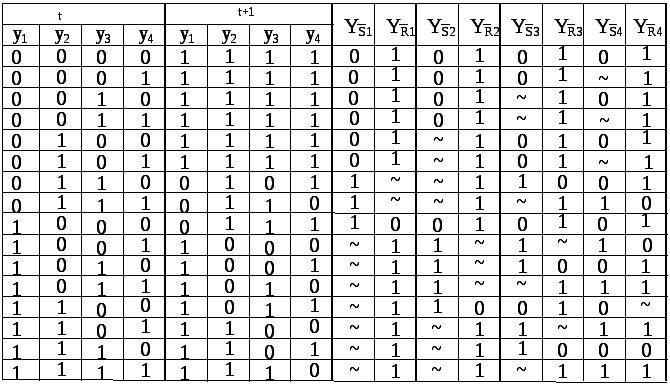

Таблиця 1.5 - Таблиця істинності

По

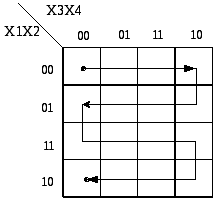

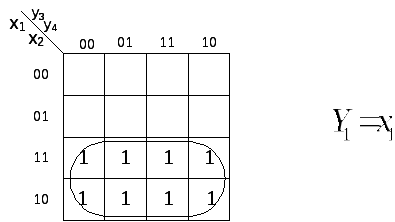

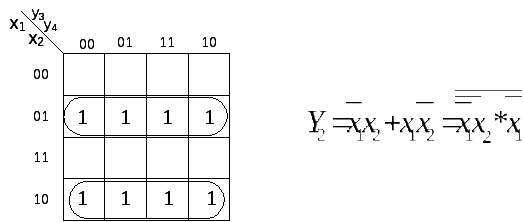

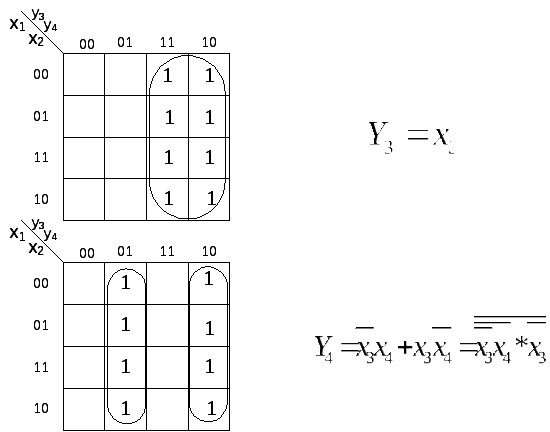

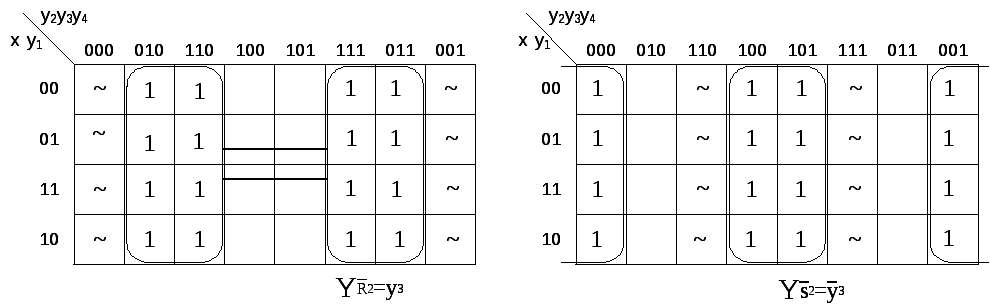

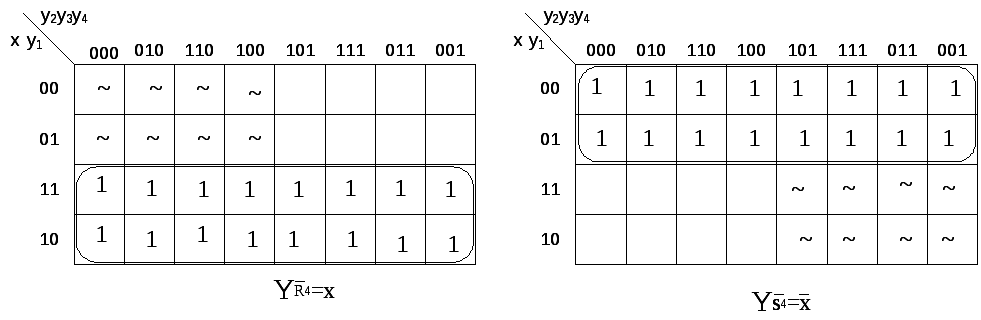

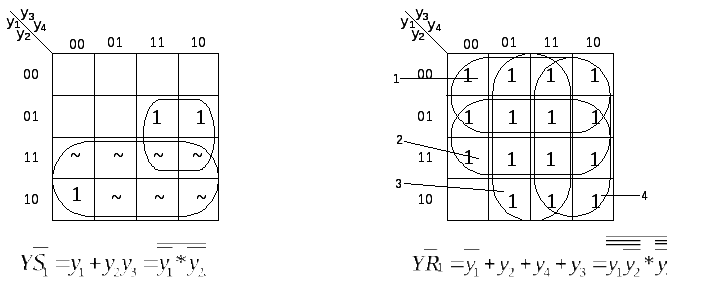

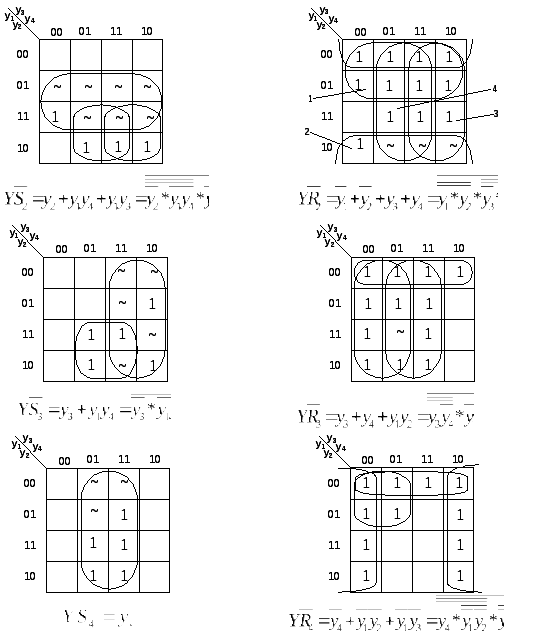

таблиці будуємо карти Карно:

Рисунок 1.6 – Карти Карно

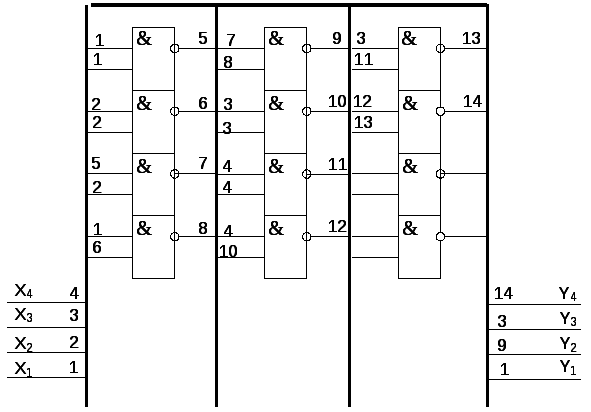

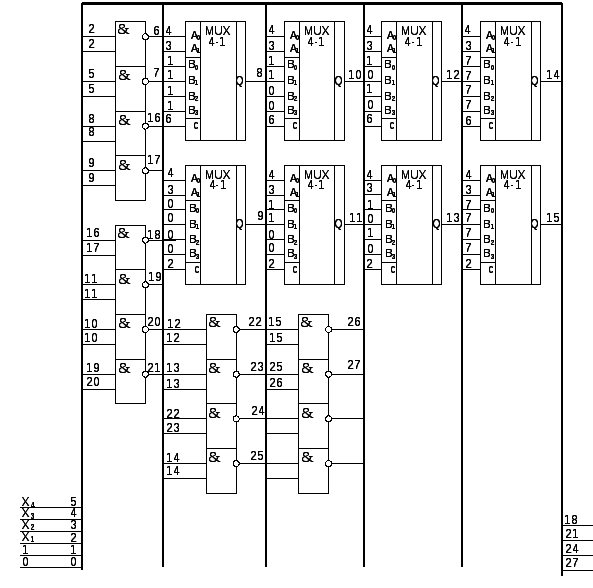

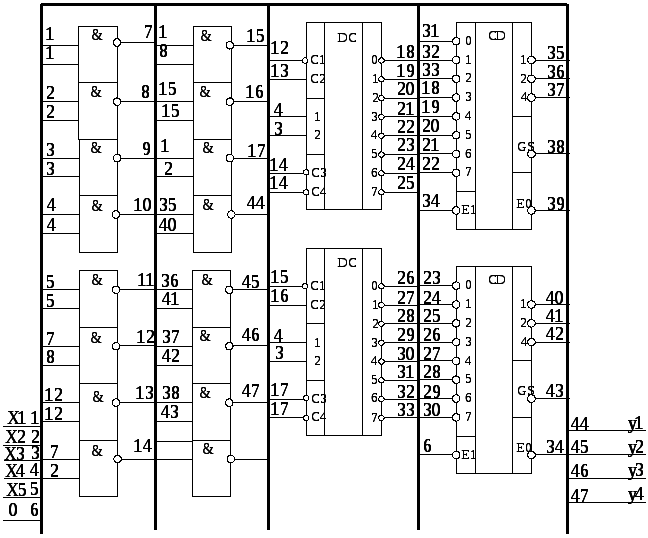

Рисунок 1.7 – Перетворювач кодів

б) Перетворювач чотирирозрядного двійкового коду в зворотній код

Зворотній код отримується шляхом інвертування кожного розряду.

Схема будується на мультиплексорах, тому у зв’язку з цим будується така таблиця істинності:

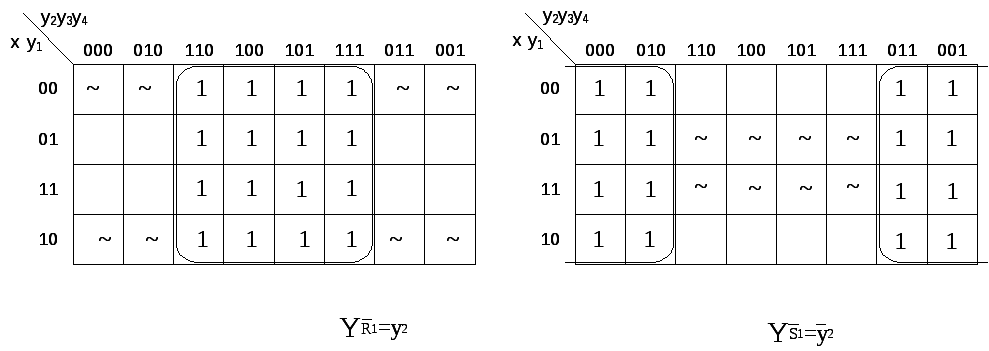

Таблиця 1.6 - Таблиця істинності

Тепер

будуємо схему перетворювача чотирирозрядного

двійкового коду в зворотній код:

Тепер

будуємо схему перетворювача чотирирозрядного

двійкового коду в зворотній код:

Рисунок 1.9 – Перетворювач кодів

в)

Перетворювач коду 8-4-2-1 в код 8-4-2-1 з

надлишком 3

в)

Перетворювач коду 8-4-2-1 в код 8-4-2-1 з

надлишком 3

Перетворювачі кодів з надлишком 3 мають код в такті t+1 на 3 порядки звинутий, у порівнянні з тактом t, тому їх будують на кодерах та декодерах. Коди надходять на декодер, вихідні сигнали з декодера потрапляють на входи кодера здвинуті на 3 порядки, з виходів кодера виходять перетворені коди.

Таблиця істинності:

Таблиця 1.7 - Таблиця істинності

Будуємо

схему:

Будуємо

схему:

Рисунок 1.10 – Перетворювач кодів

2 Автомат із пам’яттю.

Для побудови послідовного автомата заданого в умові, необхідно запам'ятовувати деякі сигнали. І ми будемо використовувати автомати з пам'яттю (АП). Дискретні АП характеризуються тим, що стан їх виходів залежить як від сигналів, присутніх на їх входах в даний момент часу, так і від послідовності сигналів, що поступили на входи автомата в попередній момент часу.

Автомат складається із комбінаційної схеми та елементів пам’яті. На вхід комбінаційної схеми надходять сигнали X1,…, Xn. Крім вихідних сигналів Z1,…, Zm, комбінаційна схема формує сигнали Y1,…, Yk, які виконують переключення елементів пам’яті в різні стани S. Вихідні сигнали елементів пам’яті y1,…,yl надходять на комбінаційну схему. Найбільш відомим видом АП є синхронний автомат.

Функціонування АП визначається сигналами, що поступають від деякого незалежного джерела синхроімпульсів (СІ), які у свою чергу визначають такти роботи. АП діляться на синхронні і асинхронні. У синхронних АП є генератор синхроімпульсів, і дискретні моменти часу відстають один щодо одного на рівну величину t. У асинхронних АП генератор синхроімпульсів відсутній, а спрацьовування АП відбувається в дискретний час задається зовнішніми подіями (наприклад , кнопки на пульті управління). Для успішної побудови АП, нам необхідно розглянути деякі принципи їх побудови.

АП мають задану кількість внутрішніх станів. Залежно від алгоритму роботи пристрою, в певному порядку, переходить з одного стану в інший. Робота АП може задаватися за допомогою графа переходів-виходів або за допомогою таблиць переходів-виходів. Граф переходів-виходів є сукупністю вершин і дуг. У вершинах проставляється внутрішній стан автомата, а за допомогою дуг показують, при яких сигналах з якого в який стан переходить автомат. Табличний спосіб більш компактний, але менш наочний, виконує ті ж функції, що і граф переходів. Елементами, що запам'ятовують свою передісторію, є тригери.

І

снують

такі тригери:RS-,D-,T-,JK-,RS-тригери.

снують

такі тригери:RS-,D-,T-,JK-,RS-тригери.

Т

ригери

є послідовними елементарними автоматами,

здатними залишатися в одному з двох

стійких станів і після припинення дії

вхідного сигналу. Одне з них вважається

одиничним, а друге - нульове. В загальному

випадку тригер має два виходи - прямийУ

та інверсний

У.

Стан тригера прийнятий визначати по

значенню потенціалу на прямому виході.

Якщо, наприклад, на прямому виході є

потенціал, відповідний логічній «1», то

тригер знаходитися в одиничному стані

(при цьому потенціал на інверсному

виході відповідає логічному – «0»). В

осоружному випадку тригер знаходиться

в нульовому стані. В розробках АП2 ми

використовуватимемо тільки SR

тригер.

Таблиця внутрішніх станів представлена

нижче. Рівняння для SR

тригера:

ригери

є послідовними елементарними автоматами,

здатними залишатися в одному з двох

стійких станів і після припинення дії

вхідного сигналу. Одне з них вважається

одиничним, а друге - нульове. В загальному

випадку тригер має два виходи - прямийУ

та інверсний

У.

Стан тригера прийнятий визначати по

значенню потенціалу на прямому виході.

Якщо, наприклад, на прямому виході є

потенціал, відповідний логічній «1», то

тригер знаходитися в одиничному стані

(при цьому потенціал на інверсному

виході відповідає логічному – «0»). В

осоружному випадку тригер знаходиться

в нульовому стані. В розробках АП2 ми

використовуватимемо тільки SR

тригер.

Таблиця внутрішніх станів представлена

нижче. Рівняння для SR

тригера:

y(t+l)=(SR+Ry)t

Таблиця

2.1- Таблиця внутрішніх станів для SR

тригера

Таблиця

2.1- Таблиця внутрішніх станів для SR

тригера

-

S

R

Y(t)

Y(t+1)

0

0

0

0

0

1

0

1

0

1

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

1

Як і для розробки будь-яких пристроїв, в проектуванні АП існують певні етапи.

Етапи структурного синтезу автоматів з пам'яттю:

1.Словесний опис алгоритму роботи АП.

2. Складання графа переходів-виходів, таблиці переходів-виходів.

3. Скорочення числа внутрішніх станів (мінімізація).

4. Визначення кількості тригерів.

5. Кодування внутрішніх станів автомата.

6. Складання функціональної таблиці автомата.

7. Отримання ФАЛ описують вхідні сигнали, що подаються на входи тригерів, а також ФАЛ для вихідних сигналів.

8.

Побудова схеми автомата.

8.

Побудова схеми автомата.

Регістр зсуву і лічильник

Зсувний регістр представляє собою схему із зв’язаних між собою однобітових елементів пам’яті, розташованих у корпусі інтегральної схеми. Елементами пам’яті є тригери, з’єднані один з одним таким чином, що вихід одного є входом іншого. Входи виходи регістру організовані послідовно-паралельно. Використовуються для тимчасового зберігання даних, перетворення даних із паралельного в послідовний та навпаки. Кількість тригерів визначається розрядністю чисел, які зберігаються. Існують такі регістри зсуву:

регістри зсуву вправо;

регістри зсуву вліво;

реверсивні регістри зсуву (і вправо, і вліво).

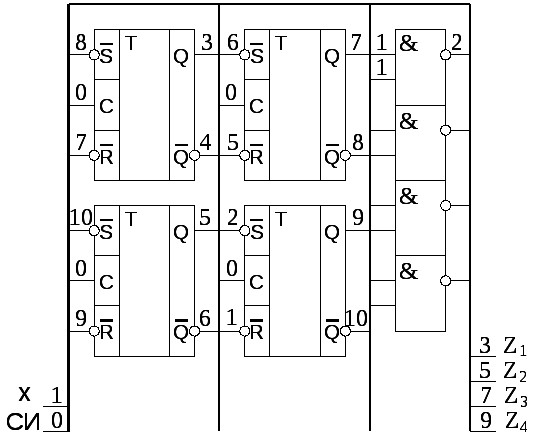

Розглянемо

чотирьохрозрядний регістр зсуву вліво.

Складаємо функціональну таблицю,

карти

Карно

,записуємо

рівняння. В цій схемі також будемо

використовувати RS

– тригери.

Розглянемо

чотирьохрозрядний регістр зсуву вліво.

Складаємо функціональну таблицю,

карти

Карно

,записуємо

рівняння. В цій схемі також будемо

використовувати RS

– тригери.

Таблиця 2.2-Функціональна таблиця

Рисунок 2.1-Карти Карно

Рисунок 2.2-Карти Карно

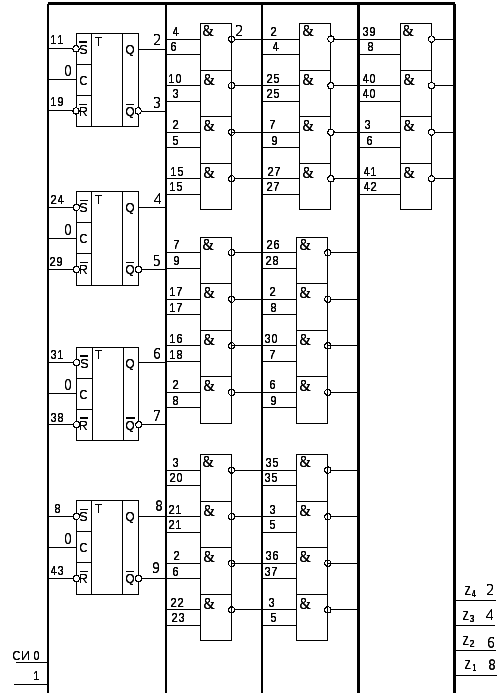

Рисунок 2.3- Схема чотирьохрозрядного регістра зсуву вліво

Лічильником імпульсів називають апарат з пам'яттю, призначений для підрахунку кількості імпульсів і перетворення їх в паралельний двійковий код.

Робота лічильника полягає в наступному. За допомогою вхідного сигналу в лічильник записуються числа, рівні кількості що поступили на вхід активних

сигналів.

Кожному числу відповідає певний

внутрішній стан лічильника. Між числами

і станами існує взаємна відповідність.

Робота лічильника полягає в послідовному

переході з одного стану в інший під

впливом вхідного сигналу. Лічильник

має певну кінцеву кількість внутрішніх

станів. Після приходу останнього

активного сигналу лічильник переходить

в початковий стан. По виду рахунку

лічильники діляться на:

сигналів.

Кожному числу відповідає певний

внутрішній стан лічильника. Між числами

і станами існує взаємна відповідність.

Робота лічильника полягає в послідовному

переході з одного стану в інший під

впливом вхідного сигналу. Лічильник

має певну кінцеву кількість внутрішніх

станів. Після приходу останнього

активного сигналу лічильник переходить

в початковий стан. По виду рахунку

лічильники діляться на:

лічильник прямого рахунку (що підсумовує);

лічильник зворотного рахунку (показує різницю);

реверсивний лічильник (підсумовує або віднімає);

лічильник по модулю рахунку;

двійково-десятковий лічильник;

лічильник, який працює в коді Грея.

На прикладі розглянемо роботу чотирьохрозрядного лічильника зворотнього рахунку по модулю 11. Модуль рахунку визначає число робочих станів лічильника.

Етапи проектування лічильника:

Виходячи із заданого модуля, визначаємо кількість тригерів:

n=]log2N[ - найближче ціле число.

Так як N=11, то n=4.Тобто нам потрібно взяти 4 тригера.

Д

ля

побудови будемо використовувати –RS

тригери;

ля

побудови будемо використовувати –RS

тригери; Складаємо функціональну таблицю для лічильника:

Так як у нас 11 робочих станів, то 5 – невикористані стани.

Таблиця 2.3-Функціональна таблиця

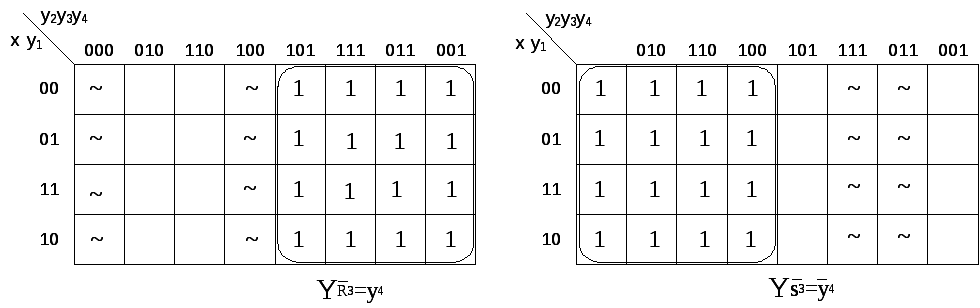

Рисунок

2.4-Карти Карно

Рисунок

2.4-Карти Карно

Рисунок 2.5-Карти Карно

Рисунок 2.6-Схема лічильника