3 Посібник Quartus

.pdf

160

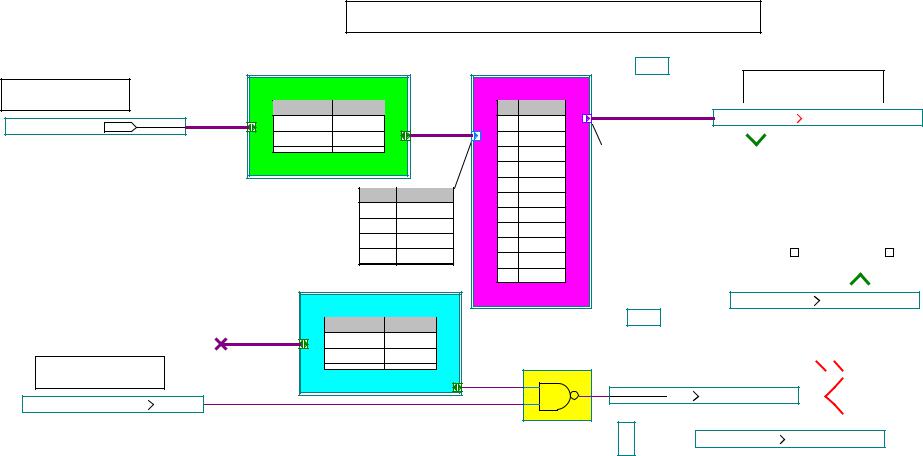

ПОРОГОВИЙ ЕЛЕМЕНТ 5 з 7 (проект на рівні блок-схеми)

DD1 MAX7000S - EPM7128SLC84-7

|

Дешифратор 7-сегм. коду |

|

|

|

Суматор (блок або символ) |

(макрофункція) |

|

VCC |

|

|

|

|

MAX_SW1 |

|

|

600sum |

|

|

|

74246 |

|

|

|

|

I/O |

Type |

|

|

I/O |

Type |

||

|

|

sw1[7..1] |

|

|

|||||

sw1[7..1] |

INPUT |

sw 1[7..1] |

INPUT |

|

dataa[3..0] |

B |

|

INPUT |

|

|

|

|

|||||||

|

VCC |

|

dataa[3..0] OUTPUT |

|

|

A |

|

INPUT |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

C |

|

INPUT |

|

|

|

inst |

|

|

|

D |

|

INPUT |

|

|

|

|

Block |

Bus |

OD OUTPUT |

|||

|

|

|

|

OC OUTPUT |

|||||

|

|

|

|

A |

|

dataa[0] |

OB OUTPUT |

||

|

|

|

|

B |

|

dataa[1] |

|||

|

|

|

|

|

OE OUTPUT |

||||

|

|

|

|

C |

|

dataa[2] |

|||

|

|

|

|

|

OF OUTPUT |

||||

|

|

|

|

D |

|

dataa[3] |

|||

161 |

|

|

|

|

OA OUTPUT |

||||

|

|

|

|

|

|

||||

|

|

Компаратор (мегафункція) |

OG OUTPUT |

||||||

|

|

|

|||||||

|

|

|

|

|

|

||||

|

|

|

cmp |

|

|

|

inst5 |

|

|

|

|

dataa[2..0] |

I/O |

|

Type |

|

|

|

|

|

|

dataa[2..0] INPUT |

|

Лог. елемент |

|||||

|

|

|

|

|

|||||

MAX_SW2 |

|

|

|

ageb |

OUTPUT |

|

|

(примітив) |

|

|

|

|

|

|

|

|

|

||

|

|

inst1 |

|

|

|

ageb |

|

NAND2 |

|

|

|

|

|

|

|

|

|

|

|

sw2[1] |

|

|

|

INPUT |

|

|

|

|

|

VCC |

inst2 |

|

|

|

|

|

yd[7] |

|

|

MAX_DIGIT |

|||

y d[7..0] |

|

|

|

|

|

|

y d[6..0] |

OUTPUT |

|

|

y d[7..0] |

||

Block |

Bus |

OA |

yd[0] |

OB |

yd[1] |

OC |

yd[2] |

OD |

yd[3] |

OE |

yd[4] |

OF |

yd[5] |

OG |

yd[6] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

a |

|

|

|

f |

|

|

|

|

|

b |

f |

|

|

|

|

b |

|

|

g |

|

|

|

g |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

e |

|

|

|

|

|

c |

e |

|

|

|

|

c |

|

|

|

|

|

|

dp |

|

|

|

|

|

dp |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

d |

|

|

|

|

d |

|

|

||

|

|

|

|

|

|

|

|

|

y o[7..0] |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

y o[7..0] |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|||

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

OUTPUT |

|

|

|

|

|

|

VD[1] |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

VD[2..16] |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

VD[2..16] |

|||||||||||||||||

|

VCC |

|

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок Д4

162

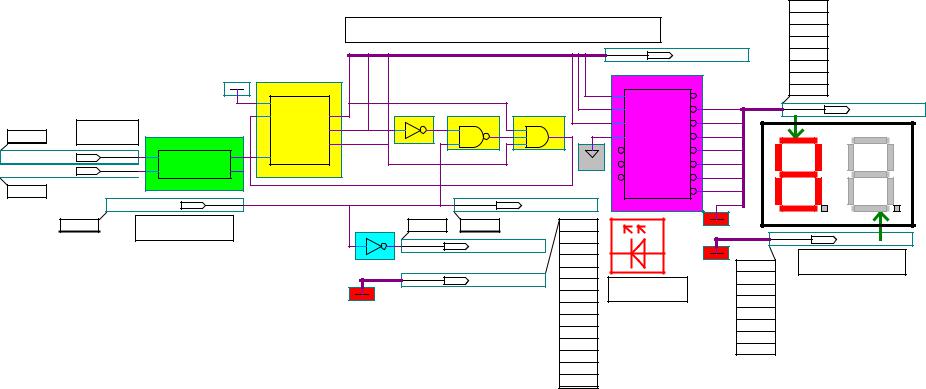

ЛІНІЯ ПЕРЕДАЧІ ДАНИХ DD1 MAX7000S - EPM7128SLC84-7

|

PIN_11 |

|

(проект на рівні блок-схеми) |

|

|

|

|

|

|

Лінія |

|

|

|

|

|

|

|

|||||

|

PIN_12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

PIN_15 |

|

MAX_SW1 |

|

|

|

|

mx |

|

|

|

зв'язку |

|

|

|

|

Фіксатор |

|

||||

|

PIN_16 |

|

|

|

|

|

I/O |

|

Type |

|

|

|

dmx |

|

|

|

|

|||||

|

PIN_17 |

|

|

|

|

|

sw1[7..1] |

|

|

|

|

|

G |

|

|

|

700f ixator |

|

|

|||

|

|

|

sw1[7..1] |

VCC |

|

|

sw 1[7..1] INPUT |

|

|

I/O |

Type |

CLRN |

|

|

|

|||||||

|

PIN_18 |

|

|

|

|

|

|

|

a[2..0] |

|

|

|

||||||||||

|

|

|

|

|

|

INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O |

Type |

|

|

PIN_20 |

|

|

|

|

|

a[2..0] |

|

|

a[2..0] |

INPUT |

|

|

|

a[2..0] |

INPUT |

|

|

|

|||

PIN_54 |

|

|

|

|

|

|

|

|

G |

OUTPUT |

|

|

|

G |

INPUT |

|

|

eq[6..0] |

INPUT |

|

||

|

|

|

|

9addr |

|

|

|

|

|

|

|

|

|

|

||||||||

pb1 |

|

|

INPUT |

pb1 |

|

Clk |

|

|

|

|

|

|

|

|

eq[6..0] |

OUTPUT |

eq[6..0] |

|

Clk |

INPUT |

|

|

|

|

|

|

|

|

inst2 |

|

|

|

|

|

|

a[2..0] |

INPUT |

|

|||||||

|

|

VCC |

pb2 |

I/O |

Type |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

pb2 |

|

|

INPUT |

|

|

|

Мультиплексор |

|

|

|

inst7 |

|

Clk |

|

CLRN |

INPUT |

|

|||||

|

|

|

pb1 |

INPUT |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

VCC |

|

a[2..0] |

|

|

|

|

|

|

|

|

Демультиплексор |

|

|

x[7..0] |

OUTPUT |

||||

PIN_55 |

|

PB1, 2 |

pb2 |

INPUT |

|

|

|

|

|

|

|

|

a[2..0] |

|||||||||

|

a[2..0] OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Clk |

OUTPUT |

VD[1] |

|

|

|

OUTPUT |

|

|

NOT |

y 2[0] |

|

|

inst5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

inst1 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

PIN_33 |

|

MAX_DIGIT |

|

Дешифратор 7seg |

y 2[1..0] |

|

0] |

|

|

||||||

|

|

|

|

|

inst12 |

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

dc7seg |

|

|

x[7.. |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

MAX_SW2 |

|

|

Формувач адреси |

|

y d[7..0] |

|

|

OUTPUT |

y d[7..0] |

I/O |

Type |

Bin8_BCD |

|

|

PIN_34 |

|||||||

|

|

|

|

|

CLRN |

PIN_58 |

|

|

|

|

|

|

|

|

||||||||

sw2[8] |

|

|

|

INPUT |

|

|

|

|

|

|

|

|

|

x[3..0] INPUT |

|

|

|

|

PIN_35 |

|||

|

|

|

|

PIN_60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

VCC |

|

|

|

|

a |

|

|

a |

|

|

z[7..0] OUTPUT |

y 1[3..0] |

I/O |

Type |

|

PIN_36 |

||

|

|

|

|

|

|

PIN_61 |

|

|

|

|

|

|

|

|

||||||||

PIN_31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x[7..0] |

INPUT |

|

PIN_37 |

||

|

|

|

|

|

|

PIN_63 |

|

|

f |

|

b |

f |

|

b |

|

inst9 |

|

|

y0[3..0] |

OUTPUT |

PIN_39 |

|

|

|

|

|

|

|

PIN_64 |

|

|

g |

g |

|

|

|

y1[3..0] |

OUTPUT |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_40 |

||||||

|

|

|

|

|

|

PIN_65 |

|

|

|

|

|

|

|

|

|

|

|

y 0[3..0] |

y2[1..0] |

OUTPUT |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

dc7seg |

|

PIN_41 |

|||||

|

|

|

|

|

|

PIN_67 |

D1 |

|

e |

c |

e |

|

c |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

I/O |

Type |

|

|

|

|

PIN_44 |

|||||||

|

|

|

|

|

|

PIN_68 |

|

|

|

inst |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_45 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x[3..0] INPUT |

Перетворювач двійкового |

|||||

|

|

|

|

|

|

|

Z100 |

|

|

d |

dp |

|

d |

dp |

|

PIN_46 |

||||||

|

|

|

|

|

|

|

|

|

|

|

z[7..0] OUTPUT |

коду у двійково-де сятковий |

||||||||||

|

|

|

|

|

|

PIN_69 |

|

y o[7..0] |

|

|

OUTPUT |

y o[7..0] |

|

|

PIN_48 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

Block |

Bus |

|

|

PIN_49 |

|||||||

|

|

|

|

|

|

PIN_70 |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

inst8 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

Z10 |

|

Z1 |

|

|

|

x[3..0] y1[3..0] |

|

|

PIN_50 |

||||

|

|

|

|

|

|

PIN_73 |

|

|

|

|

|

|

Дешифратор 7seg |

|

|

|||||||

|

|

|

|

|

|

PIN_74 |

|

|

|

|

Block |

Bus |

|

|

Block |

Bus |

|

|

PIN_51 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|||||||

|

|

|

|

|

|

PIN_76 |

|

|

|

|

z[7..0] yd[7..0] |

|

|

|

|

x[3..0] y0[3..0] |

|

|

PIN_52 |

|||

|

|

|

|

|

|

PIN_75 |

|

|

|

|

|

Block |

Bus |

|

|

|

OUTPUT |

|

|

VD[2..16] |

|

|

|

|

|

|

|

|

PIN_77 |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

PIN_79 |

|

|

|

|

|

z[7..0] yo[7..0] |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок Д5

163

ГЕНЕРАТОР КОДОВИХ ПОСЛІДОВНОСТЕЙ

(проект на основі регістра зсуву) |

|

|

|

|

|

|

Block |

Bus |

|

|

DD1 MAX7000S - EPM7128SLC84-7 |

|

VD[8..1] |

VD[8..1] |

|

|

|

|

|

|

|

|

|

PIN_11 |

74295 |

PIN_12 |

|

|

|

|

|

MAX_SW1 |

|

|

|

|

|

||||||

|

PIN_15 |

|

|

|

SER |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

sw1[3..1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

sw 1[1] |

|

|

|||

|

|

sw1[3..1] |

|

|

INPUT |

|

D0 |

Q0 |

||||||||

|

|

|

|

|

|

|

|

|

VCC |

|

sw 1[2] |

|

D1 |

Q1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

PB1, 2 |

|

|

|

|

|

|

|

|

|||||

PIN_54 |

|

|

|

|

nandltch |

sw 1[3] |

|

D2 |

Q2 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

pb1 |

INPUT |

RN |

Q |

|

VCC |

pb2 |

|

|

|

|

INPUT |

|

|

|

|

SN |

|

QN |

|

|

|

|

|

|

|

CLK |

|||

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

inst |

|

|

|

|

|

|

|

|

|

|

|

LD/SHN 1 |

||

|

PIN_55 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

sw2[1] |

|

|

|

|

|

INPUT |

|

4 |

|

SHIFT REG. |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

PIN_22

MAX_SW2

MAX_SW2

NOT |

NAND2 |

3 |

1 |

|

Q0

Q1

Q2

0  1

1  3

3

4  6

6  7

7

D1  D2

D2  D3

D3

D5  D6

D6  D7

D7

NAND2

5

800dc

|

|

|

I/O |

Type |

|

|

|

|

|||||

|

|

|

Q[2..0] |

INPUT |

|

|

|

|

|

VD[8..1] |

OUTPUT |

|

|

|

|

|||||

Q[2..0] |

|

|

VD[16..9] |

OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

inst1 |

|

|

|

|

|

|

|

|

|

||

VD[8..1]

OUTPUT

VD[16..9]

OUTPUT

y o[7..0]

OUTPUT

VCC

|

|

|

|

|

|

|

|

|

|

|

Block |

|

Bus |

|

|

|

|

|

a |

|

|

||

5 |

|

|

|

Q[3] |

|

|

|

|

VD[16..9] |

VD[16..9] |

|

|

f |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||

2 |

|

|

|

|

|

|

|

|

GN D |

|

|

|

|

|

|

|

g |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q[3..0] |

dc7seg |

|

|

|

|

|

e |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

I/O |

Type |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

Block |

|

Bus |

|

|

|

|

x[3..0] |

INPUT |

|

|

|

|

|

|

|

|

d |

|

|

||

|

|

x[3..0] |

Q[3..0] |

|

|

|

|

z[7..0] |

OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

y d[7..0] |

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

inst2 |

|

|

|

|

|

OUTPUT |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Block Bus

z[7..0] yd[7..0]

Рисунок Д6

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_33 |

|

|

|

|

|

|

|

PIN_34 |

|

|

|

|

|

|

|

PIN_35 |

|

|

|

VD[8..1] |

|

|

|

PIN_36 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

PIN_37 |

|

|

|

VD[16..9] |

|

|

PIN_39 |

||

|

|

|

|

PIN_40 |

|||

|

|

|

|

|

|

||

|

|

y o[7..0] |

|

|

|

PIN_41 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_44 |

|

|

|

a |

|

|

|

PIN_45 |

|

|

|

|

|

|

|

PIN_46 |

|

b |

f |

|

b |

|

|

PIN_48 |

|

g |

|

|

PIN_49 |

||||

|

|

|

|

|

|||

|

|

|

|

|

|

PIN_50 |

|

c |

e |

|

c |

|

|

PIN_51 |

|

|

|

|

PIN_52 |

||||

|

|

|

|

|

|

||

dp |

|

d |

dp |

|

|

|

|

|

|

PIN_69 |

|

||||

|

|

|

|

|

PIN_70 |

|

|

|

y d[7..0] |

|

|

PIN_73 |

|

||

|

|

|

PIN_74 |

|

|||

|

|

PIN_58 |

|

|

|

||

|

|

|

|

PIN_76 |

|

||

|

|

PIN_60 |

|

|

PIN_75 |

|

|

|

|

PIN_61 |

|

|

PIN_77 |

|

|

|

|

PIN_63 |

|

|

PIN_79 |

|

|

|

|

PIN_64 |

|

|

|

|

|

|

|

PIN_65 |

|

|

|

|

|

|

|

PIN_67 |

|

|

|

|

|

|

|

PIN_68 |

|

|

|

|

|

164

|

|

|

|

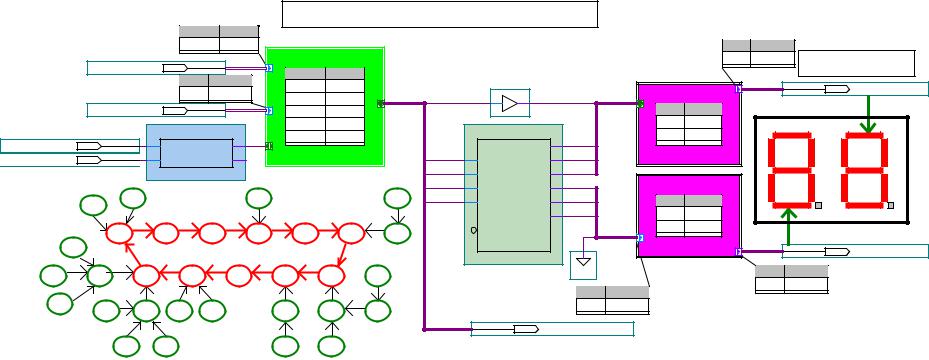

ПРОГРАМОВАНИЙ ЛІЧИЛЬНИК (М=5, 7) |

PIN_58 |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

DD1 MAX7000S - EPM7128SLC84-7 |

|

|

|

|

PIN_60 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

PIN_61 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT |

Q[2..0] |

|

|

PIN_63 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_64 |

|

|

|

|

|||

|

|

|

|

|

|

Q0 Q1 |

Q2 |

|

|

|

|

|

|

|

|

|

|

PIN_65 |

|

|

|

|

|

|

|

VCC |

|

74293 |

|

|

|

|

Q0 |

|

|

74247 |

|

|

PIN_67 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_68 |

|

|

|

|

||||

|

|

|

5 |

|

|

|

|

|

|

|

Q1 |

|

A |

|

y d0 |

y d[7..0] |

|

|

|

|

||

|

|

|

|

|

CLRA |

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

B |

OA |

|

|

y d[7..0] |

|

|||||

|

|

|

|

|

CLRB |

QB |

NOT |

NAND2 |

AND3 |

|

Q2 |

|

y d1 |

|

|

|

|

|

||||

|

|

|

|

|

|

|

C |

OB |

|

|

|

|

|

|

||||||||

|

PB1, 2 |

|

|

|

|

|

|

y d2 |

|

a |

|

|

a |

|

||||||||

|

|

|

|

|

QC |

|

|

|

|

|

|

|

|

|

|

|

||||||

PIN_54 |

|

|

|

|

4 |

|

|

|

|

|

|

D |

OC |

|

|

|

|

|||||

|

nandltch |

|

|

QD |

|

2 |

1 |

|

|

|

y d3 |

|

|

|

|

|

|

|||||

pb1 |

INPUT |

|

|

CLKB |

|

|

|

|

|

|

OD |

y d4 |

f |

|

b |

f |

|

b |

||||

RN |

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

VCC |

|

|

|

|

|

|

RM |

GND |

|

|

OE |

g |

g |

|||||||||

pb2 |

INPUT |

SN |

QN |

3 |

COUNTER |

|

|

|

|

|

|

|

y d5 |

|

|

|

|

|||||

VCC |

|

|

|

|

|

|

|

|

OF |

|

|

|

|

|

|

|||||||

|

|

inst |

|

|

|

|

|

|

|

|

|

|

|

|

y d6 |

|

|

|

|

|

|

|

PIN_55 |

|

|

|

|

|

|

|

|

|

|

|

|

|

OG |

e |

|

c |

e |

|

c |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

y d7 |

|

|

|||||||

|

|

INPUT |

|

|

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|||||||

|

sw1[1] |

|

|

|

|

|

|

VD[1] |

|

|

32 |

BCD TO 7SEG |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

d |

dp |

|

d |

dp |

|||||

|

PIN_11 |

MAX_SW1 |

|

|

|

|

PIN_34 |

PIN_33 |

|

PIN_35 |

|

|

|

VCC |

|

|

||||||

|

|

|

|

|

|

|

|

|

y o[7..0] |

|

|

|

|

|

||||||||

|

|

|

|

NOT |

|

|

|

|

PIN_36 |

|

|

|

|

|

|

y o[7..0] |

|

|||||

|

|

|

|

|

|

|

OUTPUT |

VD[2] |

|

|

|

|

|

OUTPUT |

|

|

||||||

|

|

|

|

|

|

|

|

|

PIN_37 |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

inst2 |

|

|

|

|

|

|

|

VCC |

|

MAX_DIGIT |

|

|||||

|

|

|

|

|

|

|

|

|

|

PIN_39 |

|

|

|

PIN_69 |

|

|||||||

|

|

|

|

|

|

VD[3..16] |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

OUTPUT |

VD[3..16] |

|

PIN_40 |

|

|

|

|

PIN_70 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

PIN_41 |

D1...D16 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

VCC |

|

|

|

|

|

PIN_73 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

PIN_44 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_45 |

|

|

|

|

PIN_74 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_76 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

PIN_46 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_75 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

PIN_48 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_77 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

PIN_49 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_79 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

PIN_50 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

PIN_51 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN_52 |

|

|

|

|

|

|

|

|

|

|

|

Рисунок Д7

165

ПОДІЛЬНИК ЧАСТОТИ (М=11) |

|||||||

(проект на основі JK-тригерів) |

|

|

|

|

|||

|

|

|

DD1 MAX7000S - EPM7128SLC84-7 |

||||

|

|

|

|

|

|

|

|

|

Block |

Conduit |

|

Block |

Conduit |

||

|

|

|

|

||||

|

CLRN |

sw 2[1] |

|

PRN[4..0] |

sw 1[5..1] |

|

|

|

|

|

|

|

|

|

|

VCC

|

|

MAX_SW1 |

|

|

|

1000pod11 |

|

|

|

OUTPUT |

|

|

VD[2..16] |

|

|

Block |

Bus |

|

|

|

|

|

||

|

|

|

<<sw1[5..1]>> |

|

|

|

|

|

|

|

|

z[7..0] yo[7..0] |

MAX_DIGIT |

|

||||||||||

|

|

VCC |

|

|

Qout |

|

OUTPUT |

|

|

|

|

|

|

|||||||||||

|

sw1[5..1] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

INPUT |

|

|

I/O |

Type |

|

|

|

|

VD[1] |

|

Дешифратор 7seg |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

yo[7..0] OUTPUT |

|

|

|

|

||||||

|

|

MAX_SW2 |

|

|

|

PRN[4..0] INPUT |

Q[4..0] |

Q[0] |

|

WIRE |

x[0] |

|

x[3..0] |

dc7seg |

|

|

|

|

y o[7..0] |

|||||

|

|

|

<<sw2[1]>> |

|

C |

INPUT |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

INPUT |

|

|

|

|

|

|

|

|

I/O |

Type |

|

|

|

|

|

|

||||||

|

sw2[1] |

|

|

|

|

CLRN |

INPUT |

|

|

|

inst11 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

nandltch |

|

Q[4..0] |

OUTPUT |

|

|

|

74185 |

|

|

|

x[3..0] INPUT |

a |

|

|

|

a |

|

||

|

|

|

VCC |

|

C |

Qout |

OUTPUT |

|

|

|

Y1 |

x[1] |

|

z[7..0] OUTPUT |

|

|

|

|

|

|

||||

pb1 |

|

|

|

RN |

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

INPUT |

|

|

|

|

|

Q[1] |

|

|

x[2] |

|

|

|

f |

|

b |

f |

|

b |

||||

pb2 |

|

|

VCC |

|

SN |

QN |

|

inst2 |

|

|

A |

|

Y2 |

|

inst9 |

|

g |

g |

||||||

|

|

INPUT |

|

|

|

|

Q[2] |

|

x[3] |

|

|

|

|

|

|

|||||||||

PB1, 2 |

|

inst |

|

Блок подільника частоти |

Q[3] |

B |

|

Y3 |

y [0] |

|

dc7seg |

|

e |

|

c |

e |

|

c |

||||||

17 |

|

|

23 |

|

|

13 |

C |

|

Y4 |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

Q[4] |

|

y [1] |

|

|

|

|

|

||||||||||

|

|

16 |

|

|

|

|

D |

|

Y5 |

|

I/O |

Type |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

y [2] |

|

|

d |

dp |

|

d |

dp |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y6 |

|

|

x[3..0] INPUT |

|

|

|||||

|

|

|

00 |

|

07 |

22 |

06 |

29 |

12 |

28 |

|

|

|

|

y[3] |

y[3..0] |

z[7..0] OUTPUT |

|

Z10 |

|

|

Z1 |

|

|

|

09 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

inst10 BINARY-BCD |

|

|

inst8 |

|

yd[7..0] OUTPUT |

|

|

|

y d[7..0] |

|||||

24 |

|

08 |

|

01 |

10 |

27 |

|

04 |

21 |

15 |

|

|

|

Дешифратор 7seg |

|

|

|

|

|

|

||||

|

|

|

Перетворювач двійкового |

GND |

|

Block |

Bus |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

коду у двійково-десятковий |

Block |

Bus |

|

|

z[7..0] yd[7..0] |

|

|

|

|

||||

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

03 |

02 |

11 |

26 |

|

20 |

14 |

30 |

|

|

|

|

x[3..0] y[3..0] |

|

|

|

|

|

|

|

|

||||

|

|

|

Q[4..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Q[4..0] |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|

|

|||

18 |

19 |

05 |

31 |

Примітка: Зі входів PRN[ ] стан поза основним циклом слід завантажувати в інверсному коді.

Рисунок Д8

166

ПОДІЛЬНИК ЧАСТОТИ (М=11) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

(проект на основі JK-тригерів) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

DD2 FLEX10K - EPF10K70RC240-4 |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

Block |

Conduit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PRN[4..0] sw [5..1] |

1000pod11 |

|

|

|

|

|

|

|

|

|

Block |

Bus |

|

|

|

|

|

||

|

sw[5..1] |

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

z[7..0] yo[7..0] |

FLEX_DIGIT |

||||||||

|

|

|

|

|

INPUT |

|

I/O |

Type |

|

|

|

|

|

|

|

Дешифратор 7seg |

|

|

|

|

|

|

||

|

|

|

|

|

Block |

Conduit |

|

|

|

|

|

|

|

y o[7..0] |

|

|

|

|

|

|||||

|

FLEX_SWITCH |

|

PRN[4..0] INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

y o[7..0] |

|||||||

|

|

CLRN sw 8 |

Q[4..0] |

Q[0] |

|

WIRE |

x[0] |

|

x[3..0] |

dc7seg |

|

OUTPUT |

|

|

|

|||||||||

|

|

CLRN |

INPUT |

|

|

|

|

|

|

|

|

|

||||||||||||

|

sw8 |

|

|

|

INPUT |

|

|

|

|

|

|

|

|

I/O |

Type |

|

|

|

|

|

|

|||

|

|

|

|

|

C |

INPUT |

|

|

|

inst11 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

FLEX_PB1 |

|

|

|

nandltch |

|

Q[4..0] |

OUTPUT |

|

|

|

74185 |

|

|

|

x[3..0] INPUT |

a |

|

|

|

a |

|

|||

VCC |

|

|

C |

Qout |

OUTPUT |

|

|

|

Y1 |

x[1] |

|

z[7..0] OUTPUT |

|

|

|

|

|

|

||||||

pb1 |

|

|

RN |

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

INPUT |

|

|

|

|

|

|

Q[1] |

|

|

x[2] |

|

|

|

f |

|

b |

f |

|

b |

||||

pb2 |

|

VCC |

|

SN |

|

QN |

inst4 |

|

|

A |

|

Y2 |

|

inst9 |

|

g |

g |

|||||||

|

INPUT |

|

|

|

|

Q[2] |

|

x[3] |

|

|

|

|

|

|

||||||||||

FLEX_PB2 |

|

inst |

|

|

|

Блок подільника частоти |

Q[3] |

B |

|

Y3 |

y [0] |

|

dc7seg |

|

e |

|

c |

e |

|

c |

||||

|

|

17 |

|

|

|

23 |

|

|

13 |

Q[4] |

C |

|

Y4 |

y [1] |

|

|

|

|

||||||

|

16 |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

D |

|

Y5 |

|

I/O |

Type |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

y [2] |

|

|

d |

dp |

|

d |

dp |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y6 |

|

|

x[3..0] INPUT |

|

|

|||||

|

|

00 |

07 |

|

22 |

06 |

29 |

12 |

28 |

|

|

|

|

y [3] |

y [3..0] |

z[7..0] OUTPUT |

|

Z10 |

|

|

Z1 |

|

||

09 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

inst10 BINARY-BCD |

|

|

inst8 |

|

y d[7..0] OUTPUT |

|

|

|

y d[7..0] |

||||

24 |

08 |

|

01 |

|

10 |

|

27 |

04 |

21 |

15 |

|

|

|

Дешифратор 7seg |

|

|

|

|

|

|

||||

|

|

|

Перетворювач двійкового |

GND |

|

Block |

Bus |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

коду у двійково-десятковий |

Block |

Bus |

|

|

z[7..0] yd[7..0] |

|

|

|

|

||||

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

03 |

02 |

11 |

26 |

|

20 |

14 |

30 |

|

|

|

|

x[3..0] y[3..0] |

|

|

|

|

|

|

|

|

||||

|

|

Q[4..0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

OUTPUT |

|

Q[4..0] |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

18 |

19 |

05 |

31 |

Примітка: Зі входів PRN[ ] стан поза основним циклом слід завантажувати в інверсному коді.

Рисунок Д9

Навчальне видання

Віктор Леонідович Кофанов Олександр Володимирович Осадчук Дмитро Володимирович Гаврілов

ПРАКТИКУМ З ЦИФРОВИХ ПРИСТРОЇВ

НА ОСНОВІ САПР QUARTUS II

Навчальний посібник

Оригінал-макет підготовлено авторами

Редактор

Навчально-методичний відділ ВНТУ Свідоцтво Держкомінформу України серія ДК № 746 від 25.12.2001

21021, м. Вінниця, Хмельницьке шосе, 95, ВНТУ

Підписано до друку |

Гарнітура Peterburg |

||

Формат 29,7х42 |

1 |

4 |

Папір офсетний |

|

|

|

|

Друк різографічний |

Ум. друк. арк. |

||

Тираж прим. |

|

|

|

Зам. № |

|

|

|

Віддруковано в комп’ютерному інформаційно-видавничому центрі Вінницького національного технічного університету

Свідоцтво Держкомінформу України серія ДК № 746 від 25.12.2001

21021, м. Вінниця, Хмельницьке шосе, 95, ВНТУ