цифрова схемотехніка

.pdf

позначення DD11, DD12.

4.6 Проектування модуля керуючого блока МКБ1

Проектування модуля МКБ1 на основі автомата Мура з пам’яттю на JK-тригерах виконується в такій послідовності.

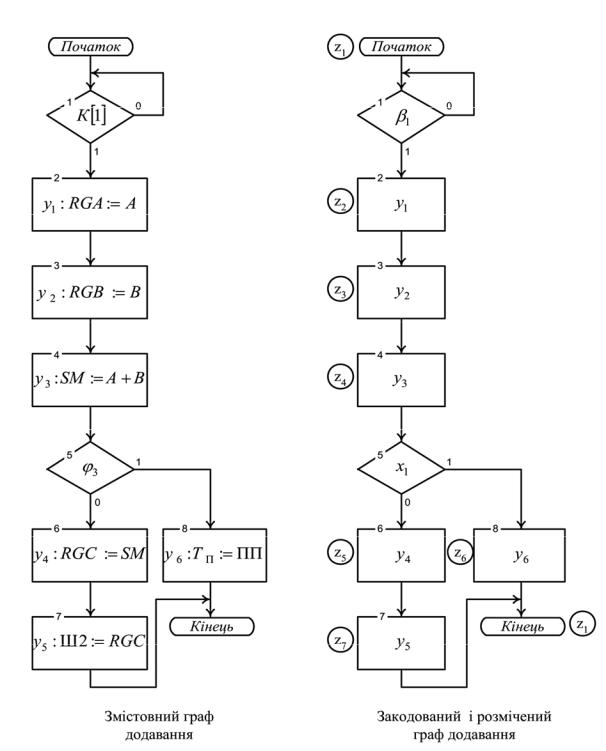

1. Розмічається закодований граф мікропрограми додавання. Визначається максимальна кількість станів автомата Мура, що дорівнює L=7. Для реалізації такого числа станів необхідно використати

n= ]log27[ = 3 тригери.

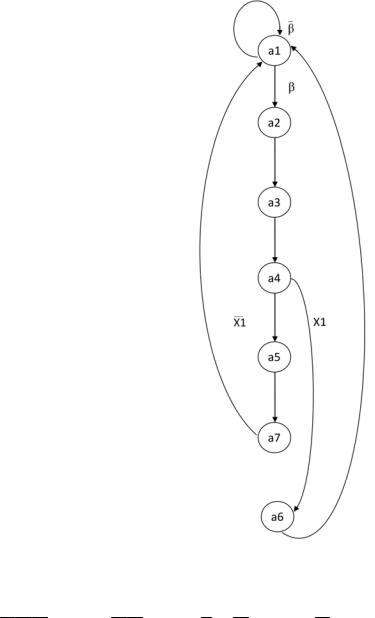

2.На основі розміченого графа мікропрограми будується граф автомата Мура (рис. 4.1), який інтерпретує мікропрограму додавання.

Рис. 4.1. Граф автомата Мура для мікропрограми додавання

3. Стани автомата Мура кодуються значеннями виходів JK-тригерів: z1 =Q1Q2 Q3 , z2 =Q1Q2 Q3 z2, z3 =Q1Q2 Q3 ... , z7 =Q1Q2Q3 .

30

4. На основі графа автомата Мура записується його структурна таблиця переходів (табл. 4.1).

Таблиця 4.1 – Структурна таблиця переходів автомата Мура

|

Zi |

|

K(zi) |

Zj |

|

K(zj) |

{xi } |

|

{y j } |

|

JK |

|

|||||

|

|

|

|

K |

|

J |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Z1 |

|

000 |

Z1 |

|

000 |

|

|

|

1 |

|

- |

- |

|

- |

|

|

|

|

|

|

β |

|

|

|

||||||||||

|

|

|

|

Z2 |

|

001 |

|

|

β1 |

|

y1 |

- |

|

J1 |

|

||

|

Z2 |

|

001 |

Z3 |

|

010 |

1 |

|

|

y2 |

K1 |

|

J2 |

|

|||

|

Z3 |

|

010 |

Z4 |

|

011 |

1 |

|

|

y3 |

- |

|

J1 |

|

|||

|

Z4 |

|

011 |

Z5 |

|

100 |

|

|

|

|

|

|

y4 |

K2, K1 |

|

J3 |

|

|

|

|

|

|

x1 |

|

|

|

|||||||||

|

|

|

|

Z6 |

|

101 |

|

|

x1 |

|

y6 |

K2 |

|

J3 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Z5 |

|

100 |

Z7 |

|

110 |

1 |

|

|

y5 |

- |

|

J2 |

|

|||

|

Z6 |

|

101 |

Z1 |

|

000 |

1 |

|

|

- |

K3, K1 |

|

- |

|

|||

|

Z7 |

|

110 |

Z1 |

|

000 |

1 |

|

|

- |

K3, K2 |

|

- |

|

|||

|

5. На підставі даних табл. 4.1 записуються системи логічних рівнянь |

||||||||||||||||

для функцій збудження входів JK-тригерів і виходів: |

|

|

|

|

|||||||||||||

|

• для функцій збудження входів: |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

J1 = z1 β1 |

z3; J2 = z2 |

z5 ; J3= z4 ; |

|

|

|

|

|

|

|

|

|

|

|

|||

|

K1 = z2 |

z4 |

z6 ; K1 = z4 z7; K1 = z6 |

z7. |

|

|

|

|

|||||||||

• для вихідних керуючих сигналів:

y1 = z2 ; y2= z3 ; y3 = z4 ; y4= z5 ; y5= z7 ; y6= z6.

6. Будується принципова схема модуля керування МКБ1 (додаток Е). Відповідність між входами керування мікросхем модуля МОБ1 (дода-

ток Д) і сигналами мікрооперацій наведено в табл. 4.2.

Таблиця 4.2 – Таблиця відповідності між керуючими входами мікросхем і сигналами мікрооперацій

Входи |

LA |

LB |

ЛИ |

LC |

|

Tп(J4) |

|

|

|

|

|

|

EZ |

||||||||||||

Сигнали мік- |

y1 |

y2 |

y3 |

y4 |

|

y6 |

|

|

|

|

|

|

|

|

|

y5 |

|

||||||||

рооперацій |

|

|

|

|

|

|

|

|

|

|

|

|

Для побудови принципової схеми модуля МКБ1 |

використані такі мі- |

|||||||||||

кросхеми:

•DD13, DD14 – дві мікросхеми типу ТВ6, кожна з яких містить по два JK-тригери (пам’ять автомата Мура);

•DD 15 – дешифратор типу ИД7. Використовується для виділення станів автомата;

•DD16, DD17.1 – дві мікросхеми типу ЛН1, кожна з яких містить шість інверторів;

31

• DD 18 – мікросхему типу ЛИ1, яка містить чотири кон’юнктори; •DD 19, DD20 – дві мікросхеми типу ЛЛ1.

В додатку Ж наведено лист переліку мікросхем АЛП.

4.7 Моделювання пристрою додавання

Моделювання проводилося в програмному середовищі National Instruments Multisim 11.0. Multisim. Даний програмний продукт є одним з найбільш відомих засобів моделювання цифрових і аналогових схем і є 11ою версією всім відомої програми Electronic WorkBench.

На додаток до багатьох особливостей, які зробили Multisim фаворитом серед професійних користувачів, Multisim містить також ряд функцій, корисних для навчання. Він містить інструменти, що надаються Multisim переваги: програмний інтерфейс, функції підтримки роботи з групою студентів, а також деякі аспекти, функції та режими роботи з метою навчання.

Використовуючи інструменти Multisim, промодельовано роботу ари- фметико-логічного пристрою операції додавання. Результати моделювання наведені у вигляді часових діаграм на рис 4.2 і 4.3, які підтверджують правильність роботи спроектованої схеми.

Рисунок 4.3 – Часова діаграма арифметико-логічного пристрою додавання до виконання умови парності молодшого байта

32

Рисунок 4.3 – Часова діаграма арифметико-логічного пристрою додавання при виконанні умови парності молодшого байта

4.8 Характеристики АЛП

Згідно з довідковими даними мікросхеми ТТЛШ серії КР1533, які використано для побудови АЛП, споживають таку потужність:

РИР35 = 122 мВт; РИР12 = 100 мВт;

РИМ6 (тип F, серія КР1531) = 180 мВт;

РИД7 |

= 50 мВт; |

РТВ6 = 22,5 мВт; |

|

РЛП5 |

= 30 мВт; |

РЛН1 |

= 13 мВт; |

РЛЛ1 |

= 22,5 мВ т; |

РЛИ1 |

= 16 мВт. |

Потужність, яку споживає пристрій АЛП1, розраховується додаван-

ням потужностей всіх мікросхем: Р АЛП1=2Р ИР35 +Р ИР12 +2Р ИМ6 +Р ИД7+ +2Р

ТВ6 +Р ЛП5 +2Р ЛН1 +4Р ЛЛ1+ +5Р ЛИ1 = (2·122+100+2·180+50+ +2·22,5+30+2·13+4·22,5+5·16)10–3=1,125 Вт.

Мікросхема КР1531ИМ6 реалізовує додавання двох чотирирозрядних операндів за t SM .1 =15 нс. При додаванні восьмирозрядних операндів тривалість мікрооперацій подвоюється, тобто t SM .2 = 2· t SM .1 = 30нс. Враховуючи затримки сигналів, що подаються на входи суматора, рекомендується обирати тривалість машинного такту ТС= 2 ·t SM .2 = 60 нс. При цьому швид-

33

кодія АЛП1, виражена кількістю операцій додавання за секунду типу «ре- гістр-регістр», становитиме F = 1/ ТС  16·106 оп/с (операцій в секунду).

16·106 оп/с (операцій в секунду).

5 ОРГАНІЗАЦІЙНІ ПИТАННЯ ТА ЕТАПИ ПРОЕКТУВАННЯ

1.За 4 тижні до захисту керівник проекту складає і подає до деканату графік захисту з визначенням місця, часу та прізвище студентів.

2.Деканат затверджує складений кафедрою графік захисту курсового проекту.

3.Поетапний графік виконання курсового проекту ведеться викладачем в журналі.

4.Не самостійно виконаний, не завершений курсовий проект відмічається у відомості як "не допущено" і повертається на доопрацювання.

Далі підписуються графи „Керівник” та „Нормоконтроль” для курсового проекту. Для захисту курсових проектів кафедрою призначається комісія у складі не менше як двох викладачів.

До захисту допускаються курсові проекти, що виконані в повному обсязі згідно із затвердженим індивідуальним завданням, перевірені керівником і підписані ним на титульному аркуші із зазначенням дати. Рекомендується підписувати КП таким чином: „До захисту”, „Дата”, „Підпис керівника”. КП, які не підписані до захисту керівником, на захист не виносяться.

Отже, основними етапами проектування є:

8.1Узгодження технічного завдання з керівником проекту.

8.2Вивчення науково-технічної літератури по темі курсового проек-

ту.

8.3Розробка алгоритму заданої операції і функціональної схеми

АЛП.

8.4Написання мікропрограми операції і розробка принципової схеми операційного блока.

8.5Структурний синтез керуючого автомата і побудова його принципової схеми.

8.6Виконання розрахунків технічних характеристик АЛП (вартості, швидкодії, споживаної потужності, середньої виробітки на відмову).

8.7Оформлення текстових і графічних матеріалів проекту.

8.8Захист курсового проекту.

Код кафедри електроніки ............................................... |

08-05 |

Рекомендована література

34

1.Угрюмов Е. П. Цифровая схемотехника.- СПб: БХВ, 2000.

2.Азаров О. Д., Бойко В. В., Обертюх М. Р. Комп’ютерна електроніка. Елементи цифрових схем. – Вінниця: ВДТУ, 2003.

3.Гикавий В. А. Цифрова і аналогова схемотехніка. Лабораторний практикум. – Вінниця: ВДТУ, 2001.

4.Бабич Н. П. Основы цифровой схемотехники. – М.: «Додеко XX1», 2007.

5.Рябенький В. М., Жуйков В. Я., Гулий В. Д. Цифрова схемотехніка. –

К.: «Новий світ – 2000», 2009.

6.Бабич Н. П., Жуков І. А., Яременко К. П. та ін. Комп’ютерна схемотехніка. Курсове проектування . Навчально-методичний посібник. –

К.: НАУ, 2004.

7.Карлащук В. И. Электронная лаборатория IBM PC. Программа

Electronics Workbench и её применение. – М.: Додэка, 2001.

8.Бойко В. І., Гуржій В. Я., Зорі К. А., Співак В. М., Жуйков В. Я., Терещенко Т. О., Петергеря Ю. С. Основи технічної електроніки в 2-х книгах. Схемотехніка, книга 2. – К.: «Вища школа», 2007.

35

Додаток А

Міністерство освіти і науки, молоді та спорту України Вінницький національний технічний університет Інститут радіотехніки, зв’язку та приладобудування

Факультет МБЕП Кафедра електроніки

Завдання

На курсове проектування з дисципліни «Цифрова схемотехніка»

Студенту гр. ЕП_____________________________________

Пропонується:

Розробити і розрахувати спеціалізований арифметико-логічний пристрій для операції додавання.

Дані для розрахунку:

тип арифметичної операції – додавання двійкових чисел;

початковий код подання операндів – прямий;

розрядність операндів – 16 біт;

код виконання операції у суматорі – обернений;

тип керуючого блока – автомат Мура з пам’яттю на JK-тригерах;

ознака результату – парність молодшого байта;

логічна операція – NOR.

Термін подання КР до захисту |

___________________ |

Керівник |

______________ |

Студент гр. ЕП- |

________________________. |

«___» ____________ 20__р |

|

|

36 |

Додаток Б

(обов’язковий)

Міністерство освіти і науки, молоді та спорту України Вінницький національний технічний університет Інститут радіотехніки, зв’язку та приладобудування

Факультет медико-біологічного та електронного приладобудування

ЗАТВЕРДЖЕНО Зав каф. електроніки, проф., д.т.н.

Білинський Й. Й.

„ ____” ________20__ р.

ІНДИВІДУАЛЬНЕ ЗАВДАННЯ

на курсовий проект з дисципліни

„ ЦИФРОВА СХЕМОТЕХНІКА ”

студенту ______________ факультету __________ групи ___________

Розробити і розрахувати спеціалізований арифметико – логічний

Назва пристрою

пристрій для операції додавання .

Вихідні дані :

1. Експлуатаційне призначення;

2.Тип арифметичної операції – додавання двійкових чисел;

3.Початковий код подання операндів – прямий;

4.Розрядність операндів – 16 біт;

5.Код виконання операції у суматорі – обернений;

6.Тип керуючого блока – автомат Мура з пам’яттю на JK-тригерах;

7.Ознака результату – парність молодшого байта;

9. Логічна операція – NOR.

10. |

Споживана потужність |

Вт |

11. |

Час виконання операцій (швидкодія) |

мкс |

12. |

Показник безвідмовності |

год. |

13. |

Елементна база мікросхеми ТТЛШ серії КР1533, КР1531. |

|

37

ЗМІСТ ПОЯСНЮВАЛЬНОЇ ЗАПИСКИ

Орієнтовний обсяг с.

Титульний лист |

|

|

Відомість проекту |

|

|

Анотація |

|

|

Вступ |

1 - 2 с. |

|

1. |

Розробка технічного завдання |

1 - 2 с. |

2. |

Розробка структурної схеми пристрою |

15 - 10 с. |

3. |

Розробка електричної принципової схеми пристрою |

10 - 15 с. |

4. |

Моделювання пристрою |

2 - 6 с. |

5. |

Порівняння результатів проектування та моделювання |

|

|

з вимогами ТЗ |

1 - 2 с. |

|

Висновки |

|

|

Література |

|

Зміст

Додатки

ГРАФІЧНА ЧАСТИНА

1.Структурна схема пристрою

2.Керуючий блок. Схема електрична принципова.

3.Операційні блок. Схема електрична принципова.

4.Схема моделювання.

5.Діаграми роботи.

6.Перелік елементів.

Дата видачі „___” _______201_ р

Термін подання КР до захисту |

___________________ |

Керівник _________________

/ підпис/

Завдання отримав __________

/ підпис

38

Додаток В Графи мікропрограми додавання

39