- •Содержание:

- •1. Анализ задания.

- •2. Описание работы шины isa ibm pc at.

- •3. Описание устройства, выбор и расчет элементов.

- •4. Программное обеспечение.

- •Текст программы:

- •Текст программы:

- •5. Список использованной литературы и программ.

- •Гук м. Аппаратные средства ibm pc. Энциклопедия. Спб: Питер, 1998.816 с.

- •Хоровиц п., Хилл у. Искусство схемотехники: Tом 1 и том 2. Пер с англ.6-е изд. Перераб. И доп.м.: Мир, 2001. – 704 с.

3. Описание устройства, выбор и расчет элементов.

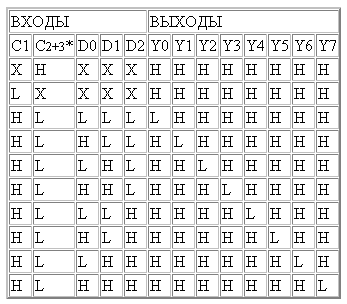

Описание устройства начнем с селектора адреса. Для устройства были выбраны свободные адреса в пространстве ввода/вывода персонального компьютера: 360h, 362h, 364h, 366h, 368h, 36Ah, 36Ch,36Eh (см. [1]). Адрес на линиях SA4-SA9 всегда одинаков, при совпадении адреса на этих линиях и появлении сигнала AEN (разрешения адреса) с помощью микросхем логики на входе С2 дешифратора формируется разрешающий сигнал низкого уровня. В зависимости от адреса на линиях SA1-SA3 дешифратор выставляет на одном из 8 выходов низкий уровень, для адреса 36Eh при этом формируется сигнал /IOCS16, чем подтверждается возможность 16-разрядного обмена. Таблица истинности дешифратора показана на рисунке 4.

Рис. 4

Выходы дешифратора подключены к логическим элементам “или - не” (кроме 8 выхода), на второй вход этих элементов поступает сигнал /IOW. Вначале на выходе логического элемента низкий уровень, в момент времени, когда дешифратор выставит на выходе низкий уровень (устройство распознало адрес), и появится низкий уровень сигнала /IOW, на выходе “или - не” появится высокий уровень. По положительному фронту сигнала на тактовом входе триггера информация с шины данных записывается в триггер.

Отдельно следует описать адрес 36Eh, после того как устройство распознает этот адрес (дешифратор выставит низкий уровень на восьмом выходе), сразу же посылается импульс на тактовый вход счетчика и изменяется адрес ячейки ОЗУ. Восьмой выход дешифратора вместе с /IOW через микросхему “или” подключен к входу ОЗУ, управляющему записью. Низкий уровень на выходе логического элемента появится только при наличии низкого уровня на выходе дешифратора и низкого уровня сигнала /IOW, с этого момента начнется запись в ОЗУ.

Непосредственно к шине подключаются микросхемы: дешифратор (КР1533ИД7), инверторы (КР1533ЛН1) и логический элемент “и” (КР1533ЛА2). Все эти микросхемы серии КР1533 и, следовательно, удовлетворяют требованиям, предъявляемым к приемникам магистральных сигналов. У них высокое быстродействие (задержки не превышают 15нс.) и малые входные токи (ток “0” – 0,2 мА) (см. [4]). Задержки на селекторе адреса определяются по формулам:

![]()

τ1 – задержка до выставления сигнала /IOCS16.

τ2 – задержка до изменения адреса ОЗУ.

τинв = 6 нс. – задержка на инверторе.

τи =12 нс. – задержка на микросхеме “и”.

τдеш = 12 нс. – задержка на дешифраторе.

τм =12 нс. – задержка на мультиплексоре.

τсч =10 нс. – задержка на счетчике.

Сигнал /IOCS16 должен быть выставлен спустя не более 90 нс. после начала обмена, сигнал /IOW выставляется не раньше 92 нс. после начала цикла записи, следовательно, задержка до изменения адреса ОЗУ не должна превышать 92 нс. Все эти условия выполняются.

Для хранения информации в селекторе адреса используется триггер. В качестве триггера используется микросхема КР531ТМ2, она имеет малое время задержки (12 нс.), содержит в корпусе два независимых триггера. Триггеры необходимы для хранения информации, управляющей микросхемами. Выходы триггеров подключены к:

Входу “In” ключей, переводящему ключи в режим пропускания при присутствии на нем высокого уровня (запись в триггер производится по адресу 360h).

Входу “ENA” преобразователей уровня, переводящему преобразователи в z-состояние при присутствии на нем низкого уровня (запись в триггер по адресу 362h).

Входу “ED” счетчиков, при низком уровне на нем происходит предустановка (запись в триггер по адресу 364h).

Входу “EС” счетчиков, при низком уровне на нем происходит разрешение счета (запись в триггер по адресу 366h).

Входу “V” мультиплексора, при высоком уровне на нем к тактовому входу счетчика подключается тактовый генератор (запись в триггер по адресу 368h).

Входам “BS0-BS1” ОЗУ, при низком уровне на них возможен доступ к первым двум байтам ячейки ОЗУ (запись в триггер по адресу 36Ah).

Входам “BS2-BS3” ОЗУ, при низком уровне на них возможен доступ ко вторым двум байтам ячейки ОЗУ (запись в триггер по адресу 36Ch).

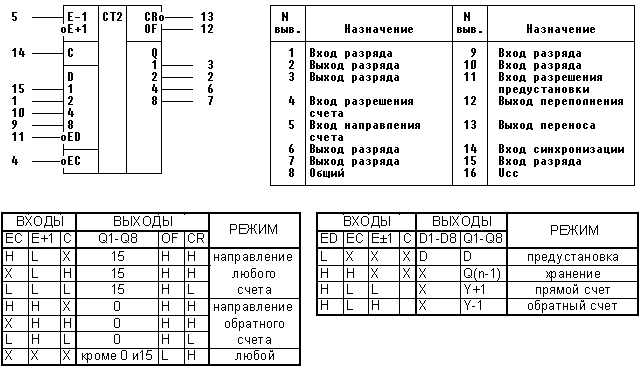

Основным элементом схемы является ОЗУ (EDI8L3265C20AC). Было выбрано именно это ОЗУ из-за быстродействия (50 МГц), объема (64 MB) и разрядности (32 разряда), также очень важна возможность выбора каждого байта ячейки. Для изменения адреса ячейки ОЗУ используется счетчик. Реализованы два способа управления счетчиком: подключение к счетчику тактового генератора и изменение состояния счетчика при обращении по адресу 36Eh. Для этого используется мультиплексор КР1533КП11. Для реализации первого способа используется тактовый генератор, построенный на базе кварца с частотой 10 МГц и двух инверторах. Этот блок генерирует импульсы с частотой 10 МГц, которые поступают на тактовый вход счетчика. В качестве счетчика используется микросхема КР1533ИЕ13 (рис. 5).

Рис. 5

Для увеличения разрядности счетчика используется выход “OF”, который подключается к тактовому входу следующего счетчика, при переполнении счетчика подается импульс на тактовый вход следующего счетчика. Входы “E” счетчиков заземлены, так как используется только прямой счет. Входы “разрешения счета” и “разрешения предустановки” подключены к триггерам, а входы “D1-D8” заземлены, это позволяет при необходимости обнулять счетчики. Также предусмотрена возможность остановки счетчиков при достижении адреса 1024 ячейки ОЗУ. Для этого третий выход третьего счетчика подключен вместе с выходом триггера, управляющим разрешением

счета, через микросхему “или” к входу разрешения счета. При возникновении высокого уровня на любом из входов микросхемы “или” счет останавливается, чтобы снова разрешить счет необходимо сбросить счетчик.

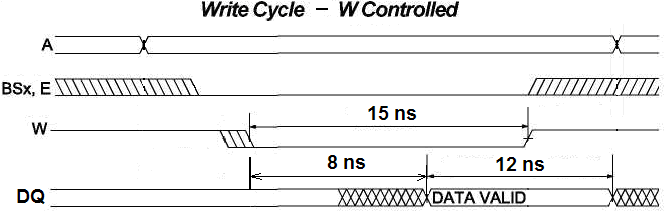

Для реализации второго способа управления счетчиком используется селектор адреса. При обращении по адресу 36Eh подается импульс на тактовый вход счетчика, и адрес ОЗУ увеличивается на единицу. Это позволяет записать данные в следующую ячейку ОЗУ. Временные диаграммы ОЗУ приведены на рисунке 6.

Рис. 6

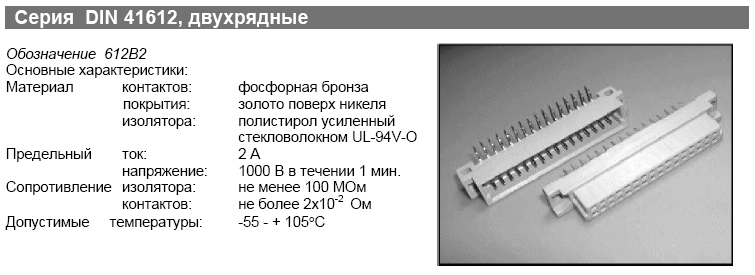

По заданию требовалось обеспечить выходные уровни ТТЛ и КМОП. Для этого данные из ОЗУ поступают параллельно на преобразователи уровня и на аналоговые ключи. В программном обеспечении пользователь выбирает желаемый выходной уровень, после этого программа записывает в триггер необходимую информацию, тем самым включает либо преобразователи уровня (ТТЛ-КМОП), либо аналоговые ключи. В качестве преобразователя уровня используется микросхема К564ПУ6, она имеет высокое быстродействие, и вход, переводящий выходы в z-состояние. В качестве аналогового ключа используется микросхема MAXIM IH5045, это ТТЛ – совместимая микросхема, она может оперировать аналоговыми сигналами до 15В, сопротивление в режиме “ВКЛ” – 25 Ом (см. [2]). Выходы преобразователей и ключей подключены к 32-входовым разъемам 612B2-32AB-FX (рис. 7). Разъем XP1 вытравливается на плате по принципу, описанному в главе 2.

Рис. 7

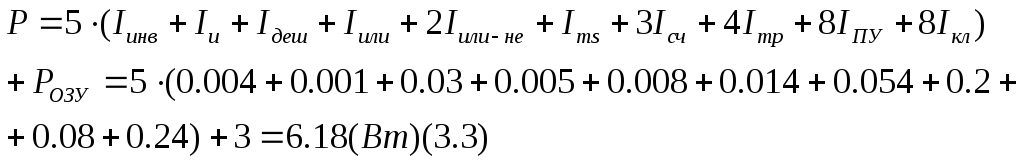

Максимальный ток, возможный при 5В на шине ISA 4,5А (мощность – 20,25 Вт.). Рассчитаем мощность, потребляемую устройством.

Iинв

– ток потребления инвертора.

Iинв

– ток потребления инвертора.

Iи – ток потребления микросхемы “и”.

Iдеш – ток потребления дешифратора.

Iили – ток потребления микросхемы “или”.

Iили-не – ток потребления микросхемы “или - не”.

Ims – ток потребления мультиплексора.

Iсч – ток потребления счетчика.

Iтр – ток потребления триггера.

IПУ – ток потребления преобразователя уровня.

Iкл – ток потребления аналогового ключа.

P – мощность, потребляемая устройством.

PОЗУ – максимальная мощность, потребляемая ОЗУ.

Следовательно, мощность, потребляемая устройством, укладывается в допустимые рамки.