- •Содержание:

- •1. Анализ задания.

- •2. Описание работы шины isa ibm pc at.

- •3. Описание устройства, выбор и расчет элементов.

- •4. Программное обеспечение.

- •Текст программы:

- •Текст программы:

- •5. Список использованной литературы и программ.

- •Гук м. Аппаратные средства ibm pc. Энциклопедия. Спб: Питер, 1998.816 с.

- •Хоровиц п., Хилл у. Искусство схемотехники: Tом 1 и том 2. Пер с англ.6-е изд. Перераб. И доп.м.: Мир, 2001. – 704 с.

Содержание:

Анализ задания.

Описание работы шины ISA IBM PC AT.

Описание устройства, выбор и расчет элементов.

Программное обеспечение.

Список использованной литературы и программ.

Приложение

Генератор последовательностей. Схема электрическая принципиальная.

Генератор последовательностей. Перечень элементов.

Модули. Перечень элементов.

1. Анализ задания.

Требуется разработать принципиальную схему и программное обеспечение модуля генератора последовательностей на шине ISA IBM PС AT. Генераторы последовательностей обычно используются для тестирования устройств, поэтому должна быть предусмотрена возможность загрузки различных последовательностей из файла. Предполагается написание специальной программы для создания таких файлов и программы для загрузки этой последовательности через шину ISA в устройство. Также при написании программного обеспечения необходимо предусмотреть возможность выбора выходных уровней. Шина ISA 16 разрядная, поэтому последовательность необходимо сначала загружать в 32 разрядное ОЗУ, а потом производить из него генерацию. Для этого требуется быстродействующее ОЗУ, также необходим тактовый генератор с частотой 10 МГц. Устройство не должно конфликтовать с остальными устройствами, подключаемыми к персональному компьютеру, что достигается выбором свободных адресов в пространстве ввода/вывода. Так как устройство подключается к шине ISA IBM PС AT персонального компьютера, то оно не требует индивидуального блока питания.

2. Описание работы шины isa ibm pc at.

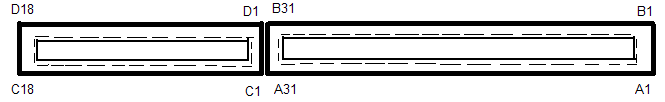

ISA (Industry Standard Architecture) - шина расширения, применявшаяся с первых моделей PC и ставшая промышленным стандартом. В компьютере XT использовалась шина с разрядностью данных 8 бит и адреса - 20 бит. В компьютерах AT ее расширили до 16 бит данных и 24 бит адреса. В таком виде она существует и поныне. Конструктивно шина выполнена в виде двух щелевых разъемов с шагом выводов 2,54 мм (рис. 1). Подмножество ISA-8 использует только 62-контактный слот (ряды А, В), в ISA-16 применяется дополнительный 36-контактный слот (ряды С, D).

Рис. 1

Шина обеспечивает возможность отображения 8- или 16-битных регистров на пространство ввода/вывода и памяти. Диапазон адресов памяти ограничен областью UMA (выше AOOOOh). Для шины ISA-16 опциями BIOS Setup может быть разрешено пространство между 15-м и 16-м мегабайтами памяти (при этом компьютер не сможет использовать более 15 Мбайт ОЗУ). Диапазон адресов ввода/вывода сверху ограничен количеством используемых для дешифрации бит адреса, нижняя граница ограничена областью адресов 0-FFh, зарезервированных под устройства системной платы. В PC была принята 10-битная адресация ввода/вывода, при которой линии адреса А[15:10] устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100h-3FFh, то есть всего 758 адресов 8-битных регистров. На некоторые из адресов претендуют системные устройства. Впоследствии диапазон адресов был расширен. При использовании адресов с большим количеством разрядов необходимо учитывать возможность присутствия на шине старых 10-битных адаптеров, которые "отзовутся" на адрес с подходящими ему битами А[9:0].

Шина ISA-8 может предоставить до 6 линий запросов прерываний, ISA-16 до 11. Часть их могут "отобрать" устройства системной платы или шина PCI. Шина позволяет использовать до трех 8-битных каналов DMA. На 16-битной шине доступны еще три 16-битных канала. Сигналы 16-битных каналов могут использоваться для прямого управления шиной устройством Bus-Master. При этом канал DMA применяется для арбитража шины, а адаптер Bus-Master формирует все адресные и управляющие сигналы шины, не забывая передать управление шиной процессору не позднее, чем через 15 мкс (чтобы не нарушить регенерацию памяти). Приведем описание контактов, используемых в курсовом проекте (рис. 2).

|

Контакт |

Название |

Направление |

Описание |

|

A2-A9 |

D7-D0 |

|

Шина данных D7-D0 |

|

A11 |

AEN |

|

Разрешение адреса |

|

A12-A31 |

A19-A0 |

|

Адресная шина A19-A0 |

|

B3 |

+5V |

|

+5 VDC |

|

B9 |

+12VDC |

|

+12 VDC |

|

B10 |

GND |

|

Общий вывод |

|

B13 |

/IOW |

|

Запись в порты ввода/вывода |

|

C11-C18 |

SD08-SD15 |

|

Шина данных D8-D15 |

|

D2 |

/IOCS16 |

|

Разрешение 16 разрядного обмена |

Рис. 2

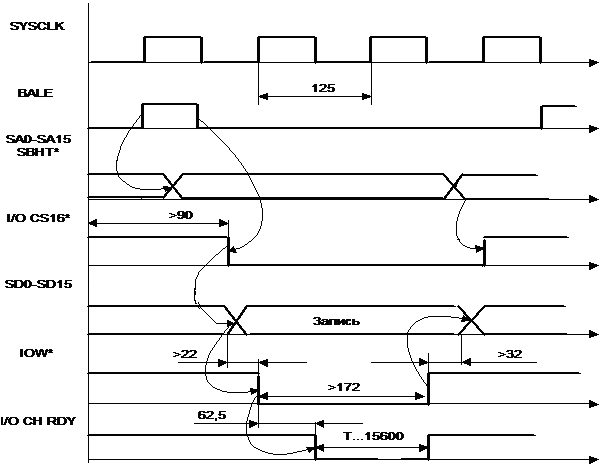

Операция "Запись в 16-и разрядное устройство ввода-вывода" (рис. 3).

В момент времени, совпадающий с началом тактовых импульсов, передаваемых по линии SYSCLK, процессор формирует сигнал BALE.

Получив этот сигнал, задатчик примерно через 20 нс. выставляет на системные линии адреса SA0...SA15 адрес исполнителя. Чаще всего адресная линия SA0 используется для определения разрядности обмена по шине.

На линию SBHE* (разрешение передачи старшего байта) выставляется сигнал высокого уровня, а на линию младшего разряда адреса SA0 сигнал низкого уровня. Эти сигналы указывают исполнителю, что будет производиться 16 битный обмен и удерживаются до момента снятия адреса.

Спустя не менее 50 нс. и не более Т/2 = 62,5 нс. сигнал BALE снимается, указывая устройствам, что адрес установлен. По заднему фронту сигнала BALE УВВ, подключенные к магистрали сравнивают адрес на линиях SA1...SA15 с собственным.

Устройство, распознавшее свой адрес, становится исполнителем и в подтверждении того, что может вести 16 битный обмен, выставляет сигнал I/O CS16. Этот сигнал должен быть выставлен не более чем через 90 нс. после начала обмена.

Спустя не менее чем через 70 нс. после начала цикла задатчик выставляет на линии SD0...SD15 данные.

Спустя не менее чем через 22 нс. после начала установки данных на линию IOW* выставляется стробирующий сигнал.

Исполнитель воспринимает сигнал IOW* и подготавливается к записи данных.

Сигнал IOW* снимается не менее чем через 172 нс. Задний возрастающий фронт сигнала позволяет исполнителю записать информацию.

Спустя не менее чем через 30 нс. после снятия сигнала IOW* задатчик снимает данные.

Если устройство не успевает выполнить требуемую от него команду в темпе магистрали, оно может приостановить на целое число периодов сигнала SYSCLK завершение цикла чтения или записи с помощью снятия (перевода в низкий уровень) сигнала I/O CH RDY (удлиненный цикл). Это производится в ответ на получение сигнала IOR* или IOW*. Сигнал I/O CH RDY может удерживаться низким не более 15,6 мкс, поскольку через этот интервал времени происходит регенерация оперативной памяти. В противном случае процессор переходит в режим обработки немаскируемого прерывания.

Рис. 3