- •Введение

- •1.1 Назначение устройства. Структурная схема

- •1.2. Функциональная схема сложения в двоично-десятичном коде

- •1.3 Элементная база устройства

- •1.4. Время выполнения операции

- •2. Проектирование вычитающего счетчика в коде грея

- •2.1. Принцип работы десятичного вычитающего счетчика в коде Грея

- •2.2. Элементная база счетчика

- •2.3. Синтез функций возбуждения триггеров

- •2.4. Анализ работы счетчика после сбоя

- •2.5. Временные диаграммы. Быстродействие счетчика

- •Библиографический список

- •Устройства дискретные

1.4. Время выполнения операции

Время задержки сигнала на микросхемах 155 серии составляет

сумму всех задержек элементов которые служат для получения последнего сигнала. Оно составляет

65+22+19+65+22+19+57=269 нс

65 нс среднее время задержки ИМ3

22 нс среднее время задержки СП1

19 нс среднее время задержки ЛЛ1

57 нс среднее время задержки ИМ2

Чтобы получить значение 3 тетрады нужно задействовать 2 сумматора ИМ3 два компаратора СП1 дважды микросхему ЛЛ1 и сумматор ИМ2

2. Проектирование вычитающего счетчика в коде грея

2.1. Принцип работы десятичного вычитающего счетчика в коде Грея

Код, связанным с именем Ф. Грея, который применил его для

построения преобразователя угловых перемещений в цифровой код,

обладающий явными преимуществами перед преобразователем с

двоичным кодом. Код Грея относится к таким, в которых при

переходе от любой кодовой комбинации к следующей изменяется

только один разряд. В схемотехнике счетчиков это свойство

устраняет одновременное переключение многих разрядов

характерное для двоичных счетчиков при некоторых переходах.

Одновременное переключение многих элементов создает такие

токовые импульсы в цепях питания схем, которые могут вызывать

сбои в работе схемы. В ряде БИС/СБИС применение двоичных

счетчиков большой разрядности не разрешается, и они заменяются

счетчиками с кодом Грея и последующим преобразованием кода Грея

в двоичный. Сложность счетчика с кодом Грея ненамного больше,

чем сложность двоичного счетчика, преобразователь кодов также

относительно прост.

При построении вычитающего десятичного счетчика в коде Грея каждое состояние кодируется последовательностью двоичных чисел.

Двоичные коды цифр десятичного счётчика в коде Грея

Рисунок 4 – Схема десятичного счетчика счётчика, построенного на универсальных D-триггерах.

Для наращивания разрядности счетчика используют дополнительные каскады триггеров к которым в качестве синхр. импульса подается сигнал межразрядного десятичного переноса который возникает при переходе из состояния 0 в состояние 1

2.2. Элементная база счетчика

Для проектирования заданного дискретного устройства (ДУ) в курсовой работе используется 1554 (74AC) серия ИМС, обзор основной элементной базы которой приведен ниже.

В настоящее время промышленность выпускает микросхемы серии КР1554, относящиеся по структуре к группе КМОП. Они практически по всем параметрам превосходят микросхемы ТТЛ и КМОП всех серий, лишь незначительно уступая по задержке переключения наиболее быстродействующим микросхемам ТТЛ.

Микросхемы выполнены в пластмассовом корпусе с числом выводов 14, 16 и 20. Шаг выводов - 2,5 мм. С плюсовым проводом питания всегда соединяют вывод с наибольшим номером, а с общим проводом - вывод с вдвое меньшим номером.

Напряжение питания микросхем серии КР1554 - от 2 до 6 В, параметры нормируют при значениях напряжения питания 3,3 ±0,3 В и 5 В ±10%. Рабочий температурный интервал -45...+85 С. Ток, потребляемый в статическом режиме, по нормам технических условий не превышает 4 мкА для простых микросхем и 8 мкА для микросхем средней степени интеграции; реально он значительно меньше.

Все микросхемы этой серии отличаются очень высокой нагрузочной способностью - при высоком логическом уровне на выходе, напряжении питания 4,5 В и выходном напряжении 3,86 В выходной вытекающий ток не менее 24 мА; при напряжении питания 3 В и выходном напряжении 2,56 В выходной ток не менее 12 мА. Таковы же нормы и на втекающий выходной ток при низком логическом выходном уровне при выходном напряжении 0,32 В для тех же значений напряжения питания.

Типовая средняя задержка распространения сигнала для простых микросхем - около 4 нс, тактовая частота последовательностных

микросхем достигает 150 МГц. Для сложных микросхем задержка распространения сигнала может доходить до 10...15 нс. Динамические параметры гарантированы при емкости нагрузки 50 пФ, максимально допустимая емкость - 500 пФ.

Микросхемы серии КР1554 значительно более устойчивы к воздействию статического электричества, чем микросхемы других серий структуры КМОП

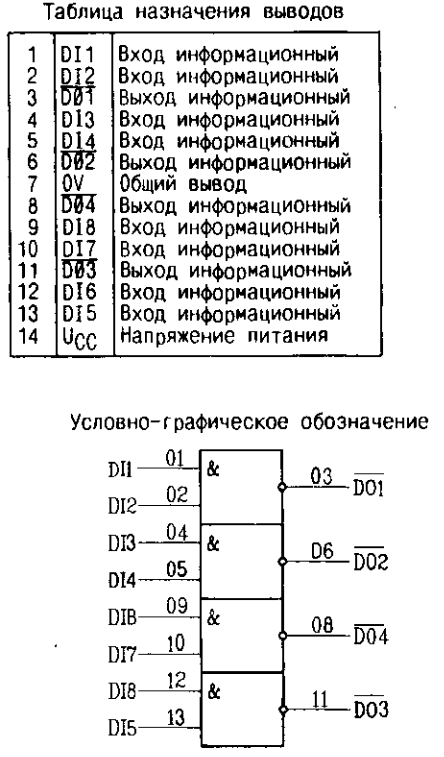

КР1554ЛА4

КР1554ЛА3

КР1554ТМ8

Микросхема КР1554ТМ8 содержит четыре D-триггера с общими входами асинхронного сброса 1 (установки в состояние низкого уровня) и входа синхронизации С. Триггеры микросхемы имеют прямые и инверсные выходы. Установка всех триггеров в состояние низкого уровня осуществляется подачей на асинхронный вход R напряжения низкого уровня. Загрузка информации от входов в триггеры осуществляется по положительному перепаду напряжения (фронту импульса) на входе С при этом на входе сброса R должно быть напряжение высокого уровня.