- •Введение

- •1.1 Назначение устройства. Структурная схема

- •1.2. Функциональная схема сложения в двоично-десятичном коде

- •1.3 Элементная база устройства

- •1.4. Время выполнения операции

- •2. Проектирование вычитающего счетчика в коде грея

- •2.1. Принцип работы десятичного вычитающего счетчика в коде Грея

- •2.2. Элементная база счетчика

- •2.3. Синтез функций возбуждения триггеров

- •2.4. Анализ работы счетчика после сбоя

- •2.5. Временные диаграммы. Быстродействие счетчика

- •Библиографический список

- •Устройства дискретные

Введение

В процессе курсового проектирования необходимо разработать два цифровых устройства.

Все цифровые устройства (ЦУ) принято разбивать на два класса:

комбинационные цепи (КЦ) и последовательностные ЦУ (автоматы с

памятью – АП).

Выходные величины КЦ зависят только от текущего значения входных величин (аргументов). Предыдущие величины значения не имеют. После завершения переходных процессов в КЦ на их выходах устанавливаются выходные величины, на которые характер переходных процессов влияния не оказывает.Во время переходных процессов на выходах КЦ появляются временные сигналы, не предусмотренные описанием работы КЦ и называемые рисками. Со временем они исчезают, и выход КЦ приобретает значение, предусмотренное логической формулой, описывающей работу цепи. С этой точки зрения переходные процессы в КЦ не опасны. Сумматор относится к категории КЦ.

Переходы АП из одного состояния в другое начинаются с некоторого исходного состояния Q0, задание которого также является частью задания автомата. Следующее состояние зависит от Q0 и поступивших входных сигналов X. В конечном счете, текущее состояние и выходы автомата зависят oт начального состояния и всех векторов X, поступавших на автомат в предшествующих сменах входных сигналов. Таким образом, вся последовательность входных сигналов определяет последовательность состояний и выходных сигналов. Это объясняет название «последовательностные схемы», также применяемое для обозначения АП.

Автоматы с памятью в каноническом представлении разделяют на две части: память и комбинационную цепь. На входы КЦ подаются входные сигналы и сигналы состояния АП. На ее выходе вырабатываются выходные сигналы и сигналы перевода АП в новое состояние.

ПРОЕКТИРОВАНИЕ СУММАТОРА ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ

1.1 Назначение устройства. Структурная схема

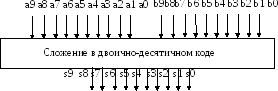

По заданию нам необходимо создать сумматор двоично-десятичных чисел. Исходя из задания структурную схему можно представить в виде, представленном на рисунке 1.

Рисунок 1 – Структурная схема устройства.

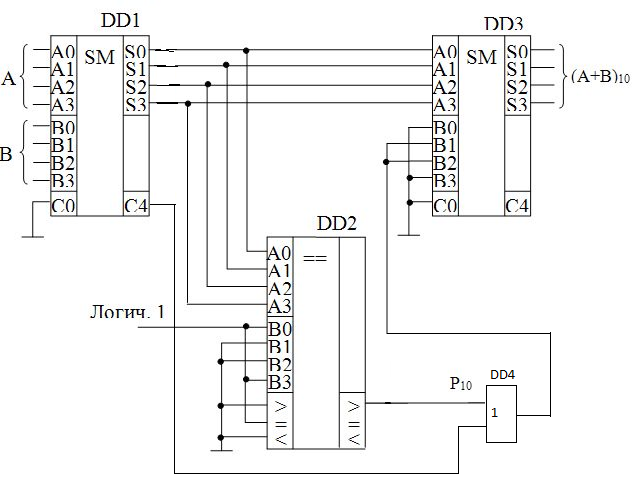

1.2. Функциональная схема сложения в двоично-десятичном коде

По общему правилу сложения двоично-десятичных чисел к тетрадам числа с большим модулем прибавляются дополнительные до числа 910= 10012коды тетрад другого числа. Поскольку максимальное значение чисел на входах и выходе арифметического устройства ограничено величиной 199, в сумматоре достаточно 2,25 декад.

Рисунок 2 – Сумматор двоично-десятичных чисел

На рисунке 2 изображена схема одной декады сумматора двоично-десятичных чисел, выполненного на интегральных 4-разрядных двоичных сумматорах DD1 иDD3 , компаратореDD2 и одном элементе ИЛИDD4. Операцию сложения выполняет сумматор DD1. При переполнении разрядной сетки сумматора формируется сигнал Р4.При сумме большей или равной десяти на выходе микросхемы DD2, которая является схемой сравнения двоичных чисел, формируется сигнал переноса Р10. На второй вход (B0…B3) микросхемы DD2 подается двоичный эквивалент числа 9 (1001).Затем сигналы Р4 и сигнал Р10идут наDD4 из которого выходит либо лог. 1 либо лог. 0. При отсутствии сигнала переноса на выходе микросхемы DD4 повторяется код числа, который был на выходе DD1, поскольку на входы В поданы лог. 0. При наличии сигнала с микросхемыDD4= 1 на входах В1 и В2 устанавливаются лог. 1, что соответствует коду числа 6.