- •Содержание

- •4.2.3. Сопроцессор 9

- •4.2.4. Контроллер прерываний 9

- •Структура эвм – магистральная 3-х шинная,______________________________________________________

- •2. Исходные данные Структура эвм – магистральная 3-х шинная,

- •3. Введение

- •4. Разработка структурной схемы гипотетической эвм

- •4.1. Структурная схема эвм

- •4.2. Описание функционирования структурной схемы эвм

- •4.2.1. Процессор

- •4.2.2. Многоблочная оперативная память

- •4.2.3. Сопроцессор

- •4.2.4. Контроллер прерываний

- •Клавиатура

- •4.2.6. Монитор

- •5. Разработка функциональной схемы кпдп и алгоритма запуска кпдп

- •Заключение

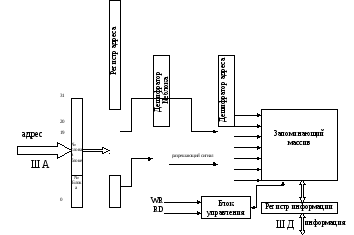

4.2.2. Многоблочная оперативная память

Оперативной памятью называют устройство, которое служит для хранения информации (данных программ, промежуточных и конечных результатов обработки), непосредственно используемые в процессе выполнения операций в арифметическо-логическом устройстве и устройстве управления процессором [2].

Многоблочная оперативная память представляет собой блоки одинакового размера по 2^20=1Мb количеством до 2^12=4096 штук, которые выглядят, как представлено на рисунке 4

Элементарный блок ОП

Рис. 4

Данная оперативная память не подразумевает виртуальность памяти, т.е. она не может быть расширена за счет ВЗУ, а физический адрес ячейки памяти формируется следующим образом:

Физ. адрес = № блока ОП + смещение (адрес) в блоке

ОП функционирует следующим образом. С МП или КПДП приходит адрес по ША, который записывается в регистр адреса ОП, после чего старшие 12 разрядов дешифрируются в дешифраторе блока ОП и если адрес принадлежит данному блоку выдается разрешающий сигнал на дешифратор адреса в блоке, который формирует адрес ячейки памяти в запоминающем массиве. После чего по шине управления приходит сигнал WR или RD от МП или КПДП и происходит запись или чтение информации в/из ОП.

4.2.3. Сопроцессор

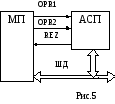

В данной структурной схеме у нас находится арифметический сопроцессор, который выполнят функции деления и умножения. Структурная схема функционирования

п редставлена

на рисунке 5 и работает следующим разом:

при поступлении по ШД данных в МП и

одновременно в АСП (без кода операции),

содержащие коды операций (программу),

дешифратором кода операций МП они

дешифрируются, после чего если текущая

дешифрированная операция является

операцией деления или умножения

микропроцессором выдаётся соответственно

сигналOPR1 или OPR2на

сопроцессор и не выполняет ее, а ждёт

результатов

редставлена

на рисунке 5 и работает следующим разом:

при поступлении по ШД данных в МП и

одновременно в АСП (без кода операции),

содержащие коды операций (программу),

дешифратором кода операций МП они

дешифрируются, после чего если текущая

дешифрированная операция является

операцией деления или умножения

микропроцессором выдаётся соответственно

сигналOPR1 или OPR2на

сопроцессор и не выполняет ее, а ждёт

результатов

с сопроцессора. При получении сигналов OPR1 или OPR2 на сопроцессор он выполняет операцию деления/умножения и выставляет результат на ШД. После этого АСП выдает сигналREZ на МП сигнализируя, что результат операции находится на ШД и при получении данного сигнала МП считывает результат в аккумулятор и начинает считывать следующую команду.

4.2.4. Контроллер прерываний

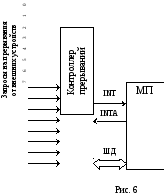

В данном курсовом проекте задана система прерываний в виде радиальной (макро) системы.

Р адиальная

система организовывается с помощью

контроллера прерываний, который

занимается арбитражем прерываний и

выдает сообщения о приходе прерывания

процессору.

адиальная

система организовывается с помощью

контроллера прерываний, который

занимается арбитражем прерываний и

выдает сообщения о приходе прерывания

процессору.

Процесс прерывания происходит следующим образом и представлен на рисун-

ке 6: данный контроллер реализует восьмиуровневою систему прерываний. Запросы на прерывания поступают на входы, пронумерованные от 0 до 7 (приоритет растёт с увеличение номера входа). При одновременном поступлений нескольких запросов контроллер

примет наиболее приоритетное и будет ожидать прихода сигналаINTA=1(разрешение прерывания) с МП, который формируется после окончания цикла команды, что обеспечивает макро уровень прерываний. При поступлении сигналаINTAна КП, он вырабатывает общий сигнал прерыванияINTи одновременно формирует командуRST Nна ШД, в которой содержится номер вектора прерывания (0÷7). По командеRSTМП записывает в стек содержимое счётчика команд, регистра флагов и загружает в счетчик команд адрес начальный адрес подпрограммы обработчика прерываний. КодN*4определяет адрес вектора прерывания в таблице векторов прерываний, а каждый вектор содержит адрес подпрограммы обработчика прерываний. После обработки прерывания МП восстанавливает счетчик команд и регистр флагов, и продолжат выполнять прерванную программу.