- •Содержание

- •4.2.3. Сопроцессор 9

- •4.2.4. Контроллер прерываний 9

- •Структура эвм – магистральная 3-х шинная,______________________________________________________

- •2. Исходные данные Структура эвм – магистральная 3-х шинная,

- •3. Введение

- •4. Разработка структурной схемы гипотетической эвм

- •4.1. Структурная схема эвм

- •4.2. Описание функционирования структурной схемы эвм

- •4.2.1. Процессор

- •4.2.2. Многоблочная оперативная память

- •4.2.3. Сопроцессор

- •4.2.4. Контроллер прерываний

- •Клавиатура

- •4.2.6. Монитор

- •5. Разработка функциональной схемы кпдп и алгоритма запуска кпдп

- •Заключение

4.2.1. Процессор

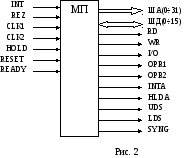

При описании микропроцессора мы возьмем в качестве прототипа КР580ВМ80, но изрядно модифицированный представленный на рисунке 2, а упрощённая структура на рисунке 3.

Где на рисунках:

INT – запрос на прерывание, REZ – сигнал от сопроцессора о окончании вычисления операции, CLK1÷CLK2 – вход тактового сигнала от генератора (фаза1,фаза2), HOLD – сигнал захвата шины от КПДП, RESET – вход сброса система в исходное состояние, READY – готовность ВУ к приёму данных, ША÷ШД – шины адреса и данных, RD/WR – сигналы на чтение/запись из/в ОП или ВУ в зависимости от сигнала I/O, I/O – запись или чтение в ВУ при наличии сигналов RD/WR, OPR1÷OPR2 – сигналы в сопроцессор об пришествии операции деления/умножения, INTA – сигнал разрешения прерывания, UDS/LDS – сигнал о передачи в ОП старшего/младшего байта данных, SYNG – сигнал начала каждого машинного цикла, АЛУ– арифметическо-логическое устройство, УУ – устройство управления, БУР – блок управляющих регистров.

В структурной схеме выделено несколько основных блоков, которые предназначены для следующих функций:

АЛУ – арифметическо-логическое устройство процессора выполняет логические и арифметические операции над данными любых типов. Характер выполняемой АЛУ операции задаётся командой программы.

УУ – устройство управления вырабатывает последовательность управляющих сигналов, инициирующих выполнение соответствующей последовательности микроопераций, обеспечивающей реализацию текущей команды.

БУР – блок управляющих регистров предназначен для временного хранения управляющей информации. Он содержит регистры и счётчики, участвующие в управлении вычислительным процессом: регистры, хранящие информацию о состоянии микропроцессора (регистр флагов или слово состояния), регистр-счетчик адреса команды –счётчик команд, счетчики тактов и др.

Блок регистров памяти небольшой емкости необходим для ускорения процесса вычислений и предназначены для хранения операндов, а также в качестве базовых и индексных регистров или указателя стека.

Блок связи (интерфейс процессора) организует обмен информацией процессора с ОП и защиту участков оперативной памяти от недозволенных данной программе обращений, а также связь процессора с периферийными устройствами и внешним по отношению к ЭВМ оборудованием.

Данный микропроцессор представленный на рисунке 2 имеет шину адреса 32-разрядную, 16-разрядную шину данных, шину управления, состоящею из следующих выводов и выполняющие следующие функции:

При нажатии кнопки сброса или пуска на вход МП RESET приходит уровень логической единицы, которая устанавливает МП в исходное состояние, т.е. сбрасывается триггера разрешения прерывания и захвата шины, а также сбрасывается счетчик команд на 0 адрес загрузки процессора. Входы CLK1÷CLK2 необходимы для того чтобы тактировать МП и синхронизировать его работу от генератора (фаза1,фаза2), входной сигнал HOLD – запрос на захват шины от КПДП, HLDA – выходной сигнал МП подтверждение захвата шины, при этом ША и ШД переключается в третье состояние (подробнее, принцип захвата шины описан в разделе 5). OPR1/OPR2 – сигналы операций деления/умножения на сопроцессор, а REZ – сигнал от сопроцессора о завершении операции деления/умножения (пункт 4.2.3.).

RD/WR, I/O-управляющие сигналы чтения/записи микропроцессором данных из ОП (при I/O=0) или ВУ(при I/O=1) подробнее в пункте 4.2.2. UDS – сигнал высокого уровня при записи/чтении старшего байта в ОП, LDS – при передачи младшего байта. SYNG – сигнал синхронизации (начало каждого машинного цикла).