opevs

.pdf

1

Оглавление

1. |

Модели и система параметров логических элементов .............................. |

3 |

2. |

Типы выходных каскадов цифровых элементов: логический выход. ...... |

6 |

3.Типы выходных каскадов цифровых элементов: выходы с тремя |

|

|

состояниями. ...................................................................................................... |

7 |

|

4.Типы выходных каскадов цифровых элементов: выход с открытым |

|

|

коллектором ....................................................................................................... |

8 |

|

5. Паразитные связи цифровых элементов по цепям питания, фильтрация |

|

|

питающих напряжений в схемах цифровых устройств ................................. |

10 |

|

6.Типовые ситуации при построении цифровых устройств на интегральных

микросхемах...................................................................................................... |

13 |

|

7. Согласование уровней сигналов. Сопряжение КМОП- и ТТЛ- |

|

|

схем.Сопряжение КМОП- и ТТЛ-схем ........................................................... |

17 |

|

8. Схемы низковольтовой КМОП-логики и их сопряжение с другими |

|

|

схемами. ............................................................................................................ |

20 |

|

9. Элементы индикации.................................................................................... |

22 |

|

10.Риски в комбинационных схемах ............................................................... |

25 |

|

11.Дешифраторы, преобразователи кодов. ..................................................... |

27 |

|

12. |

Шифраторы ................................................................................................. |

30 |

13. |

Мультиплексоры......................................................................................... |

32 |

14Демультиплексоры. ...................................................................................... |

34 |

|

15. |

Компараторы (схемы сравнения)............................................................... |

35 |

16. |

Синхронизация в цифровых устройствах ................................................. |

38 |

17. |

Регистры. ..................................................................................................... |

41 |

18. |

Счетчики. Двоичные счетчики. ................................................................. |

47 |

19. |

Двоично-кодированные счетчики с произвольным модулем .................. |

52 |

20. |

Счетчики с недвоичным кодированием. ................................................... |

54 |

21. |

Полиномиальные счетчики. ....................................................................... |

59 |

22. |

Представление чисел с фиксированной запятой. ..................................... |

63 |

|

|

|

|

|

|

2 |

|

23. |

Представление чисел с плавающей запятой. ............................................ |

66 |

|

24. |

Погрешности представления чисел. .......................................................... |

69 |

|

25. |

Кодирование двоичных чисел со знаком: прямой код. ............................ |

72 |

|

26. |

Кодирование двоичных чисел со знаком: дополнительный код. ............ |

73 |

|

27. |

Кодирование двоичных чисел со знаком: обратный код. ........................ |

74 |

|

28. |

Сложение и вычитание двоичных чисел в форме с фиксированной |

|

|

запятой со знаком в прямых кодах. Особенности выполнения операций над

числами без знака. ............................................................................................ |

75 |

|

29 |

Сложение и вычитание двоичных чисел в форме с фиксированной |

|

запятой со знаком в дополнительных кодах ................................................... |

76 |

|

30. |

Сложение и вычитание двоичных чисел в форме с фиксированной |

|

запятой со знаком в обратных кодах. .............................................................. |

77 |

|

31 |

Переполнение при сложении чисел с фиксированной запятой. |

|

Модифицированные коды................................................................................ |

78 |

|

32. |

Умножение чисел с фиксированной запятой: общая схема |

|

целочисленного умножения............................................................................. |

79 |

|

33 |

Методы умножения двоичных чисел без знака. ........................................ |

82 |

34 |

Умножение двоичных чисел со знаком. Умножение чисел в |

|

дополнительном коде. ...................................................................................... |

84 |

|

35 |

Логические методы ускорения умножения................................................ |

86 |

36 |

Деление чисел с фиксированной запятой. Методы деления двоичных |

|

чисел без знака. ................................................................................................. |

89 |

|

37. |

Деление двоичных чисел со знаком. Деление чисел в дополнительном |

|

коде .................................................................................................................... |

91 |

|

38. |

Выполнение операций над числами в форме с плавающей запятой....... |

92 |

39. |

Особенности двоично-десятичного кода: ................................................. |

96 |

1.Четыре значения напряжений задают границы отображения переменных (0 и 1) на выходе и входе элемента

4

на входе  и

и

на выходе  и

и

Для уровня  опасны отрицательные помехи, снижающие его. Допустимая

опасны отрицательные помехи, снижающие его. Допустимая

статическая помеха (т.е. помеха любой длительности) равна

.

.

Для уровня  опасны положительные помехи. Допустимая статическая помеха равна

опасны положительные помехи. Допустимая статическая помеха равна

.

2.Четыре значения токов – входные и выходные токи в обоих логических состояниях

и

и

и

и

При высоком уровне выходного напряжения из элемента-источника ток вытекает, цепи нагрузки ток поглощают. При низком уровне выходного напряжения элемента-источника ток нагрузки втекает в этот элемент, а из входных цепей элементов-приемников токи вытекают. Эти токи позволяют контролировать соблюдение нагрузочных ограничений, обязательное для всех элементов схемы ЦУ.

3.Коэффициент объединения по входу. Задает максимальное число входов элемента, т.е. максимальное число элементов, выходы которых могут быть объединены через входы данного.

4.Коэффициент объединения по выходу (коэффициент разветвления). Задает максимальное число входов элементов, которые могут быть соединены с

выходом данного элемента без нарушения режима его работы (нагрузочных ограничений).

Если некоторый элемент в схеме оказывается перегруженным по выходу, то необходимо произвести эквивалентное преобразование схемы с целью его разгрузки. Это преобразование сводится

либо к введению в схему усилителя

либо к дублированию данного элемента.

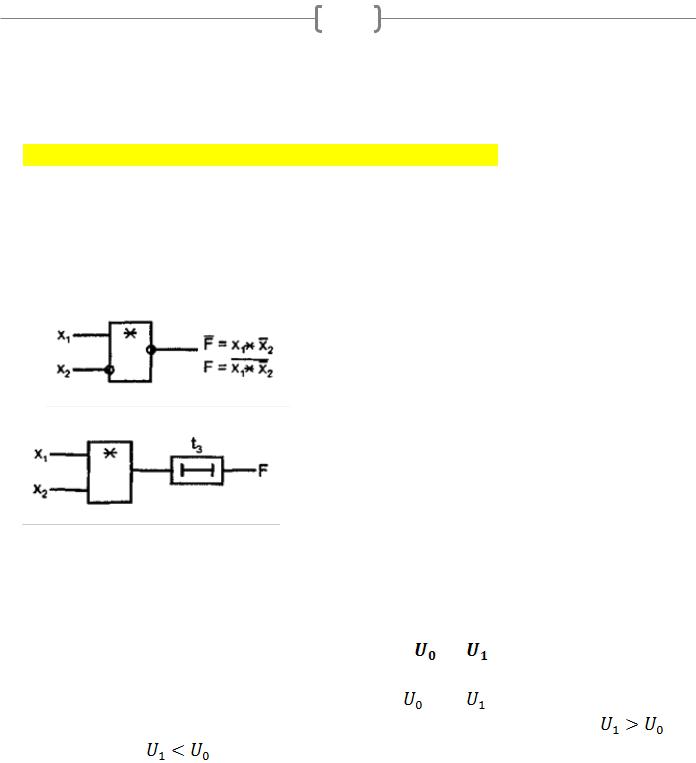

Быстродействие логических элементов (динамические параметры)

Быстродействие логических элементов определяется скоростями их перехода из одного состояния в другое

Быстродействие ЦУ определяется задержками сигналов, как в логических элементах, так и в цепях их межсоединений.

Длительности характерных этапов переходных процессов при переключении ЛЭ отсчитываются по так называемым измерительным уровням

Моментом изменения логического сигнала считают момент достижения им

порогового уровня  . Часто за пороговый уровень принимают середину логического перепада сигнала, т.е.

. Часто за пороговый уровень принимают середину логического перепада сигнала, т.е.

5

Для ЛЭ задаются задержки распространения сигнала при изменении выходного

напряжения элемента от  до

до  и обратно (

и обратно ( и

и  ). Часто для упрощения расчетов пользуются усредненным значением задержки

). Часто для упрощения расчетов пользуются усредненным значением задержки

Длительность логического перепада сигнала (фронта или среза) определяется

между уровнями сигнала, которые отличаются от значений  и

и  на величину

на величину  , где

, где  – фактическое значение перепада напряжения (на рисунке показана длительность фронта входного сигнала

– фактическое значение перепада напряжения (на рисунке показана длительность фронта входного сигнала  )

)

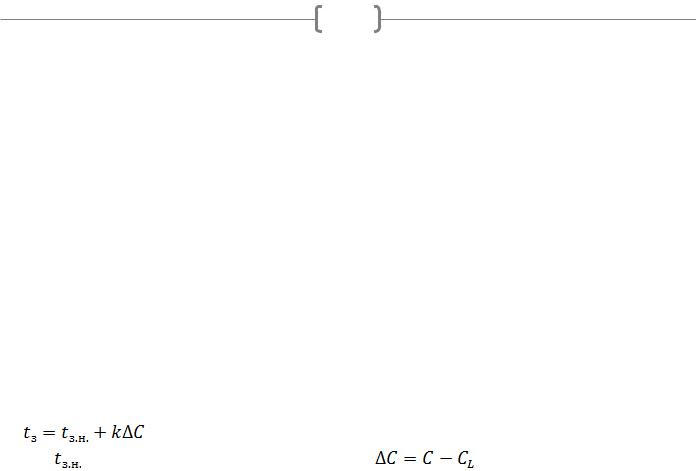

На быстродействие ЦУ влияют также емкости, на перезаряд которых требуются затраты времени

Для подключаемой к выходу элемента емкости приводятся два значения:

номинальная емкость  (L от Load)

(L от Load)

Соответствует условиям измерения задержек сигналов. Именно для нее приводятся значения задержек сигналов в справочных данных. Если реальная нагрузочная емкость отличается от номинальной, то изменятся и значения задержек. Значения реальных задержек можно оценить с помощью соотношения

|

, |

|

где |

– номинальное значение задержки; |

; С – фактическое значение |

нагрузочной емкости; k – коэффициент, величина которого задается для каждой серии элементов индивидуально

предельно допустимая емкость

Указывает границу, которую нельзя нарушать, поскольку при этом работоспособность элемента не гарантируется Мощности потребления логических элементовТаким образом, полная мощность зависит от частоты переключения

элемента, что и следует учитывать при ее подсчете.

6

2. Типы выходных каскадов цифровых элементов: логический выход.

Цифровые элементы могут иметь выходы следующих типов: логические, с

открытым коллектором, с третьим состоянием, с открытым эмиттером.

Наличие четырех типов выходов объясняется различными условиями работы элементов в логич.цепях, в магистрльно-модульных МПС и т.д.

Логический вход:

Формирует 2 уровня выходного напряжения  Вых.сопротивление стремяться сделать малым, способным развивать большие токи

Вых.сопротивление стремяться сделать малым, способным развивать большие токи

для перезаряда емкостных нагрузок и, сл-но, для получения высокого быстродействия элемента. Такой же тип имеют большинство логич.элементов, используемых в схемах цифровых устройств. В схемах логич.выходов оба фронта вых.напряжения формируются с помощью активных транзисторов, работающих противофазно, что обеспечивает малые выходные сопротивления при любом направлении переключения выхода.

Особенность таких выходов состоит в том, что их нельзя соединять параллельно.

Это создает логическую неопределенность, т.к. в точке соединения выходов, находящихся в разл.логич.состояниях возникает уравнительный ток, кот.вследствие малых величин выходных сопротивлений может достигать большой величины, что может вывести элементы из строя. Вторая особенность логич. Выхода связана с протеканием через оба транзистора коротких импульсов тока при переключениях из этого логич.состояния в другое. Эти токи протекают от источника питания на общую точку. В статических состояниях таких токов быть не может, т.к. транзисторы Т1 и Т2 в противофазе и один из них всегда заперт. Однако в пееходном процессе из-за некоторой несинхронности переключения транзисторов возникает кратковременная ситуация, в кот.проводят оба транзистора, что и порождает короткий импульс сквозного тока значительной величины.

Замечание:

Импульсные токи возникают в цепях питания логич.элементов не только из-за описанного выше явления, но и вследствие перезаряда емкостей при их переключениях. Это важное обстоятельство свидетельствует о неустранимости того, как наличие импульсных токовых помех в цепях питания цифр.элементов.

7

3.Типы выходных каскадов цифровых элементов: выходы с тремя состояниями.

Элементы с тремя состояниями кроме состояний 0 и 1 имеют еще состояние «отключено», в кот. Ток вых.цепи пренебрежимо мал. В это состояние элемент переводится специальным управляющим сигналом, обеспечивающим запертое состояние обоих транзисторов вых.каскадов. Сигнал управления элементом типа ТС обычно обозначается как ОЕ (output enable). При наличии разрешения (ОЕ=1) эл.работает как обычно, а при отсутствии разрешения (ОЕ=0) переходит в состояние «отключено». В ЦУ исп. Буферные элементы типа ТС для управляемой передачи сигналов по тем или линиям. Элементы могут быть неинвертирующими и инвертирующими, а сигналы ОЕ – с акт.высоким или низким уровнем., что приводит к наличию четырех типов буферных каскадов.

Элементы типа ТС можно соединять параллельно при условии, что в любой момент времени активным может быть только один из них. В этом случае отключенные выходы не мешают активному формировать сигналы в точке соединения выходов. Эта возможность позволяет применять элементы типа ТС в магистральномодульных МПС, где многие источники информации поочередно пользуются одной и той же линией связи. Элементы типа ТС сохраняют такие достоинства элементов с логич.выходом, как быстродействие и высокая нагрузочная способность.

8

4.Типы выходных каскадов цифровых элементов: выход с открытым коллектором

Цифровые элементы (логические, запоминающие, буферные) могут иметь выходы следующих типов:

логические;

с открытым коллектором (стоком);

с третьим состоянием;

с открытым эмиттером (истоком).

Выход с открытым коллектором (стоком)

Элементы с открытым коллектором (типа ОК) или стоком (типа ОС) имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор или сток которого не соединен с какими-либо цепями внутри микросхемы. Транзистор управляется от предыдущей части схемы элемента так, что может находиться в насыщенном (для МОП-транзистора просто открытом) или запертом состоянии. Насыщенное (открытое) состояние трактуется как отображение логического нуля, запертое — единицы

1)типа ОК 2)типа ОС Насыщение транзистора в схеме с открытым коллектором обеспечивает на выходе

напряжение  (малое напряжение насыщения «коллектор-эмиттер»

(малое напряжение насыщения «коллектор-эмиттер»  ). Запирание

). Запирание

транзистора какого-либо уровня напряжения на выходе элемента не задает, выход при этом имеет фактически неизвестный «плавающий» потенциал, так как не подключен к каким-либо цепям схемы элемента. Поэтому для формирования высокого уровня напряжения при запирании транзистора на выходе элемента с открытым коллектором требуется подключать внешний резистор (или другую нагрузку), соединенный с источником питания Несколько выходов типа ОК можно соединять параллельно, подключая их к общей

для всех выходов цепочке  – R

– R

Достоинства

Защищенность элементов с ОК при работе в магистрально-модульных системах от повреждений из-за ошибок управления, приводящих к одновременной выдаче на шину нескольких слов

возможность реализации дополнительных операций монтажной логики

Недостаток

большая задержка переключения из 0 в 1. При этом переключении происходит

заряд выходной емкости сравнительно малым током резистора R.

9

Сопротивление R нельзя сделать слишком малым, так как это приводит к большим токам выходной цепи в статическом режиме при насыщенном состоянии выходного транзистора. Поэтому положительный фронт выходного напряжения формируется относительно медленно с постоянной времени  . До порогового напряжения экспоненциально нарастающий сигнал изменится за время

. До порогового напряжения экспоненциально нарастающий сигнал изменится за время  , что и составляет задержку переключения

, что и составляет задержку переключения

10

10

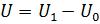

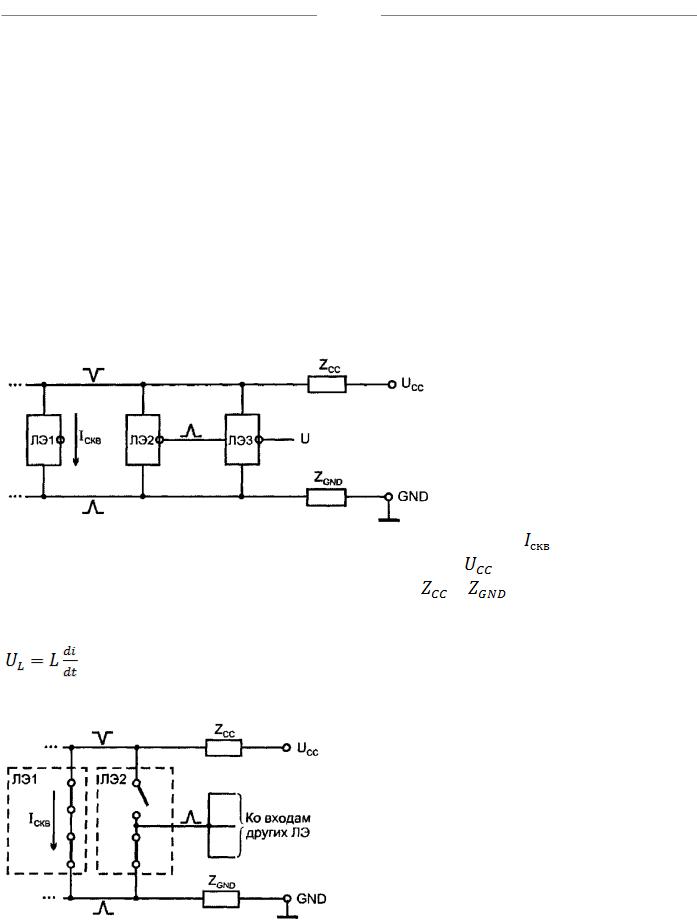

5. Паразитные связи цифровых элементов по цепям питания, фильтрация питающих напряжений в схемах цифровых устройств

Одной из важнейших задач при проектировании ЦУ является борьба со сбоями из-за помех. Типовой проблемой здесь является наличие токовых импульсов в цепях

питания ИС.

При переключении элементов в цепях питания создаются кратковременные импульсные токи, благодаря чему сами элементы становятся источниками помех для соседних элементов. Токовые импульсы в цепях питания создаются:

сквозными токами выходных каскадов

токами перезаряда емкостей.

Для определенности рассмотрим сквозные токи, то же самое относится и к токам перезаряда емкостей.

Импульс |

сквозного тока переключающегося |

элемента |

ЛЭ1 |

протекает через |

|

транзисторы выходного каскада от источника питания |

на общую точку схемы |

||||

GND через линии, имеющие полные сопротивления |

и |

|

|

||

Главную |

часть сопротивлений составляют |

индуктивности |

линий, на которых |

||

происходит падение напряжения

Протекание сквозного тока создает на линии питания отрицательный импульс, а на линии общей точки («земли») – положительный

Эти импульсы воздействуют на подключенный вблизи ЛЭ1 элемент 2. Если ЛЭ2

а

находится в состоянии логического нуля, то его выход через насыщенный транзистор выходного каскада связан с линией GND. Следовательно, импульс с этой линии попадет на выход элемента 2, откуда может распространяться и далее по обычным