- •Кафедра электротехники, электроснабжения, автоматики и информационных технологий

- •1.1. Элементы зонной теории твердого тела.

- •1.2. Полупроводники p- иn- типов

- •1.3. Полупроводниковый p-n–переход

- •1.5. Классификация полупроводниковых диодов

- •Диффузионные диоды получают за счет диффузии в полупроводниковую пластину примеси, находящейся в газообразной, жидкой или твердой фазах.

- •1. 6. Выпрямительные диоды

- •2.3. Биполярные транзисторы

- •2.4. Полевой транзистор

- •Раздел 2. Источники вторичного электропитания

- •Раздел 3. Электронные и импульсные устройства.

- •5.4.Операционные усилители (оу): базовые схемы включения операционных усилителей; амплитудно-частотная характеристика (ачх) оу; компараторы на оу.

- •Раздел 4. Основы цифровой и микропроцессорной техники

- •7.1. Логические функции. Описание логических функций с помощью таблиц истинности. Базовые логические функции.

- •7.2. Логические вентили ттл, ттлш, моп и кмоп структур; вентили с тремя состояниями.

- •7.3. Триггеры на логических элементах

7.3. Триггеры на логических элементах

7.3.1. Общие сведения о триггерах

Триггеры выполняются на двух ключевых схемах, связанных между собой перекрестными, гальваническими положительными обратными связями. Транзистор имеет два устойчивых состояния в случае транзисторного триггера: одно – VT1насыщен,VT2заперт – такое состояние соответствует 0; второе –VT1заперт,VT2насыщен. Такое состояние триггера соответствует 1. В любом из этих состояний триггер может находиться сколь угодно долго.

Переход триггера из одного устойчивого состояния в другое происходит скачком под воздействием импульса или постоянного напряжения. Скачкообразный переход обеспечивается положительными обратными связями между ключами.

Триггеры используются в вычислительной техниее как элементарные ячейки памяти на 1 бит информации или как делители частоты. На их основе выполняются счетчики импульсов, регистры, запоминающие и другие цифровые устройства. Триггеры могут быть построены на логических элементахИ-НЕлюбых серий. В зависимости от функционального назначения и организации логических связей триггеры подразделяются на следующие виды:

RS– триггеры – триггеры с раздельной установкой состояний 0 и 1.

D-триггеры – триггеры с задержкой смены состояния (например, на 1 такт).

Т-триггеры – счетные триггеры; их состояние меняется под действием каждого входного счетного сигнала.

JК-триггеры – универсальные триггеры с раздельной установкой состояний 0 и 1.

Обозначение входов триггеров:

S(Set- установить) – вход установки триггера в 1;

R(Reset- сбросить) – вход установки триггера в 0;

Т– счетный вход триггера (вход Т-триггера);

D(Delay- задкржка)– информационный входD-триггера для установки в 0 или 1;

С– вход синхронизации (командный вход, управляющий приемом информации);

J– вход для синхронизируемой (в момент прихода тактирующего импульса) установки состояния 1 вJК-триггере;

К– вход для синхронизируемой установки состояния 0 вJК-триггере;

V(E) – вход разрешающий изменения состояния триггера.

Выходы триггера

обозначаются: Q– прямой выход,![]() – инверсный выход (на схемах обозначается

окружностью). Состояние триггера

определяется сигналом на выходеQ:

приQ= 0 (

– инверсный выход (на схемах обозначается

окружностью). Состояние триггера

определяется сигналом на выходеQ:

приQ= 0 (![]() = 1) триггер находится в состоянии 0 и

устанавливается это состояние подачей

сигнала на входR. ПриQ= 1 (

= 1) триггер находится в состоянии 0 и

устанавливается это состояние подачей

сигнала на входR. ПриQ= 1 (![]() = 0) триггер находится в состоянии 1.

= 0) триггер находится в состоянии 1.

По способу записи информации триггеры подразделяются на асинхронные и синхронные:

- асинхронные триггеры допускают воздействие сигналов установки в произвольные моменты времени;

- в синхронных триггерах изменение информации происходит только при подачи сигнала на вход синхронизации.

Входы триггеров могут реагировать или на наличие потенциала или на его изменение (передний или задний фронт импульса). В первом случае входы называются статическими, а во втором – динамическими входами.

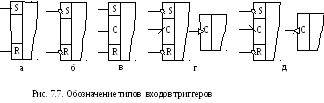

На рис. 7.7. показано условное графическое обозначение типов входов триггеров. Рис. 7.7 а, б – асинхронные триггеры со статическими входами: а – установочные входы реагируют на потенциал логической единицы; б – логического нуля. Рис. 7.7 в - синхронный триггер со статическими входами. На рис. 7.7 г, д показано условное обозначение динамического входа синхронизации С: г – вход С реагирует на передний фронт импульса; д - вход С реагирует на задний фронт импульса.

7.3.2.RS-триггеры

RS-триггеры бывают асинхронные и синхронные.

а) Асинхронные

RS-триггеры

представлены на рис.7.8 а,б. Состоят

асинхронные триггеры из двух элементовИ-НЕилиИЛИ-НЕ, охваченных

перекрестными обратными связями. Если

один элемент находится в состоянии 0,

то другой в состоянии 1. Для ориентации

триггера в одно из двух состояний для

схемы, показанной на рис.7.8 а, сигналы

на входRиSдолжны воздействовать раздельно в виде

логических единиц. Одновременная подача

наRиSвходы сигналов установкиR=S=1запрещена. В схеме, показанной на рис.

7.8 б, триггер устанавливается в состояние

1 сигналом![]() =0,

а в состоянииQ=0– сигналом

=0,

а в состоянииQ=0– сигналом

![]() =0.

Запрещенной является комбинация

=0.

Запрещенной является комбинация![]() .

.

Состояние триггера можно описать или аналитически или задать с помощью таблицы истинности (таблица 7.3).

-

Таблица 7.3

Q

0

0

ЗК

0

1

1

1

0

0

1

1

Q*

Q* -режим хранения.

ЗК – запрещенная комбинация.

б) Синхронный RS-триггер – это асинхронныйRS-триггер, дополненный еще двумя элементамиИ-НЕ(ИЛИ-НЕ), на общий вход которых (входС) подается сигнал синхронизации. При отсутствии сигнала наС-входе триггер не воспринимаетR- иS-сигналы.

В схеме, показанной

на рис.7.9, если на С-вход действует

1, то приS=1иR=0триггер

устанавливается в состояние 1, а приS=0иR=1триггер устанавливается в 0.

Аналогично работает триггер, показанный

на рис.7.9 б. Допустим, он установлен в

положениеQ = 1. На вход![]() подан сигнал логический 0. В этом случае

при подаче тактирующего импульса на

входСверхняя схемаИЛИ-НЕсформирует на своем выходе сигнал 1,

который установит триггер в состояниеQ = 0,

подан сигнал логический 0. В этом случае

при подаче тактирующего импульса на

входСверхняя схемаИЛИ-НЕсформирует на своем выходе сигнал 1,

который установит триггер в состояниеQ = 0,![]() = 1.

= 1.

7.3.3. D-триггеры (триггеры задержки)

D-триггеры – триггеры с задержкой смены состояний. Их название происходит от английскогоDelay(задержка).

Синхронные D-триггеры, показанные на рис.7.10, имеют два входа:D-вход – для приема информационного сигнала иС-вход – для сигналов синхронизации, управляющих задержкой информационного сигнала (разрешающих смену состояния триггера).

Синхронные D-триггеры состоят из четырех элементовИ-НЕ(ИЛИ-НЕ). ЭлементыDD3,DD4представляютRS-триггер. Входы элементовDD1,DD2подключены кR- иS-входамRS-триггера.

При наличии сигнала синхронизации С = 1инвертированный информационныйD-сигнал воздействует на входDDЗ(S-входRS-триггера), а неинвертированный – с выходаDDЗна входDD4(наR-входRS-триггера).

П

__ Q & & E DD2 DD4 Рис.17.13.СинхронныеD-триггеры: а

– на элементах И-НЕ; б – на элементах

ИЛИ-НЕ; в – условное обозначение; г –D-триггер с дополнительным

управляющим входом Е

В технике находят применение синхронные D-триггеры с динамическим входом синхронизации С и асинхронными установочными входамиSиR(например, К155ТМ2 – дваD-триггера в одном корпусе). Причем установочные входы, предназначенные для исходной установки триггера, имеют наивысший приоритет. На рис 7.11 а приведено функциональное обозначение одного из триггеров К155ТМ2, а на рис .7.11 б – временная диаграмма его работы при условии, что в момент времениt0 триггер был сброшен. Таблица 7.4 описывает поведениеD-триггера.

-

Таблица 7.4

D

C

Q

0

0

х

х

ЗК

0

1

х

х

0

1

0

х

х

1

1

1

0

/

0

1

1

1

/

1

1

1

x

–

Q*

7.3.4.Универсальные JК-триггеры

Они строятся на основе RS-триггеров. Логика их управления обеспечивает широкие возможности по смене состояний и блокировке сигналов запуска. Независимо от действия других сигналов ориентация их в состояния 0 и 1 осуществляется поR- иS-входам.

По J- иК-входам, имеющим расширение по 3И, триггер соответственно устанавливается в состояние 1 или 0, но при наличии синхросигнала наС(Т)-входе. В отличие отRS-триггера сигналы наJ- иК-входы могут действовать одновременно, меняя при этом состояние триггера на противоположное тому, какое было до воздействия этих сигналов: то естьJК-триггер будет работать в счетном режиме.

Если на J- иК-входы подана 1, то поС(Т) – входу он работает как счетный триггер (работа в счетном режиме). Если наJ- иК-входы подан 0, то действие входных сигналов на триггер блокировано(режим хранения). На рис. 7.12 а и б приведено соответственно функциональное обозначениеJK-триггера (К155ТВ1) и его работа в счетном режиме. Таблица 7.5 описывает поведениеJK-триггера.

-

Таблица7.5

J

K

C

Q

0

0

х

х

х

ЗК

0

1

х

х

х

0

1

0

х

х

х

1

1

1

0

0

\

Q*

1

1

0

1

\

0

1

1

1

0

\

1

1

1

1

1

\

![]() -инверсия предыдущего

состояния (работа в счетном режиме).

-инверсия предыдущего

состояния (работа в счетном режиме).

7.3.5. Счетные Т-триггеры

Т-триггеры имеют два входа – вход синхронизации С и собственно счетный вход Т. Счетные триггеры меняют свое состояние на противоположное с приходом на Т-вход каждого сигнала синхронизации. Они состоят из синхронныхRS- илиD-триггеров и различных сочетаний логических элементов.

На рис.7.13 показан

Т-триггер на основе схемыD-триггера

с динамической синхронизацией. Для

этого![]() -выход

триггера соединяют сD-входом, а наС-вход синхронизации подают импульсы,

используя его как счетный вход. Пусть

в исходном состоянии выходные сигналыQ=0,

-выход

триггера соединяют сD-входом, а наС-вход синхронизации подают импульсы,

используя его как счетный вход. Пусть

в исходном состоянии выходные сигналыQ=0,![]() =1.

Следовательно, сигнал на входеDбудетD=1. При первом же перепаде

напряжений 0,1 на входе синхронизацииСтриггер примет состояниеQ=1. При

этом потенциалы на выходе

=1.

Следовательно, сигнал на входеDбудетD=1. При первом же перепаде

напряжений 0,1 на входе синхронизацииСтриггер примет состояниеQ=1. При

этом потенциалы на выходе![]() и на входеDстанут

и на входеDстанут![]() =D=0.

Переключение триггера происходит в

течение очень короткого времени. Поэтому

изменение сигнала на входеDс

небольшой задержкой относительно

момента срабатывания триггера не меняет

его состояния. Следующий перепад

напряжения 0,1 установит триггер в

состояниеQ=0,

=D=0.

Переключение триггера происходит в

течение очень короткого времени. Поэтому

изменение сигнала на входеDс

небольшой задержкой относительно

момента срабатывания триггера не меняет

его состояния. Следующий перепад

напряжения 0,1 установит триггер в

состояниеQ=0,

![]() =1.

Потенциал наD-входе станетD=1.

Таким образом, состояние триггера

меняется на противоположное при каждом

перепаде напряжения на входе синхронизации.

Т

=1.

Потенциал наD-входе станетD=1.

Таким образом, состояние триггера

меняется на противоположное при каждом

перепаде напряжения на входе синхронизации.

Т -триггеры

обычно используются для изготовления

счетчиков импульсов в интегральном

исполнении.

-триггеры

обычно используются для изготовления

счетчиков импульсов в интегральном

исполнении.

Лекция 8. Системы счисления. Счетчики импульсов. Микроконтроллеры: принципы организации микропроцессоров; архитектура микропроцессоров и их функционирование, структура микроконтроллеров.

8.1 Системы счисления

В цифровой и вычислительной технике сигналы и информация представляются в дискретной форме. Для удобства последующего преобразования дискретный сигнал подвергается кодированию. Большинство кодов основано на системах счисления, причем использующих позиционный принцип образования числа, при котором значение каждой цифры зависит от ее положения (позиции, веса) в числе.

Примером позиционной формы записи чисел является та, которой мы пользуемся (так называемая арабская форма чисел). Так, в числах 123 и 321 значения цифры 3, например, определяются ее положением в числе: в первом случае она обозначает три единицы (т.е. просто три), а во втором – три сотни (т.е. триста).

В современной информатике используются в основном три системы счисления (все – позиционные): двоичная, шестнадцатеричная и десятичная.

Двоичная система счисления используется для кодирования дискретного сигнала, потребителем которого является вычислительная техника. Такое положение дел сложилось исторически, поскольку двоичный сигнал проще представлять на аппаратном уровне. В этой системе счисления для представления числа применяются два знака – 0 и 1.

Шестнадцатеричная система счисления используется для кодирования дискретного сигнала, потребителем которого является хорошо подготовленный пользователь – специалист в области информатики. В такой форме представляется содержимое любого файла, затребованное через интегрированные оболочки операционной системы, например, средствами Norton Commander в случае MS DOS. Используемые знаки для представления числа – десятичные цифры от 0 до 9 и буквы латинского алфавита – A, B, C, D, E, F.

Десятичная система счисления используется для кодирования дискретного сигнала, потребителем которого является так называемый конечный пользователь – неспециалист в области информатики (очевидно, что и любой человек может выступать в роли такого потребителя). Используемые знаки для представления числа – цифры от 0 до 9.

В любой позиционной системе счисления число можно представить в виде полинома вида

N = a n-1 b n-1 + a n-2 b n-2 +…. + + a 0 b 0 , a m b m + a m-1 b m -1 + a m-i b m –I , (8.1)

где n– количество разрядов целой части числа,

где m– количество разрядов дробной части числа,

b– основание системы счисления,

ai – множитель, принимающий любые целочисленные значения от 0 до b-1, и соответствующий цифре i-го порядка числа.

Двоичная система счисления - число представляется совокупностью цифр 0 и 1, которые называются битами (binarydigits– двоичные цифры). Основание системы счисленияb= 2.

Шестнадцатеричная система счисления – для записи чисел используют цифры от 0 до 9 и буквы латинского алфавитаA(10),B(11),C(12),D(13),E(14),F(15).

Перевод из десятичной системы счисления в двоичную и шестнадцатеричную:

Для перевода чисел из одной системы счисления в другую используют метод деления (целая часть числа) – умножения (дробная часть числа) на основание системы счисления.

Перевод целой части числа:

а) исходное целое число делится на основание системы счисления, в которую переводится (на 2 - при переводе в двоичную систему счисления или на 16 - при переводе в шестнадцатеричную); получается частное и остаток;

б) если полученное частное меньше основания системы счисления, в которую выполняется перевод, процесс деления прекращается, переходят к шагу в). Иначе над частным выполняют действия, описанные в шаге а);

в) все полученные остатки и последнее частное преобразуются в соответствии с таблицей перевода в цифры той системы счисления, в которую выполняется перевод;

г) формируется результирующее число: его старший разряд – полученное последнее частное, каждый последующий младший разряд образуется из полученных остатков от деления, начиная с последнего и кончая первым. Таким образом, младший разряд полученного числа – первый остаток от деления, а старший – последнее частное.

Выполнить перевод числа 19 в двоичную систему счисления:

|

|

частное |

остаток |

|

19 : 2 = |

9 |

1 -младший бит |

|

9 : 2 = |

4 |

1 |

|

4 : 2 = |

2 |

0 |

|

2 : 2 = |

1 |

0 |

|

1: 2 = |

0 |

1 -старший бит |

|

|

|

|

Выполнить перевод числа 173 в шестнадцатеричную систему счисления:

|

|

частное |

остаток |

|

173 :16= |

10 |

D (13)-младший бит |

|

10:16= |

0 |

A (10)-старший бит |

Перевод дробной части числаиз десятичной системы в любую другую позиционную систему счисления.

При переводе правильной десятичной дроби в систему счисления с основанием bнеобходимо сначала саму дробь, а затем дробные части всех последующих произведений последовательно умножать наb, отделяя после каждого умножения целую часть произведения. Число в новой системе счисления записывается как последовательность полученных целых частей произведения. Умножение производится до тех поp, пока дробная часть произведения не станет равной нулю. Это значит, что сделан точный перевод. В противном случае перевод осуществляется до заданной точности. Достаточно того количества цифр в результате, которое поместится в ячейку.

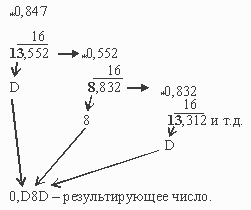

Пример. Выполнить перевод числа 0,847 в двоичную систему счисления. Перевод выполнить до четырех значащих цифр после запятой.

Имеем:

Пример. Выполнить перевод числа 0,847 в шестнадцатеричную систему счисления. Перевод выполнить до трех значащих цифр.

Для различения систем счисления, в которых представлены числа, в обозначение двоичных и шестнадцатеричных чисел вводят дополнительные реквизиты:

для двоичных чисел – нижний индекс справа от числа в виде цифры 2 либо знак B или b (binary – двоичный), справа от числа. Например, 1010002= 101000B= 101000b;

для шестнадцатеричных чисел - нижний индекс справа от числа в виде числа 16 либо знак H или h (hexadecimal – шестнадцатеричный), справа от числа. Например, 3AB16= 3ABH = 3ABh.

Перевод из двоичной или шестнадцатеричной систем счисления в десятичную выполняется по соотношению (8.1).

Группа из 8 битов информации называется байтом. Если бит — минимальная единица информации, то байт ее основная единица. Существуют производные единицы информации: килобайт (кбайт, кб), мегабайт (Мбайт, Мб) и гигабайт (Гбайт, Гб).

1 кб =1024 байта.

1 Мб = 1024 кбайта = 1024 x 1024 байтов.

1 Гб = 1024 Мбайта = 1024х1024 х 1024 байтов.

Эти единицы чаще всего используют для указания объема памяти ЭВМ.

8.2. Счетчики импульсов

Счетчик – это последовательная схема, в основе которой лежит регистр (последовательное соединение триггеров). Поскольку любая последовательная схема имеет конечное число состояний, то счетная последовательность счетчика либо завершается неким определенным состоянием (счетчики с конечным состоянием или счетчики с насыщением), либо циклически повторяется – счетчики по модулю (mod). Термин модуль используется для обозначения числа различных состояний счетной последовательности. Например, в счетчике поmod= 6 после прихода на вход шестого импульса счетчик обнуляется и процесс счета повторяется снова. Если в счетчикеnтриггеров, то число возможных состояний счетчика равно 2n и следовательно его модуль равенmod= 2n.

Счетчики строятся на базе синхронных триггеров (D,T). В зависимости от способа соединения синхронизирующих входов триггеров, двоичные счетчики подразделяются на синхронные и асинхронные.

В зависимости от модуля они подразделяются на десятичные (декадные), у которых

mod= 10 и двоичные сmod= 2n.

В зависимости от направления счета они подразделяются на суммирующие, вычитающие или реверсивные (направление счета можно менять).

Синхронные счетчики. Функциональная схема синхронного двоичного счетчика на базе Т-триггеров и временная диаграмма его работы представлены на рис. 8.1.

Так как в счетчике общая синхронизация, то состояние триггеров меняется синхронно, т. е. те триггеры, которые должны изменить своё состояние по синхроимпульсу, делают это синхронно. В частности, если в момент времени t0все триггеры исходно обнулены, то после подачи на линию «разрешение счета» сигнала Т = 1 в единичном состоянии будет только первый триггер (Q0 =1) после прихода импульса синхронизации. Все остальные – в нулевом, так как через схемы И их входы Т блокированы нулевым потенциалом. С приходом второго тактового импульса к изменению своего состояния на единичное будет подготовлен второй триггер и по заднему фронту второго импульса синхронизации триггеры примут новое состояние:Q0 = 0,Q1 = 1,Q2 = 0.

Число импульсов, пришедших на вход счетчика, можно определить по соотношению:

N=Q0 20 +Q1 21 +Q2 22 + … +Qn -1 2n -1 (8.2).

Описанный выше способ формирования сигналов на Т входов триггеров используется в счетчиках с последовательным переносом. Применение вентилей И для формирования сигналов на входах Т приводит к снижению скорости счета, так как после прохождения синхроимпульса следующий нельзя подавать до тех пор, пока не определятся все значения на входах Т. Для n-разрядного счетчика требуется времяtзад = τв (n– 1), где τв – время задержки распространения сигнала через один вентиль.

Этот недостаток устраняется в счетчиках со сквозным переносом за счет усложнения схемы подачи сигналов на Т входы триггеров.

Асинхронные счетчики.

В асинхронных счетчиках входы синхронизации триггеров, кроме первого, соединены с выходами предыдущих триггеров (рис. 8.2), а входы Т объединены в общую линию «разрешение счета», поэтому состояние триггера меняется в ответ на изменение состояния предыдущего.

Е

а DD3 сли

на линию «разрешение счета» подана

логическая 1, то каждое «отрицательное»

изменение состояния каждого левого

триггера (задний фронт импульса) вызовет

изменение состояния последующего и

т.д. В асинхронных счетчиках возможен

сбой в процессе передачи информации от

триггера к триггеру. Они находят широкое

применение в качестве делителей частоты

на любую степень двойкиfвых

=fвх/ 2n

.

сли

на линию «разрешение счета» подана

логическая 1, то каждое «отрицательное»

изменение состояния каждого левого

триггера (задний фронт импульса) вызовет

изменение состояния последующего и

т.д. В асинхронных счетчиках возможен

сбой в процессе передачи информации от

триггера к триггеру. Они находят широкое

применение в качестве делителей частоты

на любую степень двойкиfвых

=fвх/ 2n

.

Все рассмотренные

счетчики являются суммирующими двоичными

счетчиками. Они легко могут быть

перестроены в вычитающие. Для этого,

например, в схеме рис. 8.1 достаточно

переключить входы вентилей И с выходов

Qна инверсные![]() .

.

8.3. Микроконтроллеры.

8.3.1. Принципы организации микроконтроллеров; архитектура микропроцессоров и их функционирование, структура микроконтроллеров.

В современной технике микроконтроллеры находят очень широкое применение. На их основе строятся датчики измерения физических параметров с линейными характеристиками, регуляторы параметров технологических процессов, системы сбора и передачи данных, информационные системы и системы автоматического управления различного класса. Современное понятие микроконтроллер возникло в связи с мощным развитием и совершенствованием микроэлектроники и является естественным развитием более старых понятий, таких как ЭВМ, микро-ЭВМ, употреблявшихся в 70 – 80 годы прошлого столетия. Однако основные, базовые принципы организации функционирования вычислительных систем остаются.

По определению ЭВМ – это искусственная, инженерная система, предназначенная для выполнения вычислений на основе алгоритмов. Принципы ее построения определяются с одной стороны, назначением ЭВМ, а с другой – элементной базой. Совершенствование элементной базы и привело к появлению в конце 20 века такого понятия как микроконтроллер.Современная вычислительная техника строится на одном из важных принципов –принципе программного управления, предложенного Дж. Фон Нейманом в 1945 г. Эти принципы следующие:

1. Информация кодируется в двоичной форме и разделяется на единицы информации, называемые словами.

2. Разнотипные слова информации различаются по способу использования, но не способом кодирования. Все слова, представляющие числа, команды и т.д. выглядят в ЭВМ совершенно одинаково и сами по себе неразличимы. Только порядок использования слов в программе вносит различия в слова. Благодаря этому возможно использовать одни и те же операции для обработки и чисел и команд.

3. Слова информации размещаются в ячейках памяти и идентифицируются номерами ячеек, называемых адресами слов.

4. Алгоритм представляется в форме последовательности управляющих слов, которые определяют наименование операции и слова информации, участвующие в операции, и называются командами.

5. Выполнение вычислений, предписанных алгоритмом, сводится к последовательному выполнению команд в порядке, определяемом программой.

Принцип программного управления предполагает, что алгоритм в ЭВМ представляется в виде упорядоченной последовательности команд вида

b0 b1 ...bl b0 b1 ...bm … b0 b1 ...bn ,

где b– двоичная переменная. Определенное число первых разрядов команды характеризует код операции (КОП) – характер выполняемых действий (+, -, * ,и т.д.). Последуюшие наборы двоичных переменных (А1 …Аn ) определяют адреса операндов (аргументов и результатов), заданных кодом КОП. Процесс вычислений, выполняемый по заданной программе, состоит в последовательном выполнении команд. Первой выполняется команда, заданная пусковым адресом программы. Обычно это адрес первой команды программы.

В состав современного микроконтроллера входят: ядро (микропроцессор); память данных (оперативное запоминающее устройство - ОЗУ (RAM)); память программ (постоянное запоминающее устройство – ПЗУ (ROM) илиFlash-память); периферийные устройства: контроллеры прерываний, порты ввода-вывода, ШИМ- генераторы, таймеры, АЦП, ЦАП, порты для последовательной передачи данных –USART,I2C,SPIи т.д. Все эти устройства выполняются, как правило, на одном кристалле и помещаются в одном корпусе.

8.3.2. Архитектура микропроцессоров и их функционирование.

Основным элементом микроконтроллера является микропроцессор (МП). Первый коммерческий микропроцессор Intel-8080 был разработан фирмойIntelв 1975 г. Микропроцессор – это функциональный блок, предназначенный для логической и арифметической обработки информации на основе принципа программного управления. Современные микропроцессоры выполняются, как правило, по КМОП технологии и содержат десятки и сотни тысяч элементов, имеют высокое быстродействие – от 10Mips(миллионов операций в секунду) и более, 8, 16 или 32 –разрядную шину данных, 18, 24-разрядную и более шину адреса (речь идет о микропроцессорах для промышленного применения).

В настоящее время основными являются две архитектуры микропроцессоров - неймановская, основанная на принципах, сформулированных фон Нейманом и Гарвардская архитектура. Неймановская архитектура предполагает, что память в системе линейна, т. е. безразлично, в каких областях располагается ОЗУ и ПЗУ. Гарвардская архитектура предлагает жесткое разделение информации на команды и данные и поэтому в архитектуре предусмотрено хранение команд в памяти команд, а операндов – памяти данных.

Из-за сложности схемы, пользователю программно-доступны только основные регистры управления микропроцессором. Рассмотрим архитектуру неймановского процессора с позиций, предоставленных пользователю (рис.8.3).

С периферийными устройствами МП связан с помощью системы шин: ExternalDataBus-двунаправленнаяn-разрядная внешняя шина данных;ExternalAddressBus- однонаправленнаяm-разрядная внешняя шина адреса;ControlBusоднонаправленнаяk-разрядная шина управления (одни разряды шины работают только на ввод, другие – только на вывод). Все шины с тремя состояниями.

Основными устройствами МП являются:

1. АЛУ– арифметико логическое устройство; предназначено для выполнения арифметических (+, -, *, / ) и логических операций (И, ИЛИ, НЕ, Исключающее ИЛИ, операции сдвига). В состав АЛУ входятn-разрядные сумматоры, аппаратные умножители и схемы деления. АЛУ связано с регистром признаков FR(FlagsRegister).

2. В регистре признаков фиксируются результаты операций (при выполнении того или иного условия автоматически взводится определенный бит регистра):

Z (Zero) – нулевой результат операции; устанавливается, если результатом выполнения последней операции в АЛУ является ноль;

S (Sing) или N (Negative) – флаг отрицательного знака при выполнении операции (устанавливается если при выполнении операции в АЛУ получается отрицательное число);

C (Carry) – флаг переноса; устанавливается, если при выполнении операции в АЛУ был установлен бит переноса;

V – флаг переполнения; устанавливается, если при выполнении операции в АЛУ имело место переполнение.

3. GPR (General Pupas Registers)–регистры общего назначения. Предназначены для временного хранения информации, располагаются, как правило, во внутреннем ОЗУ процессора и имеют минимальное время доступа.

SP (Stack Pointer) – указатель стека; это регистр, который содержит адрес ячейки памяти, являющейся вершиной стековой памяти. Стековая память, как правило, создается в оперативной памяти и предназначена для временного хранения информации, в частности при выполнении некоторых команд, например, вызова подпрограмм, возврата из подпрограмм, обработки прерывании и т.д.

PC (Program counter) – программный счетчик, счетчик команд; содержит адрес ячейки памяти, из которой выбирается следующая команда. Во время выборки команды содержимое счетчика передается в регистр адресаRA и из него через буферную схему поступает на внешнюю шину адреса. С помощью схемы приращенияСхП содержимое счетчика команд увеличивается на 1 или 2 в зависимости от длины слова, с которым обменивается процессор (один или два байта) для указания адреса следующей команды.

IR (Instruction Register) – первое слово команды, выбранное из программной памяти, передается через буфер данных и внутреннюю шину данных вIR, выход которого связан с дешифратором команд и формирователем машинных цикловDCи ФМЦ, который по КОП в команде определяет тип выполняемой операции.

Устройство управления и синхронизации (УУС) – вырабатывает управляющие и синхронизирующие сигналы, необходимые для выполнения принятой и дешифрированной команды, подключая необходимые устройства процессора. С помощьюk-внешних линий управления (ControlBus) реализуется интерфейс процессора с другими модулями микроконтроллера. Некоторые из этих сигналов:

FCLK - тактовая частота процессора; синхронизирует работу всех устройств и определяет время выполнения команд (быстродействие МП).

RESET – выходной сигнал сброса; обнуляет все основные регистры процессора, в том числе программного счетчикаРС, указывая при старте на ячейку памяти 0000h, из которой должна быть считана первая команда программы.

WR (Write) – запись в память, внешнее устройство;

RD (Read) –чтение из памяти, из внешнего устройства.

Современные процессоры выполняются по RISC(ReduceInstructionSetComputering) архитектуре (выполнение вычислений по минимизированным командам). Это обеспечивает выполнение большинства команд за очень малое время даже при относительно не высоких тактовых частотах процессора. Например, МПSAB80C167 фирмыSiemensпри тактовой частоте 20 МГц выполняет большинство команд за 100 нс.

8.3.3. Структура микроконтроллеров

В качестве примера ниже дано краткое описание промышленного микроконтроллера М167-2.

Промышленный контроллер М167-2, структурная схема которого приведена на рис.8.4., разработан на базе микроконтроллера Siemens80С167, ядром которого является 16-разрядныйRISCпроцессорSAB80C167 [1]. В основу работы процессора положена конвейерная организация выполнения команд, благодаря чему для выполнения большинства из них требуется 100 наносекунд при тактовой частоте процессора 20 МГц.

Центральное процессорное устройство имеет фон-Неймановскую архитектуру, что обеспечивает доступ к исполняемому коду в пределах единого линейного адресного пространства. Максимальный размер адресуемой памяти составляет 16 Мбайт, которая разделена на 256 сегментов (CodeSegment) по 64 Кбайт в каждом. Каждый сегмент состоит из четырех страниц данных (DataPage) размером по 16 Кбайт.

Процессор имеет внутреннее ОЗУ объемом 2 Кбайт (1Кх16), расположенное в третьей странице данных нулевого сегмента (00.F000h– 00.FFFFh).Во внутреннем ОЗУ размещены регистры общего (GPR) и специального (SFRиESFR) назначения.

Система обработки прерываний контроллера обрабатывает более 56 независимых каналов прерываний. Текущее состояние программы (IP,PSW,CSP) сохраняется во внутреннем системном стеке. Шестнадцати уровневая система приоритетов с четырех уровневым (групповым) приоритетом второго уровня позволяет организовать обработку прерываний по приоритету. Кроме того, в состав контроллера входит 8 канальный блок РЕС (событийный контроллер), с помощью которого можно осуществлять пересылку данных между периферийными устройствами и областями памяти в режиме прерываний без участия основного процессора.

Контроллер внешней шины позволяет задать четыре типа внешней шины и изменять их временные характеристики.

Входящие в состав контроллера блоки «Захват/Сравнение» и блоки таймеров позволяют организовать дополнительные ШИМ каналы (до 28) кроме стандартного четырех канального модуля ШИМ, а так же формировать и измерять параметры импульсных сигналов.

Микроконтроллер обеспечивает 111 параллельных каналов ввода/вывода, организованных в 16- или 8-битовые порты. Все выводы портов битадресуемы и индивидуально (побитно) программируются на ввод или вывод.

Кроме того, в состав микроконтроллера входят два АЦП (8 и 16 каналов) и сетевой контроллер CANсо скоростью передачи до 1 Мбит/сек.CANконтроллер позволяет создавать сложные распределенные системы управления реального времени.

Наличие встроенного полноэкранного отладчика обеспечивает режим интерактивного доступа ко всем ресурсам микроконтроллера и удобный интерфейс для отладки программ, что позволяет быстро и эффективно отлаживать программы в реальном времени с подключенными внешними устройствами. С помощью специальных функций отладчика и программатора, находящегося на плате контроллера, программа после окончания разработки и отладки может быть записана во FlashПЗУ.