- •Кафедра электротехники, электроснабжения, автоматики и информационных технологий

- •1.1. Элементы зонной теории твердого тела.

- •1.2. Полупроводники p- иn- типов

- •1.3. Полупроводниковый p-n–переход

- •1.5. Классификация полупроводниковых диодов

- •Диффузионные диоды получают за счет диффузии в полупроводниковую пластину примеси, находящейся в газообразной, жидкой или твердой фазах.

- •1. 6. Выпрямительные диоды

- •2.3. Биполярные транзисторы

- •2.4. Полевой транзистор

- •Раздел 2. Источники вторичного электропитания

- •Раздел 3. Электронные и импульсные устройства.

- •5.4.Операционные усилители (оу): базовые схемы включения операционных усилителей; амплитудно-частотная характеристика (ачх) оу; компараторы на оу.

- •Раздел 4. Основы цифровой и микропроцессорной техники

- •7.1. Логические функции. Описание логических функций с помощью таблиц истинности. Базовые логические функции.

- •7.2. Логические вентили ттл, ттлш, моп и кмоп структур; вентили с тремя состояниями.

- •7.3. Триггеры на логических элементах

7.2. Логические вентили ттл, ттлш, моп и кмоп структур; вентили с тремя состояниями.

Схемы, реализующие логические функции, называются логическими элементами (ЛЭ) или логическими вентилями.

По типу сигналов логические элементы делятся на статические, импульсные и фазовые.

В статическихэлементах выходные сигналы, соответствующие двоичным кодам, представляются в виде статических сигналов. Под статическим понимается сигнал, который после завершения переходных процессов принимает постоянное значение. При устойчивом состоянии элемента такой сигнал удерживается на его выходе неограниченно долго.

Импульсные элементы выдают сигналы в виде импульсов напряжения или тока. Сигналы кодов «1» и «0» на выходах импульсных элементов могут представляться либо одиночными импульсами, либо сериями импульсов (динамичное представление), причем наличие импульса соответствует «1»; отсутствие – «0».

В фазовыхэлементах кодовые сигналы в выходных цепях представляются электрическими колебаниями, отличающимися по фазе.

В логических схемах логические нули и единицы представляют разными значениями напряжения: уровнем нуля – U0или уровнем единицы – U1. Если U1> U0, то схема работает в “положительной логике”, если наоборот – в “отрицательной логике”

Разность уровней U= U1– U0называетсялогическим перепадом. Чем больше логический перепад, тем выше помехоустойчивость.

Логические элементы выпускаются в виде логических полных серий ИМС, включающих базовые элементы и другие схемы, расширяющие возможности построения и облегчающие композицию сложных цифровых устройств различного назначения. Базовыми являются элементы Шеффера (И – НЕ) и Пирса (ИЛИ – НЕ), обладающие свойствами обратимости. Для данной логической серии все ИМС имеют одинаковое напряжение питания и согласованы по входу и выходу, то есть логические 0 и 1 на их входах и выходах представляются физически одинаково. Это позволяет соединить ИМС друг с другом непосредственно.

7.2.1.Типы логических интегральных схем (ИС)

Схемные варианты интегральных логических элементов называются транзисторными логиками(ТЛ). В настоящее время наибольшее распространение получили следующие базовые логические элементы:

ТТЛ – транзисторно–транзисторная логика;

ТТЛШ - транзисторно–транзисторная логика с диодами Шоттки;

МОП логика – логика на полевых транзисторах с изолированным затвором с каналом n-типа;

КМОП логика – комплементарная логика (на полевых транзисторах с изолированным затвором с каналом n- и р-типа;

Параметры логических ИС

Чем более резким является переход от максимального к минимальному (и наоборот) уровню напряжения, тем выше качество логических ИС.

а) Статистические параметры логических ИС:

Uип– напряжение источника питания;

(U0вх) и (U0вых) – входное и выходное напряжения логического нуля;

(U1вх) и (U1вых) – входное и выходное напряжения логической единицы;

(I0вх, I1вх) и (I0вых, I1вых) – токи логического нуля и логической единицы;

Краз– коэффициент разветвления по выходу;

Коб– коэффициент объединения по входу (число входов, по которым реализуется логическая функция);

Uп– допустимое напряжение статистической помехи (с длительностью, большей времени переключения схемы);

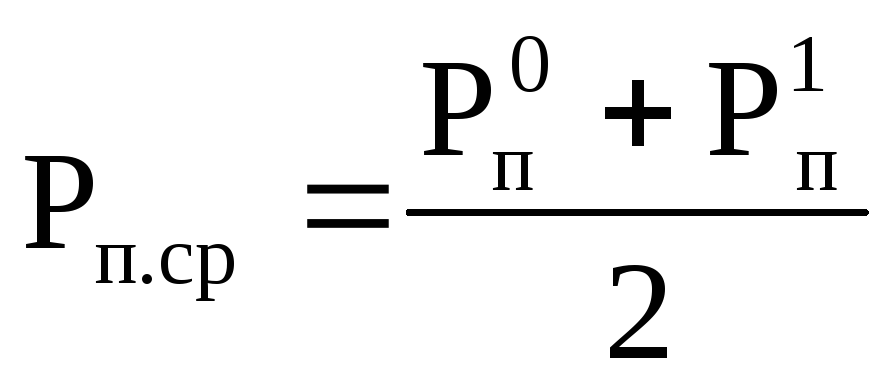

–средняя

потребляемая мощность.

–средняя

потребляемая мощность.

б) Динамические параметры (характеризуют свойства ИС в режиме переключения):

- время перехода из состояния логического нуля в состояние логической единицы;

- время задержки распространения сигнала при выключении ИС;

- время перехода из состояния логической единицы в состояние логического нуля;

- время задержки распространения сигнала при включении ИС;

-

– среднее время задержки распространения

сигнала

– среднее время задержки распространения

сигнала

(t3= 10…300 нс).

7.2.2. Транзисторно-транзисторная логика

Основой транзисторно-транзисторной логики (ТТЛ) являются биполярные транзисторы. На рис. 7.2,а показана принципиальная схемаn-входового типового логического элемента транзисторно-транзисторной логики серии К155.Многоэмиттерный транзистор VT1 образует n-входовую цепь Ии выступает в роликомбинатора. В случае присоединения хотя бы одного эмиттера этого транзистора к потенциалу, близкому к нулю, транзистор насыщается током от источника питания и присоединяет к нулевому потенциалу коллектораVT1вход инвертора (базуVT2). Если же на все входы (эмиттеры) цепиИподан потенциал, близкий к напряжению питания (потенциал лог1), то базо-коллекторный переход многоэмиттерного транзистораVT1окажется смещенным в прямом направлении. Этот переход открывается, и ток из базовой цепи транзистораVT1поступает на вход инвертора (на базуVT2).

Таким

образом,транзистор VT2

с нагрузочным резистором R2

выполняет функцию инвертора НЕ. ЦепьR3,R4,VT3служит для

нелинейной коррекции инвертора,

увеличивая быстродействие и улучшая

его формирующие свойства. Выходные

сигналы инвертора усиливаются двухтактным

выходным усилителем на транзисторахVT4иVT5,

резистореR5и

диодеVDn.

При этом если на выходе инвертора будет

напряжениеU1(VT2заперт), будет запертVT5и насыщенVT4. Если

на выходе инвертора будет напряжениеU0(VT2насыщен), будет насыщенVT5и запертVT4.

Таким

образом,транзистор VT2

с нагрузочным резистором R2

выполняет функцию инвертора НЕ. ЦепьR3,R4,VT3служит для

нелинейной коррекции инвертора,

увеличивая быстродействие и улучшая

его формирующие свойства. Выходные

сигналы инвертора усиливаются двухтактным

выходным усилителем на транзисторахVT4иVT5,

резистореR5и

диодеVDn.

При этом если на выходе инвертора будет

напряжениеU1(VT2заперт), будет запертVT5и насыщенVT4. Если

на выходе инвертора будет напряжениеU0(VT2насыщен), будет насыщенVT5и запертVT4.

Во

входной цепи многоэмиттерного транзистора

VT1включены

дополнительные диодыVD0–VDn-1,

защищающие элемент от появления на его

входе недопустимых напряжений обратной

полярности. Учитывая обозначения,

приведенные на рис.17.2,а можно записать

функцию, реализуемую логическим

элементом, в видеу=![]() ,

то есть функциюИ-НЕ.

,

то есть функциюИ-НЕ.

Для расширения функциональных возможностей применяются элементы И-НЕ с открытым коллектором.В схеме такого элемента, приведенной на рис. 7.3, выходной усилитель мощности выполнен по однотактной схеме без нагрузочного резистора.

Э лемент

может согласовывать логические схемы

с внешними исполнительными и индикаторными

устройствами, например обмотками реле

или светодиодными индикаторами

подключение нагрузки к напряжению до

30В.

лемент

может согласовывать логические схемы

с внешними исполнительными и индикаторными

устройствами, например обмотками реле

или светодиодными индикаторами

подключение нагрузки к напряжению до

30В.

ТТЛэлементы имеют сравнительно высокое быстродействие (10 -15 МГц), малые входные и большие выходные токи.

Они хорошо работают на емкостную нагрузку, так как перезарядка конденсаторов осуществляется через низкоомную выходную цепь. Основные параметры ТТЛ:

- напряжение источника питания Uип= +5 В;

- входное напряжение логического нуля 0,4 ≤ U0вх < 2,4B;

- входное напряжение логической единицы U1вх > 2,4B;

- токи логического нуля I0вх= 1,6mA, и I0вых= 16mA;

- токи логической единицы I1вхи I1вых приблизительно составляют 0,4mA;

- коэффициент разветвления по выходу Краз = I0вых / I0вх =10.

7.2.3. Транзисторно-транзисторная логика с диодами Шоттки

Наряду с обычными схемами ТТЛсуществуют схемыТТЛШ, в которых базо-коллекторные переходы транзисторов шунтированы диодами Шоттки. Это позволяет существенно повысить быстродействие логических элементов, примерно в два раза по сравнению с ТТЛ. ТТЛШ выпускается в виде интегральной серии К555, которая полностью взаимозаменяема с серией К155. Кроме повышенного быстродействия серия К555 обладает примерно в десять раз меньшим энергопотреблением. Входные и выходные токи логического нуля у ТТЛШ составляют I0вх= 0,36mA, и I0вых= 8mA. Таким образом Краз ≈ 22.

7.2.4. Логические схемы с тремя состояниями

Если в схеме рис. 7.2. ввести управляющую линию CS(ChipSelect– выбор кристалла), подсоединив ее через диод к базеVT4 и эмиттеру входного транзистора, ТТЛ вентиль превратится в вентиль с тремя состояниями. Это третье состояние называютZ- состоянием или состоянием с высоким выходным импендансом. Для перевода вентиля вZ- состояние на линиюCSследует подать напряжение логического нуля. В этом случае выходные транзисторыVT4 иVT5 окажутся в закрытом состоянии и выходная линия окажется оторванной как от плюса, так и от минуса источника питания – высокое выходное сопротивление. Когда на линии разрешенияCS=1, схема ведет себя как обычный ТТЛ вентиль.

Выходы таких вентилей можно соединять в одну линию, однако необходимо помнить, что сигнал разрешения может быть передан в каждый момент времени только на один вентиль, т.е. один вентиль находится в активном состоянии, а все другие – в Z- состоянии (не активны). Этот принцип используется в вычислительной технике для подключения периферийных устройств к шинам микропроцессора (шинам адреса, данных и управления).

7.2.5. МОП логика

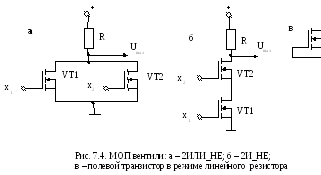

О сновой

этой логики являются полевые транзисторы

с изолированным затвором с каналом

проводимостиn-типа. Для

реализации логических функций используют

последовательно-параллельное соединение

полевых транзисторов (схемы с

непосредственной связью).

сновой

этой логики являются полевые транзисторы

с изолированным затвором с каналом

проводимостиn-типа. Для

реализации логических функций используют

последовательно-параллельное соединение

полевых транзисторов (схемы с

непосредственной связью).

Так например, для рис.7.4, а если к одному из входов приложено напряжение высокого уровня, то соответствующий транзистор переходит в открытое состояние и потенциал выходной линии будет равен логическому нулю. Если на обоих входах х1 и х2 будут нулевые потенциалы, то транзисторыVT1 иVT2 будут закрыты и потенциал выхода будет приблизительно равен потенциалу стока, т.е. логической единице. МОП логика реализуется на интегральной серии К176. Основные параметры этой серии:

- напряжение источника питания Uип= +9 В;

- входное напряжение логического нуля 2,4 ≤ U0вх < 4,7B;

- входное напряжение логической единицы U1вх > 4,7B;

- токи логического нуля I0вх=mA, и I0вых= 1,6mA;

- коэффициент разветвления по выходу Краз ≥102.

7.2.6. Логические схемы на комплементарных МОП – транзисторах (КМОП логика)

Их работа основана на использовании последовательно включенных и управляемых одним сигналом МОП– транзисторов разных типов проводимости. Когда один из последовательно включенных транзисторов открывается, другой – закрывается. Поэтому такой каскад практически не потребляет мощности в статическом режиме.

В логических схемах на КМОП-транзисторах отсутствуют элементы между выходом одного каскада и входом другого. Это объясняется высоким входным сопротивлениемМОП-транзисторов, которое определяется практически только утечками в изоляции и достигает 1012– 1014Ом. Схемотехника базовых логических элементов КМОП-типа заключается в парном использовании транзисторовр-типа иn-типа. Причем если для реализации заданной функции транзисторы сn-каналом включаются последовательно, то парные им транзисторы ср-каналом включаются параллельно и наоборот.

На рис.7.5 приведены схемы логических элементов И-НЕиИЛИ-НЕ. Для схемыИ-НЕпри подаче на затворы напряжения логического нуляUз=U0р-канальные транзисторыVT1-VT3будут открыты;n-канальные транзисторыVT4–VT6будут открыты при подаче логической единицыUз = U1. Если хотя бы на одном из входов будет лог 0, то будет открыт соответствующий транзистор изVT1-VT3и на выходеБЛЭбудет напряжение

у = +Uп = U1

Если

на всехвходах будет действовать

сигналU1, тор-канальные

транзисторыVT1 -VT3закроются, аn-канальные транзисторыVT4-VT6откроются и закоротят

выход элемента на корпус, то естьу =

U0. Таким образом, будет

реализована функцияу =![]() .

.

Схема ИЛИ-НЕработает аналогично. Если хотя бы на один из входов податьU1, то закроется соответствующий транзистор ср-каналом и на выходе будету = U0.

И только, если на все входы податьU0,

то всер-канальные транзисторы

откроются, аn-канальные

закроются и на выходе появится сигналу = U1 = +Uп.

То есть реализуется функцияу =

только, если на все входы податьU0,

то всер-канальные транзисторы

откроются, аn-канальные

закроются и на выходе появится сигналу = U1 = +Uп.

То есть реализуется функцияу =![]() .

.

Защита входов интегральных КМОП-схем от пробоя обычно осуществляется с помощью встроенных диодов, соединяющих входы с шинами источника питания и образующих совместно с выходным сопротивлением источника входного напряжения диодный ограничитель. КМОП логика реализуется на интегральной серии К564. Отличительной особенностью этой серии является плавающее напряжение источника питания Uип= + 3…+ 15 В;

Согласование ТТЛвентилей с КМОПвентилями можно выполнить различными способами. Можно, например, питать вентиль КМОП малыми напряжениями (+5В). При этом сигналы вентиля ТТЛпереключают транзисторы КМОП. Можно применять преобразователи уровня (564ПУ4 при согласовании уровня серийКМОПс сериямиТТЛи 511ПУ2, 564ПУ7, 564ПУ8 при согласовании серийТТЛс сериямиКМОП).