- •Электротехника и электроника электроника

- •Функциональные узлы цифровой обработки сигналов

- •14.1. Логические интегральные схемы

- •Для двухвходового дизъюнктора

- •Инвертора

- •Сумматора на два входа (ос-2)

- •14.2. Счётчики электрических сигналов

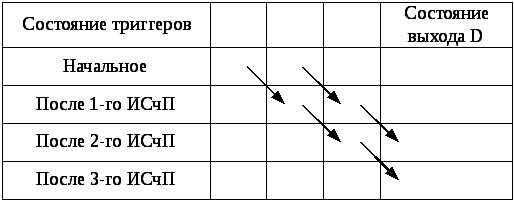

- •Иллюстрация работы трёхразрядного прямого счётчика импульсов

- •14.3. Аналогово-цифровые и цифроаналоговые преобразователи

- •14.4. Регистры

- •Диаграммы изменений состояния разрядных триггеров рг при сдвигах

- •14.5. Сумматоры

- •14.6. Шифраторы

- •Кодирование десятичных символов двоичными тетрадами

- •14.7. Дешифраторы

- •14.8. Мультиплексоры

- •Логическая функция f «сумма по модулю 2»

- •14.9. Микропроцессоры и микропроцессорные системы

- •Основные данные приоритетных образцов поколений мп (1971 -2007 гг.)

Диаграммы изменений состояния разрядных триггеров рг при сдвигах

Примечание. Стрелками обозначены перемещения по разрядной сетке РГ разрядных символов преобразуемого числа при его сдвигах.

Итак, поскольку содержимое РГ проявляется наличием соответствующих высоких (UИПВ – код 1) или низких (0 В – код 0) потенциалов на основных выходах его триггеров, то можно представить, что в исходном состоянии схемы, до подачи импульсов сдвига, на информационных входах ЛЭИс номерами 4, 5, 7 и 8 действуют высокие потенциалы (коды 1), а с номерами 6 и 9 – низкие (коды 0). Тогда, при подаче первого УС серии из трех ИСчП будут сформированы выходные сигналы у ЛЭИс номерами 7, 8 и у ЛЭИЛИс номером 10, а, значит, они появятся наR-входах разрядных триггеров и обнулят их.В это же время выходные сигналы ЛЭИ№ 7, 8 появятся на входах ЛЭИЛИс номерами 2 и 3, которые, в свою очередь, сформируют импульсы (коды 1) на своих выходах. Выходные импульсы ЛЭИЛИ с номерами 2 и 3, воздействуя наS-входы триггеровТ1иТ0, соответственно переведут их в единичные состояния, в результате чего содержимым РГ окажется двоичное число 011, т. е. сдвинутое вправо на 1 разряд исходное число 110. При этом на выходеDРГ сигнала не будет, т. е. будет выдан код 0 младшего разряда исходного числа 110.

Теперь высокие потенциалы выходов триггеров действуют на информационные входы ЛЭ Ис номерами 5, 6, 8 и 9. При поступлении 2-го УС ИСчП выходные сигналы будут сформированы у логических элементов с номерами 10, 8 и 9, каждый из которых выполнит свою функцию:UВЫХ ЛЭ10обнулиттриггеры РГ,UВЫХ ЛЭ8– через ЛЭИЛИс номером 3 – переведёт триггерТ0в единичное состояние, аUвых ЛЭ9послужит сигналом на выходеD– код 1 среднего разряда числа 110.

Содержимым РГ окажется двоичное число 001, а подготовленными к формированию выходного сигнала - только ЛЭ Ис номерами 6 и 9.

Нетрудно, проанализировав взаимодействие элементов и узлов РГ при поступлении последнего, 3-го УС ИСчП, определить, что будут обнулены все триггеры РГ и на выходе Dпоявится код 1 – символ старшего разряда преобразуемого в последовательный код числа 110.

Аналогичным образом, можно рассмотреть работу реверсивного РГ как при сдвигах его содержимого влево, так и выполнении других функций (обращение кодов и преобразование последовательного кода в параллельный).

14.5. Сумматоры

Основным решающим узлом вычислительной техники являются сумматоры (СМ), обеспечивающие простоеарифметическоесложение кодов двух подаваемых на них двоичных чисел.

По устройству они бывают накапливающими(на триггерах) иликомбинационными(на ЛЭ), параллельные (суммирующие во всех разрядах сетки одновременно) или последовательные (поразрядные), с циклическим (последовательным) или сквозным (ускоренным) переносом и т. д.

И каким бы сложным ни было математическое выражение, подлежащее расчёту, все вычисления в цифровой машине в конечном счёте сводятся к сложениючисел, участвующих в операции (операндов), в каком-либо из кодов, например, в обратном, модифицированном обратном, дополнительном, модифицированном дополнительном коде и т. д.

Для сведения всех математических операций над числами к сложению их кодов математиками созданы и продолжают создаваться численные методы их реализации, отличающиеся друг от друга быстротой и точностью вычислений. Например, умножение двух чисел 1001 (множимого) и 0101 (множителя) может быть выполнено сдвигами множимого влево, а множителя вправо и сложением их прямых кодов. В этом случае сдвинутое множимоеобычно заносится в СМ параллельно, т. е. всеми разрядами одновременно, если после сдвигамножителякод с выходаD(см. рис. 14.4.4) оказался 1, и не заносится, если в выдаваемом разряде множителя оказался 0. Операция считается законченной после четырёх (по числу разрядов в разрядной сетке) сдвигов и сложений. Вербально это может быть описано следующей последовательностью действий:

1. Занесение множимого из РГ в СМ, поскольку

в младшем разряде множителя 1:

![]() .

.

2. Сдвиг множимого в РГ на один разряд

влево без занесения сдвинутого числа

в СМ, так как в очередном разряде

множителя 0:

![]() .

.

3. Сдвиг множимого в РГ ещё на один разряд влево и занесение его в СМ, поскольку в следующем разряде множителя 1: (+) 1001.

4. Сдвиг множимого в РГ ещё на один разряд

влево без занесения сдвинутого числа

в СМ, так как в старшем разряде множителя

снова 0:

![]() .

.

В результате в СМ образовалось произведение 0101101 (9 х 5 = 45[10]).

В настоящее время наиболее распространены комбинационныеСМ, которые строятся из одноразрядных сумматоров на 3 входа (ОС-3) или на 2 входа (полусумматоры) (ОС-2). Входы в сумматор разрядов слагаемых обычно обозначаются начальными буквами алфавита (Аi,Вi и т. д.), а выходы – конечными (Si – сумма вi-м разряде иPi– перенос в соседний старшийi+1 разряд). УГО ОС–3 (SMi) и ОС–2 (HSi) представлены на рис. 14.5.1. Структурная схема многоразрядного сумматора комбинационного типа показана на рис. 14.5.2.

Для раскрытия принципа построения функциональных схем одноразрядных сумматоров проанализируем их работу на примере полусумматора, таблица истинности которого приведёна ниже.

Рис. 14.5.1. УГО

одноразрядных комбинационных

сумматоров ОС-3

(а)

и ОС-2 (б)

Рис. 14.5.2. Структурная

схема многоразрядного сумматора на ЛЭ

Таблица 14.5.2

Таблица истинности

работы полусумматора

Вход

А Вход

В Выход

S Выход

Р 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1

Анализ данных табл. 14.5.2 приводит к следующим выводам:

– для образования единицы переноса (Р= 1) должна использоваться логическая схема совпадения – ЛЭИ1, дающая сигнал на выходе в случае равенства единице кодов обоих слагаемых;

– для получения суммы Sв данном разряде должен использоваться второй ЛЭИ2, на выходе которого сигнал единицы будет формироваться тогда, когда одно из слагаемых равно единице (на выходе ЛЭИЛИесть сигнал) и нет переноса (на выходе ЛЭНЕесть сигнал). В других случаях сигналы на выходахSиPдолжны отсутствовать.

Поэтому функциональная схема полусумматора на ЛЭ принимает вид, показанный на рис. 14.5.3.

Рис. 14.5.3.

Функциональная схема комбинационного

полусумматора ОС-2

Более сложной является схема одноразрядного сумматора на ЛЭ ОС-3, третьим входом которой служит выход переноса сумматора предыдущего разряда. Его работа описывается следующими логическими выражениями:

Анализ приведённых логических выражений показывает, что для образования одноразрядного логического автомата ОС-3, формирующего результаты операции в виде суммы Siи переносаPi в соседний старший разряд, необходимы два ЛЭИЛИна четыре входа каждый, семь ЛЭИна три входа каждый и три ЛЭНЕдля инвертирования входных данных. Функциональная схема автомата, реализующего эти зависимости, показана на рис. 14.5.4.

Если компьютер работает с n-разрядными числами, то в СМ используется соответственноnодноразрядных сумматоров ОС-3.

Важно отметить то, что поскольку комбинационные сумматоры не имеют собственных элементов памяти, они непосредственно связаны с регистрами чисел (операндов).

В интегральной схемотехнике, кроме одноразрядных, выпускаются и используются 2-разрядные и 4-разрядные сумматоры.

В системе обозначений интегральных микросхем по функциональному назначению для сумматоров предусмотрены две отличительные буквы: ИМ. Например, в серии микросхем К155 используются ИМС К155ИМ1 – одноразрядный СМ, К155ИМ2 – 2-разрядный и К155ИМ3 – 4-разрядный сумматоры.

Рис. 14.5.4.

Функциональная схема одноразрядного

комбинационного СМ ОС-3