- •Электротехника и электроника электроника

- •Функциональные узлы цифровой обработки сигналов

- •14.1. Логические интегральные схемы

- •Для двухвходового дизъюнктора

- •Инвертора

- •Сумматора на два входа (ос-2)

- •14.2. Счётчики электрических сигналов

- •Иллюстрация работы трёхразрядного прямого счётчика импульсов

- •14.3. Аналогово-цифровые и цифроаналоговые преобразователи

- •14.4. Регистры

- •Диаграммы изменений состояния разрядных триггеров рг при сдвигах

- •14.5. Сумматоры

- •14.6. Шифраторы

- •Кодирование десятичных символов двоичными тетрадами

- •14.7. Дешифраторы

- •14.8. Мультиплексоры

- •Логическая функция f «сумма по модулю 2»

- •14.9. Микропроцессоры и микропроцессорные системы

- •Основные данные приоритетных образцов поколений мп (1971 -2007 гг.)

П

Таблица 14.9.1

№ поколения

и год выпуска

Шифр МП и

фирма- изготовитель

Кол-во транзисторов

в кристалле, технология

Раз-ряд- ность

Тактовая часто-та,

МГц Примечания I 1972

МП 8080 Intel

(США)

6 тыс., (нет

данных) 8 2 На

его основе был создан первый персональный

компьютер (ПК) II 1982

МП 80286 Intel

(США)

134

тыс., (нет

данных) 16 2 Добавлены

виртуальная память (винчестер) и

мультизадачный режим. Стал основой

ПК PC/AT III 1985

МП 80386 Intel

(США)

275 тыс., (нет

данных) 32 33 Введена

внешняя КЭШ-память. Адресная память

достигла 4 Гбайт, виртуальная – 64

Гбайт IV 1989

МП 80486 Intel

(США)

1,2 млн., (нет

данных) 32 64 Расширен

набор команд; дополнительно встроена

внутренняя КЭШ-память для данных и

команд, управляемая спец. контроллером;

реализована конвейеризация вычислений,

добавлен математический сопроцессор V

1993 1997 Pentium

(МП

80586)

Pentium

ММХ Intel

(США)

3.1 млн.,

0,8-мкм,

0,25-мкм технологии 64 166 2

конвейера вычислений с 5 ступенями;

разделена КЭШ-память для данных и

команд; модернизирован сопроцессор

и т. д. VI

1995 1997 1999 Pentium

PRO

(МП

80686), Pentium

II, Pentium

III Intel

(США)

5,5 млн.,

0,25 –мкм,

0,22-мкм, 0,18-мкм технологии 64

233

450 733 3

конвейера с 14 ступенями; 2-х уровневая

КЭШ-память с переносом второго уровня

с материнской платы в МП; расширен

набор команд и т.д. VII

1999 2003 AMD

K-7

AMD

(США), Pentium

IV

(Willamate) Intel

(США)

22 млн.,

0,22-мкм,

0,18-мкм технологии 64

500

3000 (3ГГц) Переход

на новые субмикронные технологии,

модернизация системной шины

(магистрали), рас-ширение КЭШ-памяти

и рост числа конвейеров

Основные данные приоритетных образцов поколений мп (1971 -2007 гг.)

1. Шинами (магистралями) на схемах обозначаются многопроводные линии связи, формируемые в процессе изготовления кристалла МП.

2. Для уменьшения количества внешних соединений МП как для ввода, так и для вывода данных используют одни и те же линии, переключаемые на соответствующий режим специальным интерфейсным устройством (на схеме не обозначено).

Основное отличие МП от стандартных ИМС (элементов с жесткой логикой) – способность микропроцессоров действовать по заданной программе. В них входные данные (входной сигнал) через соответствующие шины поступают в УУ МП, вырабатывающее фиксированную последовательность команд, выполнение которой АЛУ и регистрами микропроцессора приводит к требуемым результатам, передаваемым через шины ввода/вывода в исполнительное звено САУ, в другой МП, на индикацию и т. д.

МП с микропрограммным управлением (МП с МПУ) обычно состоят из нескольких кристаллов (блоков) БИС, каждый из которых аналогичен МП саппаратнымуправлением, но настроен на выполнение функций блока центральных процессорных элементов (ЦПЭ), блока микропрограммного управления (БМУ) или блока памяти микропрограмм (БПМП) соответственно. Обобщённая схема структуры МП с МПУ показана на рис. 14.9.2.

С

Рис. 14.9.2. Структурная

схема МП

с микропрограммным управлением:

1 – выходная шина

адреса; 2 – выходная шина данных

и 3 – входная шина

данных

Узлы внутренней памяти МП (ячейки ЗУ), как правило, содержат группу регистров общего назначения (РОН), которые служат операционной памятью МП, и группу специальных регистров, в том числе аккумулятор и стек, которые используются для организации вычислительного процесса, счётчика команд, выработки признаков результата (флажков) и некоторых других функций. Учитывая особую роль устройств памяти (ЗУ) в МП, охарактеризуем их основные параметры, типовой набор сигналов управления и структуру.

Важнейшими параметрамиЗУ МП являются ихинформационнаяёмкостьибыстродействие (производительность).

Ёмкость обычно измеряется в величинах, кратных битам (1 бит – ёмкость одного двоичного разряда, хранимого, например, триггером) или байтам (1 байт – это ёмкость одной 8 разрядной ячейки памяти). При этом добавление префикса к (кило) к основной единице измерения означает умножение её на 210= 1024, а добавлением префикса М (мега) – на 220= 1048576.

Быстродействие памяти, как правило, определяется количеством коротких операций считывания слов из ячеек памяти, производимых за 1 секунду, или величиной тактовой частоты, измеряемой в Гц, кГц, МГц или ГГц.

Поскольку для МП, как и любого другого цифрового вычислительного средства, характерна шинная(магистральная) структура обмена информацией, то нужная команда или требуемое данное (операнд) выбирается в нём из шины управления (ШУ) или шины данных (ШД) соответственно. В эти шины они попадают, будучи сосчитанными из ячеек памяти с соответствующими номерами, называемыми их адресами (А). Адреса требуемых ячеек передаются вЗУпо специальной адресной шине (ША). Количество различных адресов, которые могут быть переданы поn-проводниковой ША, а значит, и число ячеек памяти, к которым возможно обращение, ограничено числомN= 2n. При этом разрядность адресаnсвязана с числом ячеекN соотношениемn=log2N. Адреса же изменяются отn нулей (адрес первой ячейки) доnединиц (адрес 2n-й ячейки). Например, при ёмкости ЗУ в 1024 ячейки (210) адресом 1-й ячейки будетА1= = 0000000000[2] (десять нулей), т.е. номер 0[10], а адресом 1024-й ячейки –А1024= = 1111111111[2](десять единиц), т.е. номер 1023[10], или в общем виде – максимальным адресом может быть номер, равный числу (2n– 1)[10].

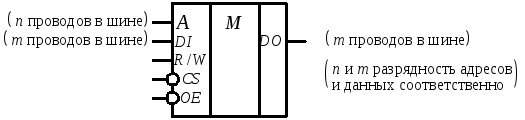

Для выполнения функций ЗУ МП обычно используется следующий набор управляющих сигналов:

А – адрес ячейки;

CS(ChipSelect) илиCE(ChipEnable) – разрешение или запрещение работы данной микросхемы (при наличии в ЗУ нескольких микросхем памяти);

R/W(Read/Write) – сигнал на выполнение чтения (1) или записи (0);

DI(DataInput) илиDO(DataOutput) – подключение ШД для приёма входных или передачи выходных данных. При использовании общей ШД для работы с входными и выходными данными применяется сигналDIO;

OE(OutputEnable) – отключение буферных каскадов от ШД.

УГО типовой микросхемы ЗУ МП показано на рис. 14.9.3.

Важнейшими параметрамиЗУ МП являются ихинформационнаяёмкостьибыстродействие (производительность).

К

Рис. 14.9.3. УГО

типовой микросхемы ЗУ (М

– memory

– память)

По способу доступа к ячейкам памяти различают ЗУ адресные, споследовательнымдоступом иассоциативные.

АдресныеЗУ были созданы первыми и получили наибольшее распространение. Они до настоящего времени применяются во всех цифровых устройствах в качестве оперативнойRAM(RandomAccessMemory) памяти, в том числе внутренней сверхоперативной (СОЗУ) или так называемой КЭШ-памяти на триггерах, и постояннойROM (ReadOnlyMemory) памяти. Обычно постоянная память (ПЗУ) программируется ещё при изготовлении МП методами интегральной технологии и не подлежит изменению при эксплуатации. Вместе с тем, в последнее время были разработаны и получили распространение новые разновидностиROM-памяти: РROM, ЕРROMи ЕЕРROM, наличие буквыР(отProgrammable) в аббревиатуре которых характеризует их возможности к одноразовому (РROM) или многоразовому (ЕРROM– путём облучения кристалла ультрафиолетовыми лучами, а ЕЕРROM –электрическими сигналами) перепрограммированию ПЗУ пользователем. Здесь следует отметить, чтоЕЕРROM-память дала жизнь самой быстродействующей флэш-памяти (flash– вспышка). Это вполне объяснимо, так как чтобы использовать всю информацию ПЗУ типа ЕЕРROM, требуется последовательное обращение к каждой её ячейке, а для флэш-памяти достаточно подачи одного сигнала.

Разработка флэш-памяти – наивысшее достижение схемотехники полупроводниковых программируемых ЗУ (ППЗУ). Особенностью флэш-памяти является то, что в ней не предусмотрены запись и стирание информации отдельными словами, а они производятся блоками или всей памятью одновременно. При чём эти операции осуществляются не программатором, а самим МП вычислительного устройства, действующим в обычном рабочем режиме. Перспективным является использование файловойфлэш-памяти, которая идёт на замену памяти на жёстких магнитных дисках (винчестерах) с динамическими полупроводниковыми ОЗУ. Если в ПК с винчестером программа сначала должна быть считана с диска и записана в ОЗУ, то при использовании флэш-памяти команды программы читаются процессором непосредственно из её файлов, кстати туда же записываются и результаты вычислений.

ЗУ с последовательным доступомобычно используются в качестве буферной, файловой или циклической памяти, в которых записываемые данные образуют очередь, считываемую в порядке их записи или в обратном порядке. В них адресом служит номер в очереди. Примером циклического ЗУ со считыванием в порядке записи может служить полупроводниковая видеопамять (VRAM), а считыванию в обратном порядке свойственна работастековыхЗУ, где реализован принцип «последний пришёл – первый ушёл».

Стек (магазинная память) – это эффективное программно-аппаратурное средство для сохранения и возврата данных при контекстном1переключении и осуществлении многократных прерываний. Образным аналогом стека может служить этажерка, чьи полки соответствуют ячейкам, где «положить» (записать) слово можно только выше последнего положенного слова, а «взять» (считать) – только то, которое положено последним. Для осуществления именно такого порядка работы стек имеет специальный реверсивный регистр – указатель состояния стека (РСС). При поступлении запроса, например, от ВУ на прерывание исполняемой программы для его удовлетворения УУ МП автоматически выполняет команду «Записать состояние в стек». При её осуществлении производится запись контекстного состояния рабочих регистров МП в стек, добавление единицы в РСС после каждой записи и последующий перевод МП на выполнение новой программы (подпрограммы). Возврат к выполнению прерванной программы также осуществляется УУ МП автоматически по команде «Восстановить состояние», в процессе выполнения которой в счётчик команд из РСС заносится адрес возврата из прерываний, указывающий на команду, которая должна выполняться первой. Возможность управления организованными переходами от выполнения одной подпрограммы к другой с запоминанием промежуточных состояний позволяет осуществлять последовательное завершение всех подпрограмм основной программы.

АссоциативныеЗУ обладают достаточно высоким быстродействием и реализуют поиск информации по некоторому признаку –тегу(tag– ярлык, этикетка) во входном слове (теговом адресе). В частности, этим признаком может служить и полный адрес ячейки ОЗУ. Основная область применения ассоциативных ЗУ – внешняя КЭШ-память данных. При этом следует иметь в виду, что ёмкость современных ОЗУ превосходит сотни мегабайт, а ёмкость ассоциативных ЗУ ограничивается лишь сотнями килобайт.

Типовая структура микропроцессорной системы показана на рис. 14.9.4.

Рис. 14.9.4. Структура

микропроцессорной системы

К основным узлам МП относятся устройство управления (УУ), арифметико-логическое устройство (АЛУ), регистр команд (РК), дешифратор команд (ДШК), регистр флажков (РФ), наборы адресных регистров (РА), регистров данных (РД), общего назначения (РОН), аккумулятор (РГ «А»), стек, программный счётчик (ПС) и устройство управления шинами (УУШ).

АЛУ выполняет арифметические, логические и сдвиговые операции, формируя при этом признаки их результата – флажки, которые записываются в специальный регистр РФ. Эти флажки служат условиями для выполнения команд условного перехода (УП).

Флажков обычно бывает шесть: 1) флажок знака, код которого формируется в старшем бите мантиссы результата (1 – результат отрицательный, 0 – положительный): 2) флажокнуля–единицы, если результат равен нулю; 3) флажокпаритета– 1, если в младших битах чётное число единиц; 4) флажокпереноса– 1, если возникает перенос (или заём) из старшего бита мантиссы; 5) флажоквспомогательногопереноса – 1, если возникает перенос (заём) из третьего бита при выполнении арифметических операций в двоично-десятичном коде; 6) флажокпереполнения– 1, если произошло переполнение разрядной сетки, то есть результат не поместился в установленном диапазоне.

Каждый из регистров данных, кроме арифметических функций, в некоторых командах выполняют и другие операции. Так через аккумулятор (РГ«А») может осуществляться обмен данными между МП и ВУ при выполнении команд ввода/вывода, а регистр данных (РД) в некоторых командах ввода/вывода хранит адрес взаимодействующего порта ввода/вывода – соответствующего регистра ВУ. При этом весь обмен информацией МП с ВУ всегда осуществляется через блок интерфейса, состоящий из набора различныхмикроконтроллеровиадаптеров.

Интерфейсв микропроцессорных системах (МПС) – это совокупность аппаратных, программных и конструкторских средств, обеспечивающих информационный обмен между устройствами системы. К аппаратным средствам относятся отдельные узлы системы, через которые осуществляется обмен информацией (адресами, данными или управляющими сигналами). Под программными средствами подразумевается строгий порядок (алгоритм) следования информационных и служебных сигналов, обеспечивающих рабочее взаимодействие устройств МПС, реализованный в виде специальных программ.Конструкторскимисредствами интерфейса служат линии связи, объединённые в шины, по которым осуществляется обмен информацией. Приём и передача данных в устройствах МПС реализуются через специальные буферные узлы (регистры), называемыепортами. Порты могут быть параллельными, если информация в них обрабатывается всеми разрядами одновременно, или последовательными (при больших расстояниях между приёмником и источником информации), когда информация в порт поступает по одной линии связи разряд за разрядом. В последовательных портах осуществляется преобразование данных из параллельного кода в последовательный при их передаче и из последовательного в параллельный – при их приёме.

Структурная схема фрагмента интерфейсных связей МП с внешними устройствами (ВУ) и оперативной памятью (ОЗУ) в МПС с соответствующими шинами показана на рис. 14.9.5.

Связь МП, которую необходимо обеспечить

через выводы его корпуса, должна

минимально включать десять групп линий

связи – информационных и управляющих

шин. В частности, для обеспечения связи

МП с ВУ по шине 1 передаётся код адреса

требуемого устройства из ВУ (адрес

порта), по шине 2 – сигнал управления

считыванием/записью (R/W),

по шине 3 – сигнал запроса на прерывание,

по шинам 4 и 5 осуществляется передача

обрабатываемых данных от МП к ВУ или от

ВУ к МП соответственно.

Рис. 14.9.5. Структурная

схема интерфейсных связей МП в МПС

(фрагмент)

Шины связи МП с ОЗУ имеют следующее предназначение: 6 – адресная, 7 – управляющая чтением/записью (R/W), 8 – принимающая команды, подлежащие исполнению МП, 9 и 10 – шины обмена данными из ОЗУ в МП и обратно соответственно (подробнее см. рис. 14.9.3). Поскольку электрические сигналы МПС зачастую имеют разные форматы существует необходимость в преобразовании интерфейсов. Операции преобразования интерфейсов обычно осуществляются интерфейсными контроллерами(< англ.controller– управитель), которые часто называются периферийнымиадаптерами(<лат.adaptare– приспособлять, преобразовывать). Структура типового адаптера показана на рис. 14.9.6.

Рис. 14.9.6. Структура

параллельного периферийного адаптера

Адаптер подключается к системной ШД через канал данных, включающий шинные формирователи, которые усиливают сигналы источника по мощности или отключают его от шины, когда он не участвует в обмене, или при необходимости формирует требуемые уровни сигналов лог. 0 или лог.

Контроллеры – это блоки местного управления (БМУ) средствами ввода/вывода информации, физически и логически координирующими взаимодействие информационно-управляющих шин МПС с узлами ВУ, которые служат источниками (датчиками) или приёмниками (потребителями) данных и управляющей информации.

Контроллеры задают порядок следования, количество и электрические параметры сигналов, обеспечивающих своевременность и необходимую направленность прохождения информации между МП и ВУ. Одни из них являются специализированнымина конкретное использование только в определённом устройстве. Они выполнены как цифровые автоматы на основе аппаратурной логики жёсткими соединениями между группами вентилей, триггеров и других элементов обслуживаемых узлов. Вместе с тем, наибольшее применение нашлиуниверсальныепрограммируемые контроллеры, которые реализуются или в виде однокристальных БИС, или на основе секций микропроцессорных комплектов (МПК) БИС. В них необходимые временные диаграммы последовательностей управляющих сигналов создаются соответствующим распределением импульсов тактовых генераторов (ГТИ) не путём контактных проводных соединений, а методом преобразования последовательностей команд (микрокоманд). Перепрограммирование такого контроллера осуществляется лишь перезаписью содержимого ячеек его памяти без изменения аппаратной реализации МП. Обобщённая структура универсального контроллера показана на рис. 14.9.7.

Рис. 14.9.7. Структурная

схема универсального программного

контроллера

Каждый контроллер работает автоматически по заранее введённой в него программе. Основными задачами контроллера при этом являются обеспечение отпирания и запирания одиночных вентилей или их групп, запуск электромеханических переключателей, возбуждение соленоидов, приём усиленных или сформированных разнообразных сигналов датчиков информации – пульта управления (ПУ) и узлов различных устройств ввода/вывода (УВВ).

Анализ схемы (рис. 14.9.7) показывает, что устройства контроллера, как и обычного МП, связаны шинами кодов адресов (ША), данных (ШД) и сигналов управления (ШУ), он имеет свои кристаллы БИС оперативной (ОЗУ) и постоянной (ПЗУ) памяти и управление, обеспечиваемое собственным МП.

Узлы программируемого интерфейса (УПИ) и сопряжения (УС), обычно имеющие модульную структуру, дают возможность как наращивать их при усложнении или увеличении числа УВВ, так и осуществлять переходы от внутрисистемного интерфейса к интерфейсу разнообразных УВВ, т. е. учитывать их специфику.

В заключение рассмотрения общих сведений о МП (рис. 14.9.8) покажем обобщённую структурную схему типовой МПС, например, микроЭВМ, в которой в качестве всех блоков местного управления используются соответствующие программируемые контроллеры (К).

Рис. 14.9.8. Обобщённая

структурная схема МПС (вариант типовой

микроЭВМ)

Основными программируемыми контроллерами в схеме обозначены КСПУ – контроллер системного пульта управления (СПУ); КУВВ – контроллеры одиночных средств ввода/вывода (УВВ) и ГрКУВВ – групповой контроллер УВВ. Оперативное (ОЗУ) и постоянное (ПЗУ) ЗУ управляются с помощью контроллеров КОЗУ и КПЗУ соответственно. При такой организации МПС центральный процессор (ЦП) обеспечивает программируемые контроллеры только управляющей информацией высокого уровня, детализируемой самими контроллерами. Поэтому нагрузка на системную информационную шину снижается, что позволяет увеличить скорость передачи данных.

Вместе с тем следует отметить, что развитые МПС могут быть классифицированы и как многопроцессорные вычислительные системы, в которых каждый контроллер, в принципе, имеет те же возможности, что и центральный процессор. Всё это позволяет повысить быстродействие используемых средств за счёт введения распределённого управления и обработки информации во всех подсистемах МПС.

Появление же новых способов организации вычислительного процесса приводит к созданию более эффективных микропроцессорных систем с децентрализованным. управлением и обработкой информации.

Детальное изучение конкретных комплектов МП и МПС, применяемых в корабельной технике и вооружении, и их программного обеспечения предусмотрены программами специальных учебных дисциплин.

1Буль Дж. (см. прил.1).

1 < англ. count – считать, подсчитывать.

1См. прил. 1.

1 (<лат. contextus – тесная связь, соединение).