- •Электротехника и электроника электроника

- •Функциональные узлы цифровой обработки сигналов

- •14.1. Логические интегральные схемы

- •Для двухвходового дизъюнктора

- •Инвертора

- •Сумматора на два входа (ос-2)

- •14.2. Счётчики электрических сигналов

- •Иллюстрация работы трёхразрядного прямого счётчика импульсов

- •14.3. Аналогово-цифровые и цифроаналоговые преобразователи

- •14.4. Регистры

- •Диаграммы изменений состояния разрядных триггеров рг при сдвигах

- •14.5. Сумматоры

- •14.6. Шифраторы

- •Кодирование десятичных символов двоичными тетрадами

- •14.7. Дешифраторы

- •14.8. Мультиплексоры

- •Логическая функция f «сумма по модулю 2»

- •14.9. Микропроцессоры и микропроцессорные системы

- •Основные данные приоритетных образцов поколений мп (1971 -2007 гг.)

В

Таблица истинности

для одноразрядного

Вход

Вход Выход

Выход 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1

Рис. 14.1.8. УГО ЛЭ

И-НЕ

(а)

и ИЛИ-НЕ

(б)

с инвертирующими выходамиСумматора на два входа (ос-2)

![]()

![]()

![]()

![]()

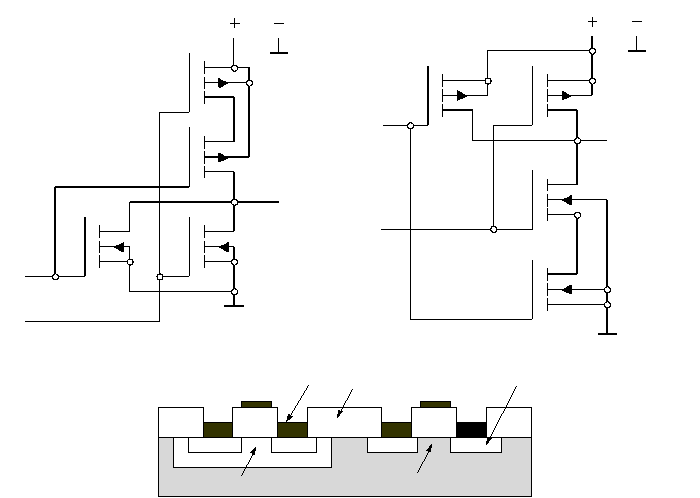

Например, если в схеме на рис. 14.1.9, а

на обоих входахх1и х2сигналы будут отсутствовать (коды 0), то

транзисторыVT1и VT2сn-каналом окажутся

закрытыми, так как разность потенциалов

между их затворами и истоками (корпусом)

равна нулю, аVT3и VT4ср-каналом – открытыми, поскольку

нулевой потенциал их затворов создаёт

отрицательную разность потенциалов

относительно соответствующих подложек,

что индуцирует в нихр-канал. А так

как через эти каналы протекают

пренебрежительно малые токи запертых

транзисторовVT1и VT2, то и

падения напряжения на транзисторахVT3и VT4незначительны, а всё напряжение![]() приложено к стокам транзисторовVT1и VT2, что

соответствует действию на выходе схемыукода 1.

приложено к стокам транзисторовVT1и VT2, что

соответствует действию на выходе схемыукода 1.

Рис. 14.1.9. Базовые

ЛЭ на КМОП-транзисторах: ИЛИ-НЕ

(а),

И-НЕ

(б)

и

схема разреза

КМОП-структуры (в)

Если же хотя бы на один из входов, например

х1, поступит сигнал (код 1), т.

е. потенциал близкий к![]() ,

то закроется транзистор ср-каналомVT3, чем будет

отключен потенциал источника питания

,

то закроется транзистор ср-каналомVT3, чем будет

отключен потенциал источника питания![]() от выходау, к которому через

открывшийся транзисторVT1окажется подключённым корпус (код 0).

от выходау, к которому через

открывшийся транзисторVT1окажется подключённым корпус (код 0).

Таким образом, рассмотренная схема реализует функцию ИЛИ-НЕ. Аналогично работают пары транзисторов в схеме на рис. 14.1.9,б, реализующей функциюИ-НЕ.

Некоторые возможности реализации основных логических связей И, ИЛИиНЕс помощью базовых ЛЭИЛИ-НЕиИ-НЕпоказаны соответственно на рис. 14.1.10 и рис. 14.1.11.

Рис. 14.1.10. Реализация

ЛЭ НЕ

(а),

И

(б)

и ИЛИ

(в)

с помощью ЛЭ ИЛИ-НЕ

Рис. 14.1.11. Реализация

ЛЭ НЕ

(а),

И

(б)

и ИЛИ

(в)

с помощью ЛЭ И-НЕ

Функциональное назначение ЛЭ маркируется двумя символами, начинающимися с буквы Л: НЕ– ЛН,ИЛИ – ЛЛ,И– ЛИ,И-НЕ– ЛА и т. д.

14.2. Счётчики электрических сигналов

Счётчиками называются функциональные узлы электронной техники, предназначенные для подсчёта и запоминания числа поступивших на их вход электрических импульсов. Как и другие элементы памяти, они бывают асинхронными и синхронными (тактируемыми), в которых счётный (общий) вход обозначается символомС1, а тактовый или синхронизирующий (СИ) вход –CLK.На рис. 14.2.1 показаны УГО для двух типов счетчиков импульсов.

Счётчики применяются для подсчёта номеров команд, реализующих программы ЭВМ, для выполнения этапа кодирования в АЦП; для определения дистанции до цели в РЛК и ГАК; для определения контролируемых величин в цифровых радиоизмерительных приборах, часах, таймерах и т. д.).

Примечания.

1. Наибольшее десятичное число N, которое может быть представлено используемыми n разрядами в двоичной системе счисления, равно N = 2n–1. Например: шестью двоичными разрядами можно представить в двоичной системе счисления максимальное десятичное число N = 26 – 1 = 64 – 1 = 63.

2. Код 8421 – это

двоично-десятичный код, служащий для

выражения цифры каждого разряда

десятичных чисел соответствующей ей

двоичной тетрадой

(соответствующим 4 разрядным двоичным

числом). Например: 0257[10]

![]() 0000 0010 0101 0111[2-10].

0000 0010 0101 0111[2-10].

Рис. 14.2.1. УГО

асинхронного (а)

и синхронного (б)

счётчиков импульсов

Счётчики электрических импульсов классифицируются по:

– системе счисления -двоичные, десятичные, двоично-десятичные (типа 8421),пересчётные схемы (у минут и секундк= 60, у часов – 24) и т. д.;

– направлению счёта- суммирующие или прямые (+1, +1 и т.д.), вычитающие или обратные (–1, –1, –1 и т.д.) и реверсивные (двунаправленные)

– элементной базе - на дискретных элементах (ламповые, транзисторные и т.п.), гибридные, на интегральных микросхемах и т. д.

Строятся счётчики, как правило, из последовательного набора разрядных асинхронныхТ-,RST- или синхронныхJK-триггеров, состояние которых и определяет число подсчитанных импульсов.

Прямым счётчикомимпульсов называют счётчик, содержимое которого увеличивается на 1 с приёмом каждого очередного входного импульса, поэтому их часто определяютсуммирующими.

Устройство и работу прямого счётчика рассмотрим на примере трёхразрядного суммирующего счётчика электрических импульсов, построенного на RST-триггерах, структурная схема которого приведена на рис. 14.2.2.

Представленный на рис. 14.2.2 прямой (суммирующий) счётчик содержит три разрядныхRST-триггера,R-входы которых объединены шинойгашения, а их основные выходы (выходы прямого кода)у0, у1иу2последовательно подсоединены кТ-входам триггеров соседних старших разрядов.

Н

Рис. 14.2.2. Структурная

схема асинхронного трёхразрядного

прямого счётчика

с последовательным

переносом

![]() наТ-вход триггера изменяет его

первоначальное состояние на противоположное

и это проявляется в соответствующих

перепадах напряжения на основном выходе

триггера. Эти перепады напряжения,

поступая на дифференцирующую цепьТ-входа соседнего триггера старшего

разряда, вызывают формирование на её

выходе остроконечных импульсов

чередующейся полярности. Например, при

переходе первого триггера изнулевогосостояния вединичноена его выходе

прямого кода происходит перепад

напряжения из низкого (код 0) уровня в

высокий (код 1). Это вызывает появление

на выходе соответствующей дифференцирующей

цепи остроконечного импульсаположительнойполярности. Сигналы такой полярности

не пропускаются диодамиТ-входа

соседнего триггера, чем сохраняется

его прежнее состояние. Если же первый

триггер меняет своё состояние из 1 в 0,

то дифференцирующая цепь, подсоединённая

к его выходу прямого кода, формирует

остроконечный импульсотрицательнойполярности. Такой сигнал пропускается

соответствующим диодомТ-входа

второго триггера на базу открытого в

это время транзистора, который, закрываясь,

вызывает переход состояния триггера

на противоположное. Таким образом,

триггеры в счётчиках меняют своё

состояние, как говорят, позаднему

фронтувходного импульса, поступающего

на его Т-вход.

наТ-вход триггера изменяет его

первоначальное состояние на противоположное

и это проявляется в соответствующих

перепадах напряжения на основном выходе

триггера. Эти перепады напряжения,

поступая на дифференцирующую цепьТ-входа соседнего триггера старшего

разряда, вызывают формирование на её

выходе остроконечных импульсов

чередующейся полярности. Например, при

переходе первого триггера изнулевогосостояния вединичноена его выходе

прямого кода происходит перепад

напряжения из низкого (код 0) уровня в

высокий (код 1). Это вызывает появление

на выходе соответствующей дифференцирующей

цепи остроконечного импульсаположительнойполярности. Сигналы такой полярности

не пропускаются диодамиТ-входа

соседнего триггера, чем сохраняется

его прежнее состояние. Если же первый

триггер меняет своё состояние из 1 в 0,

то дифференцирующая цепь, подсоединённая

к его выходу прямого кода, формирует

остроконечный импульсотрицательнойполярности. Такой сигнал пропускается

соответствующим диодомТ-входа

второго триггера на базу открытого в

это время транзистора, который, закрываясь,

вызывает переход состояния триггера

на противоположное. Таким образом,

триггеры в счётчиках меняют своё

состояние, как говорят, позаднему

фронтувходного импульса, поступающего

на его Т-вход.

Для начала необходимо отметить, что одним из базовых принциповобработки информации элементами и узлами цифровой электроники является принцип еёзамещения, который требует сохранения информации на носителе до момента необходимости её обновления. Поэтому обычно работа счётчика начинается с его очистки от хранимой информации (содержимого) путёмобнуленияразрядных триггеров счётчика одновременной подачей управляющего сигнала Уст.«0» на все ихR-входы. Это приводит к появлению на прямых выходах триггеров счётчикау0у1у2соответственно исходной кодовой комбинации 000. Если же нужен другой показатель начального отсчёта, он может быть установлен с помощью кодовых сигналов, подаваемых наS-входы соответствующих триггеров. Такие операции нужны, например, при задании адреса первой команды программы, подлежащей реализации на ЭВМ, при установке требуемого времени на часах или таймерах и т. д.

Пусть в рассматриваемом случае счёт

будет вестись от нуля. Тогда

поступление 1-го импульса![]() наТ-вход триггера младшего разрядаТ0изменит егонулевоесостояние наединичное(из 0 в

1-переднийфронт на основном выходе).

Формируемый дифференцирующей цепьюТ-входа триггераТ1положительныйимпульс из перепада

напряжения на выходеу0триггераТ0не будет пропущен диодами

к базам транзисторов и не произведёт

изменения состояния триггера следующего

старшего разрядаТ1. Таким

образом, счётчик принял и будет сохранять

до поступления очередного счётного

импульса своё новое состояние – код

001, которое называетсясодержаниемсчётчика.

наТ-вход триггера младшего разрядаТ0изменит егонулевоесостояние наединичное(из 0 в

1-переднийфронт на основном выходе).

Формируемый дифференцирующей цепьюТ-входа триггераТ1положительныйимпульс из перепада

напряжения на выходеу0триггераТ0не будет пропущен диодами

к базам транзисторов и не произведёт

изменения состояния триггера следующего

старшего разрядаТ1. Таким

образом, счётчик принял и будет сохранять

до поступления очередного счётного

импульса своё новое состояние – код

001, которое называетсясодержаниемсчётчика.

При поступлении 2-го импульса

![]() наТ-вход триггераТ0последний изменит своё состояние из 1

в 0 (заднийфронт), что вызовет

появление на выходе дифференцирующей

цепи остроконечного импульса отрицательной

полярности, воздействующего наТ-вход

триггераТ1. Это воздействие

изменит состояние триггераТ1из 0 в 1 (переднийфронт), которое не

повлияет на состояние следующего

старшего триггераТ2.

Следовательно, счётчик примет и будет

сохранять до поступления очередного

счётного импульса

наТ-вход триггераТ0последний изменит своё состояние из 1

в 0 (заднийфронт), что вызовет

появление на выходе дифференцирующей

цепи остроконечного импульса отрицательной

полярности, воздействующего наТ-вход

триггераТ1. Это воздействие

изменит состояние триггераТ1из 0 в 1 (переднийфронт), которое не

повлияет на состояние следующего

старшего триггераТ2.

Следовательно, счётчик примет и будет

сохранять до поступления очередного

счётного импульса![]() состояние 010 и т. д. до подсчёта 7 импульсов.

При поступлении на вход прямого

трёхразрядного счётчика 8-го импульса

произойдёт так называемое переполнениеразрядной сетки, которое проявляется

в обнулении его триггеров, что должно

быть предотвращено. Изменение состояний

триггеров в процессе работы прямого

счётчика удобно проиллюстрировать

табл. 14.2.1.

состояние 010 и т. д. до подсчёта 7 импульсов.

При поступлении на вход прямого

трёхразрядного счётчика 8-го импульса

произойдёт так называемое переполнениеразрядной сетки, которое проявляется

в обнулении его триггеров, что должно

быть предотвращено. Изменение состояний

триггеров в процессе работы прямого

счётчика удобно проиллюстрировать

табл. 14.2.1.

Таблица 14.2.1