С dc инхронный d триггер со статическим управлением. Latch – прозрачная защелка.

В ыход

Q

такого D

триггера по сигналу на C

входе принимает то же

ыход

Q

такого D

триггера по сигналу на C

входе принимает то же

& & & & D C Q

1

T

с остояние

что и на D

входе. Получается из синхронного RS

триггера при объединении через инвертор

R

и S

входов. D

– DATA

– данные, иногда DELAY

– задержка, т.к. сигнал завершается до

С. При С=0 триггер находится в режиме

хранения, т.е. изменения сигнала на D

входе не влияет на Q

выход триггера. При С=1 этот D

триггер прозрачен для сигнала на D

входе: этот сигнал сразу же появляется

на Q

выходе как только появится на D

входе. Прозрачность триггера может

привести к срабатыванию его от помех,

как например, в предыдущем разделе,

прозрачный RS

триггер сработал от импульса помехи в

конце

диаграммы.

Минимизированная для ТТЛ схема D

триггера имеет некоторую склонность к

ложным срабатываниям, если фронт сигнала

на С входе 1-0 слишком пологий, а порог

срабатывания D1

выше D2.

такая ситуация называется гонками по

входу.

остояние

что и на D

входе. Получается из синхронного RS

триггера при объединении через инвертор

R

и S

входов. D

– DATA

– данные, иногда DELAY

– задержка, т.к. сигнал завершается до

С. При С=0 триггер находится в режиме

хранения, т.е. изменения сигнала на D

входе не влияет на Q

выход триггера. При С=1 этот D

триггер прозрачен для сигнала на D

входе: этот сигнал сразу же появляется

на Q

выходе как только появится на D

входе. Прозрачность триггера может

привести к срабатыванию его от помех,

как например, в предыдущем разделе,

прозрачный RS

триггер сработал от импульса помехи в

конце

диаграммы.

Минимизированная для ТТЛ схема D

триггера имеет некоторую склонность к

ложным срабатываниям, если фронт сигнала

на С входе 1-0 слишком пологий, а порог

срабатывания D1

выше D2.

такая ситуация называется гонками по

входу.

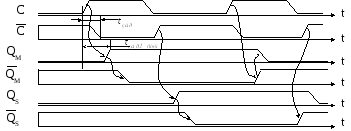

Синхронный двухступенчатый jk триггер.

1.При J=0 (какой-либо из J1, J2, или J3=0, J1*J2*J3=0) и К=0 (К1К2К3=0) сигнал лог 1 на С входе не может открыть входные ЛЭ, И-НЕ триггер не меняет связи состояния – режим хранения.

2.При J=1, К=0 первый RS триггер М переключается в 1 (QM=1) при поступлении на С вход лог 1 (фронт С01), а второй RS триггер S переключателей в 1 (QS=1) при фронт С10 [режим установка].

3 .

При J=0,

K=1

QM→0

по С01,

QS→0

по С10.

[сброс]

.

При J=0,

K=1

QM→0

по С01,

QS→0

по С10.

[сброс]

4. При J=K=1

сигналы с выходов

![]() открывают

для С именно тот ЛЭ И-НЕ,

пройдя через который он переключает

триггер в противоположное положение в

два этапа: сначала при С01

переключается QM,

а затем по С10

– QS

[счетный режим, или Т режим].

открывают

для С именно тот ЛЭ И-НЕ,

пройдя через который он переключает

триггер в противоположное положение в

два этапа: сначала при С01

переключается QM,

а затем по С10

– QS

[счетный режим, или Т режим].

Триггер непрозрачен, т.е. сигналы, поступающие на входы J и K не проходят сразу же на выход QS триггера, как это происходит в синхронных RS и D триггерах, рассмотренных ранее.

|

C |

C |

J |

K |

Qn+1 |

|

x |

x |

0 |

0 |

Qn |

|

|

|

0 |

1 |

0 |

|

↓ |

|

1 |

0 |

1 |

|

|

|

|

|

Qn |

В этом триггере видны параллельные пути распространения фронтов сигнала со входа С, которые являются причиной гонок. Чтобы микросхемы таких JK триггеров не давали сбоев, в них опасность гонок ликвидируется за счет или нормирования минимальной задержки М ступени, или специально введенный гарантированный разницы в порогах срабатывания инвертора и входных схем И ступени М. Делают так, чтобы инвертор переключался при более низком уровне С- сигнала, чем входные схемы 6И, и тогда нужная последовательность срабатывания инвертора и М ступени обеспечивается за счет конечной длительности фронтов С сигнала. Инвертор реагирует на фронт С01 сигнала раньше, а на его С10 позже, чем это делает М-ступень.

↓

↓ ↓

↓