МУ к КП

.pdfФЕДЕРАЛЬНОЕАГЕНТСТВО ПООБРАЗОВАНИЮ РЯЗАНСКИЙГОСУДАРСТВЕННЫЙРАДИОТЕХНИЧЕСКИЙУНИВЕРСИТЕТ

КАФЕДРА ЭВМ

А.В.Кистрин

Схемотехника ЭВМ

Методические указания к курсовому проектированию

Рязань 2011

Задание.

Общая часть задания. Разработать устройство, выполняющее заданную обработку данных.

В памяти, начиная с адреса 00, записан массив из 16 однобайтовых чисел со знаком, представленных в дополнительном коде. Подсчитать количество чисел, удовлетворяющих условию х1, результат записать в память по адресу 1016. Числа, удовлетворяющие условию х2, модифицировать и записать в память по исходному адресу.

Разделы проекта.

1.Алгоритм решения задачи. Структура устройства.

2.Архитектура и функциональная схема операционного устройства.

3.Граф управляющего автомата.

4.Синтез управляющего автомата с жесткой логикой. Разработка схемы

5.Моделирование и тестирование управляющего автомата.

6.Разработка схемы, моделирование и тестирование устройства.

7.Разработка второго варианта устройства с описанием элементов на языке Verilog

Индивидуальные задания. В соответствии с номером бригады определяются варианты для условий х1, х2, и для операции модификации числа

Группа *40,

|

Бригада |

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

12 |

|

|

|

х1 |

|

0 |

|

7 |

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

|

0 |

|

7 |

|

6 |

|

5 |

|

|

|

х2 |

|

1 |

|

2 |

|

3 |

|

0 |

|

1 |

|

4 |

|

5 |

|

2 |

|

3 |

|

4 |

|

5 |

|

4 |

|

|

|

Модиф. |

|

0 |

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

12 |

|

|

Группа *41 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Бригада |

|

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

12 |

|

|

|

х1 |

|

0 |

|

7 |

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

|

0 |

|

7 |

|

6 |

|

5 |

|

|

|

х2 |

|

|

1 |

|

2 |

|

3 |

|

0 |

|

1 |

|

4 |

|

5 |

|

2 |

|

3 |

|

4 |

|

5 |

|

4 |

|

|

Модиф. |

|

12 |

|

11 |

|

10 |

|

9 |

|

8 |

|

7 |

|

6 |

|

4 |

|

3 |

|

2 |

|

1 |

|

0 |

|

|

|

Варианты для Х1. Условие Х1 = 1 для следующих чисел: |

|||

0 |

Число >0 |

4 |

|

Сумма бит в старшей тетраде четна |

1 |

Число <0 |

5 |

|

Сумма бит в старшей тетраде нечетна |

2 |

Число в старшей тетраде>7 |

6 |

|

В старшей тетраде константа 5 |

3 |

Число в старшей тетраде<7 |

7 |

|

В старшей тетраде константа 7 |

|

Варианты для Х2. Условие Х2 = 1 для следующих чисел: |

|||

0 |

число кратно 2 |

|

3 |

число не кратно 4 |

1 |

число кратно 4 |

|

4 |

Сумма бит в младшей тетраде четна |

2 |

число не кратно 2 |

|

5 |

Сумма бит в младшей тетраде нечетна |

|

Варианты модификации данных: |

|

|

|

0) представить число в обратном коде; |

|

6) |

прибавить к числу 1; |

|

1) логическая операция И с маской 5Ah; |

|

7) |

прибавить к числу 2; |

|

2) логическая операция ИЛИ с маской A6h; |

|

8) |

представить число в дополнительном коде; |

|

3) логическая операция сумма по модулю 2 с |

9) |

логический сдвиг числа влево; |

||

маской 0Fh; |

|

10) логический сдвиг числа вправо; |

||

4) арифметический сдвиг числа вправо; |

|

11) циклический сдвиг влево; |

||

5) поменять местами тетрады в байте; |

|

12) циклический сдвиг влево; |

||

2

1. Структура цифрового устройства обработки данных

|

|

|

Входные |

Выходные |

|

Цифровое устройство обработки данных (процессор) |

|

|

|

|

|

данные |

данные |

|

можно представить в виде системы, состоящей из операци- |

|

|

|

|

|

|

|

онного устройства (ОУ) и управляющего устройства (УУ) |

|

|

|

|

|

|

|

(Рис.1). Операционное устройство принимает входные дан- |

КОП |

|

|

Операционное |

ные, выполняет их обработку в соответствии с кодом опера- |

|||

|

|

|

|

устройство |

ции (КОП) и формирует выходные данные. Оно содержит |

||

|

|

|

|

|

|

|

функциональные блоки, выполняющие обработку входных |

|

|

|

|

Y |

X |

||

|

|

|

|

данных, предусмотренную заданным алгоритмом, и выдачу |

|||

|

|

|

|

|

|

|

|

|

|

|

|

Управляющее |

выходных данных. Управляющее устройство генерирует по- |

||

|

|

|

|

следовательность управляющих сигналов Y на основе анали- |

|||

|

|

|

|

устройство |

|||

|

|

|

|

за состояния устройства и признаков результатов X, посту- |

|||

|

|

|

|

|

C |

||

|

|

|

|

|

пающих из ОУ. Моменты выдачи управляющих сигналов оп- |

||

|

|

|

|

|

|

|

|

|

|

|

Рис.1. Устройство |

|

ределяют импульсы частоты синхронизации C. |

||

|

|

|

обработки данных |

|

Любая операция, выполняемая в ОУ, описывается |

||

|

|

|

|

|

|

|

микропрограммой, реализуемой одной, или несколькими |

|

|

|

|

|

|

|

|

микрокомандами. Интервал времени, отводимый на выполнение микрокоманды, равный периоду частоты C, называется тактом.

In |

|

|

КС |

|

|

|

КС |

|

|

|

КС |

Out |

|||

D Q |

|

|

D Q |

|

|

D Q |

|||||||||

|

|

|

|

|

|

|

|

||||||||

C |

|

C |

|

|

|

|

C |

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рис.2. Принцип однофазной синхронизации

При однофазной синхронизации (Рис. 2) триггеры выполняют задержку обрабатываемых данных на один такт, а все комбинационные схемы КС за это время должны выполнить необходимую обработку. Длительность такта выбирается по самой продолжительной микрокоманде.

2. Архитектура операционного устройства

|

|

|

|

|

|

|

0 |

7 |

0 |

Архитектура, или регистровая модель |

|

|

|

|

|

7 |

|

|

операционного устройства отображает блоки, |

||||

|

|

|

|

||||||||

|

00 |

|

|

|

|

|

|

Счетчик адреса |

способные воспринимать, хранить и выдавать |

||

|

|

|

|

|

|

Память |

|

|

|

слово информации. Такими элементами явля- |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

7 |

0 |

ются регистры и память. Связи между элемен- |

|

|

|

|

|

|

|

|

|

|

тами и комбинационные схемы, выполняющие |

||

|

FF |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

Регистр данных |

|||

|

|

|

|

|

|

|

|

|

логические операции, в архитектуре не изобра- |

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

0 |

жаются. Они учитываются при составлении |

|

|

|

|

|

|

|

|

|

функциональной схемы. |

|||

|

|

|

|

|

|

|

|

|

Счетчик чисел |

Выберем параметры элементов архитек- |

|

|

|

|

|

|

|

|

|

|

|

|

туры применительно к заданиям проекта. |

|

|

|

|

|

Рис.3. |

Регистровая модель ОУ |

|

Память. Для хранения массива исходных |

|||

данных необходимо оперативное запоминающее устройство ОЗУ, с разрядностью – 8 бит, емкостью – не менее 17 ячеек. Емкость может быть увеличена с учетом потребностей других устройств, работающих в системе совместно с разрабатываемым устройством.

данных необходимо оперативное запоминающее устройство ОЗУ, с разрядностью – 8 бит, емкостью – не менее 17 ячеек. Емкость может быть увеличена с учетом потребностей других устройств, работающих в системе совместно с разрабатываемым устройством.

Счетчик адреса. Для хранения адреса ячеек памяти необходим счетчик адреса разрядности К, соответствующей равенству 2К=N, где N – емкость памяти. При N=256 получим К=8.

3

Регистр данных. Данные, читаемые из ОЗУ необходимо фиксировать в регистре с разрядностью 1 байт, и сохранять на время, необходимое для выполнения их математической обработки. Блочная память, используемая в ПЛИС, имеет, как правило, буферный регистр данных.

Счетчик чисел. По условию задачи в ОА необходимо выполнить подсчет количества чисел, удовлетворяющих заданному условию, при этом максимальное число равно 16. Учитывая, что результат подсчета будет записываться в память с байтовой организацией, выбираем счетчик с разрядностью 8 бит. На счетчик чисел необходимо подать сигналы, обеспечивающие режимы сброса и инкремента.

|

|

|

|

|

Сброс |

|

|

|

q0 |

(y0) |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Чтение |

q1 |

(y1) |

||||||||

|

|

|

|

|

|

числа |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||||||

|

Формирование |

q2 |

(y2) |

||||||||||||

|

|

признаков |

|

|

|

||||||||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

Х1 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||||||

1 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Инкремент |

q3 |

(y3) |

|||||||||||

|

|

|

счетчика |

|

|

|

|||||||||

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Х2 |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||||

1 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Модифик. |

q4 |

(y4) |

|||||||||||

|

|

|

и запись |

|

|

|

|||||||||

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Инкремент |

q5 |

(y5) |

|||||||||||

|

|

|

|

|

адреса |

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|||||||||||

|

Формирование |

q6 |

(y6) |

||||||||||||

|

|

признака |

|

|

|

||||||||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Х3 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||||

1 |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

Запись |

|

q7 |

(y7) |

|||||||

|

|

количества |

|

|

|

||||||||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

q0 |

(y0) |

|

|

|

|

|

Конец |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4. Схема алгоритма

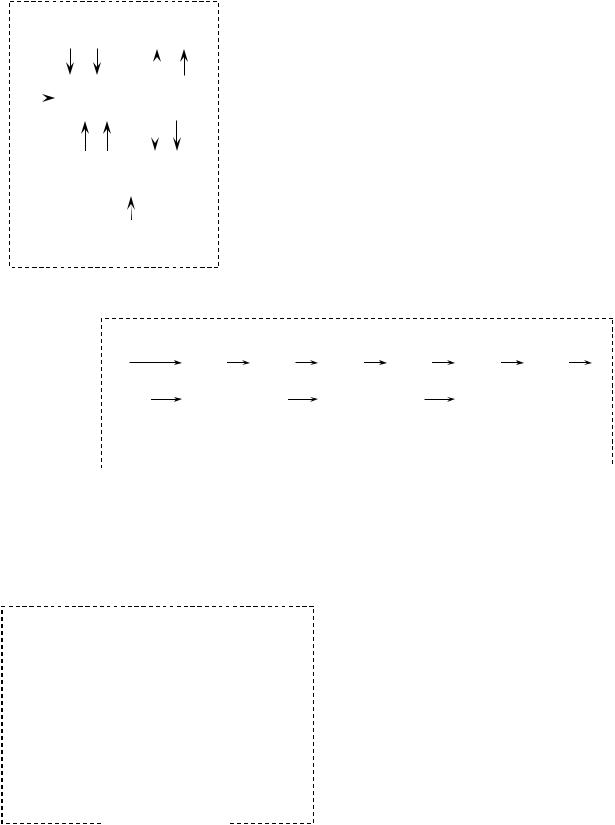

3. Алгоритм решения задачи.

Обобщенная схема алгоритма для задач проекта приведена на рис. 4. Каждой операторной вершине алгоритма при выполнении будет соответствовать один такт,

вкотором выдается управляющий сигнал (команда). Начальной вершине q0 соответствует сигнал начального сброса Y0. Микрооперации начального сброса регистра адреса и счетчика чисел объединены в одну микрокоманду, так как эти действия выполняются разными устройствами и могут быть выполнены одновременно.

По команде Y1 выполняется чтение кода числа из памяти в регистр данных, в котором этот код будет сохраняться при выполнении его обработки. Если устройство памяти имеет асинхронный вывод и буферный регистр на выходе, то сигнал Y1 на устройство памяти не подается, но такт чтения числа необходим.

ТактY2 предусмотрен для задержки выполнения алгоритма на 1 такт, что является гарантией готовности данных, прочитанных из памяти.

Проверка условия Х1 определяет необходимость инкремента счетчика чисел, если условие выполняется.

При Х1=0 инкремент счетчика не выполняется, соответствующая команда Y3 не выдается и такт попускается.

Условие X2 определяет необходимость выполнения модификации числа и записи его в память по исходному адресу по команде Y4.

Такт Y4 необходим для записи числа в память, а для выполнения модификации, которую выполняет простейшее АЛУ комбинационного типа с высоким быстродействием, дополнительный такт не нужен.

Втакте Y5 содержимое счетчика адреса увеличивается на 1. выполняется подготовка к циклической обработке следующего числа. Команда Y6 - пропуск одного такта для формирования признака Х3.

Условие выхода из цикла обработки чисел Х3 принимает значение 1, когда адрес, полученный после инкремента, выходит за диапазон адресов, в которых хранятся числа массива.

Втакте Y7 выполняется запись кода, полученного

всчетчике чисел, в память. Работа алгоритма заканчивается.

4

4. Функциональная схема операционного устройства

Функциональная схема (рис.5.) отображает набор функциональных устройств, связи и управляющие сигналы. Набор функциональных узлов ОУ производится в соответствии с заданием и архитектурой.

Память имеет два режима работы: чтение и запись. Выбор режима выполняет управляющий сигнал WE (Write Enable), равный «0» для режима чтения и «1» – для записи. ОЗУ имеет 8-разрядные шины данных - данных записиDI (Data Input) и данных чтенияDO (Data Output). Шина адреса A имеет 9 разрядов, что обеспечивает адресное пространство ОЗУ, равное 512 байт.

Счетчик адреса 8-разрядный, должен обеспечивать режимы начального сброса сигналом Y0 и инкремента адреса (+1) сигналом Y5. Код адреса подается также на комбинацион-

|

|

|

|

|

|

x3 |

|

|

|

|

|

we |

|

|

|

|

|

x1 |

|

x2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

y0 |

|

|

Счетчик |

|

|

Память |

|

DO |

|

|

|

АЛУ |

|

|

|||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

y5 |

|

|

адреса |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

DI |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y0 |

|

|

Счетчик |

|

N |

|

|

Мульти- |

|

|

|

|

|

D |

|

|

|

|

|||||||

|

y3 |

|

|

|

чисел |

|

|

|

|

плексор |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

y4 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5. Функциональная схема ОУ |

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ную схему формирования признака конца массива Х3. В общем случае необходим режим параллельной загрузки в счетчик фиксированного адреса, по которому следует записать код из счетчика чисел. В задании на проектирование предусмотрен упрощенный вариант, когда запись кода производится в ячейку, адрес которой на 1 больше последнего адреса массива.

Регистр данных– 8-разрядный, он входит в состав блока памяти. Запись данных в регистр - асинхронная, происходит после подачи адреса. Очистка регистра не требуется, она произойдет в результате записи.

Счетчик чисел. Разрядность – 8, хотя максимальное количество чисел 16. Выбор разрядности счетчика обусловлен байтовой организацией памяти. На счетчик чисел поданы сигналы, обеспечивающие режимы сброса Y0 и инкремента Y3.

Мультиплексор – комбинационная схема, управляемая сигналом Y4. При Y4=0 (по умолчанию) в качестве данных записи подключается выход АЛУ, а при Y4=1 – код счетчика чисел N.

АЛУ – комбинационная схема, выполняющая модификацию данных, поступающих по шине DO и выдачу результата на шину D. В блоке АЛУ также содержится формирователь признаков числа Х1 и Х2, входами которого являются биты шины DO.

Преобразование данных в АЛУ выполняется постоянно и безусловно. На шине D всегда присутствуют данные, полученные путем модификации сигналов с шины DO. Модифицированные данные при Х2=1 записываются в память, а при Х2=0 - не используются.

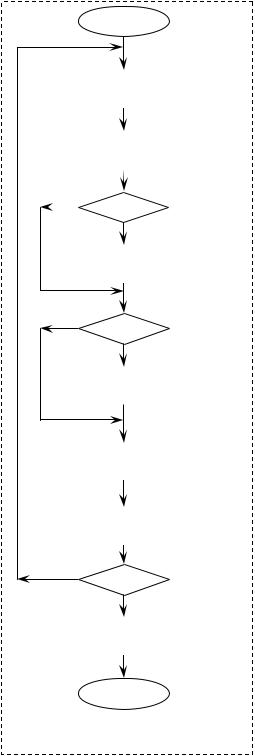

5. Синтез управляющего автомата

Цифровой автомат – это устройство, которое содержит элементы памяти и имеет некоторое конечное число внутренних состояний Q (Рис.6). Под воздействием тактовых импульсов C и входных сигналов X цифровой автомат переходит из одного состояния в другое и выдает выходные сигналы Y.

5

Существует два основных типа управляющих автоматов. В управляющем автомате с жесткой, или схемной логикой состояния фиксируются с помощью элементов памяти, а

С |

Схемы |

D |

|

Q |

|

Y |

x1 |

формирования |

Память |

Дешифратор |

|||

x2 |

функций |

|

|

|

состояний |

|

x3 |

переходов |

|

|

|

|

|

Рис.6. Функциональная схема УА

управляющие сигналы формирует набор комбинационных схем. Автоматы данного типа обеспечивает наиболее высокое быстродействие. Второй тип автомата – с программируемой логикой является более универсальным, так как наборы управляющих сигналов для каждой микрокоманды хранятся в памяти микрокоманд и могут быть модифицированы. В зависимости от способа описания поведения автомата различают автоматы Мили и Мура. Автомат Мура имеет, как правило, большее количество состояний, чем эквивалентный автомат Мили,

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

однако обеспечивает более надежную синхрониза- |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

цию устройств с памятью. |

||||

|

|

|

|

|

|

|

|

|

|

q0 |

|

|

|

|

|

|

q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рассмотрим способ построения автомата Му- |

||||

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ра. В автомате Мура за состояния принимают испол- |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

няемые операторы графа, выходные сигналы при |

|||||

|

q7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

q2 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

этом получаются как функции состояний. В автома- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

те Мура каждому состоянию графа qJ соответствует |

|||

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

выходной сигнал yJ . Представим микропрограмму |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

разрабатываемого устройства в виде графа. Каждой |

|

|

q6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

q3 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

x1x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

микрокоманде ставится в соответствие состояние ав- |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x2 |

|

томата, отображаемое вершиной графа. |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Начало и конец микропрограммы отобража- |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

q5 |

|

|

|

|

|

|

|

|

|

|

q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x2 |

|

|

|

|

|

|

ются начальным состоянием q0. В результате полу- |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

чим циклический автомат, допускающий повторение |

|

|

|

Рис.7. Граф управляющего |

рабочего цикла. Условия перехода из одного состоя- |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

автомата Мура |

|

|

|

|

|

|

|

|

|

|

|

|

|

ния в другое записываются на дугах графа в виде |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

конъюнкций входных сигналов, принимающих еди- |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 1. |

ничное значение, когда данный переход происхо- |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

дит. При безусловном переходе дуга графа отмеча- |

|||||||||||||

|

QT (YT) |

|

QT+1 |

|

|

|

|

|

X |

|

D2D1D0 |

ется константой 1. |

||||||||||||||||||||||||||||

|

|

|

Q7 |

|

|

Q0 |

|

|

|

|

1 |

|

|

|

0 0 0 |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема управляющего автомата должна со- |

|||||||||||||||||||||||||||

|

|

|

Q0 |

|

|

Q1 |

|

|

|

|

1 |

|

|

|

0 0 1 |

|

держать N триггеров, при этом 2 N ≥ n, где n – ко- |

|||||||||||||||||||||||

|

|

|

Q6 |

|

|

Q1 |

|

|

|

|

/X3 |

|

0 0 1 |

|

личество состояний автомата. Для рассматриваемо- |

|||||||||||||||||||||||||

|

|

|

Q1 |

|

|

Q2 |

|

|

|

|

1 |

|

|

|

0 1 0 |

|

го примера N=3. При построении схем на ПЛИС в |

|||||||||||||||||||||||

|

|

|

Q2 |

|

|

Q3 |

|

|

|

|

|

X1 |

|

0 1 1 |

|

качестве элемента памяти автомата предпочтение |

||||||||||||||||||||||||

|

|

|

Q2 |

|

|

Q4 |

|

|

|

/X1 X2 |

|

1 0 0 |

|

отдают D-триггеру. В простейшем случае состояния |

||||||||||||||||||||||||||

|

|

|

Q3 |

|

|

Q4 |

|

|

|

|

|

X2 |

|

1 0 0 |

|

кодируются соответствующими двоичными кодами: |

||||||||||||||||||||||||

|

|

|

Q2 |

|

|

Q5 |

|

|

/X1 /X2 |

|

1 0 1 |

|

q0-000, q1-001, и т.д. |

|||||||||||||||||||||||||||

|

|

|

Q3 |

|

|

Q5 |

|

|

|

|

/X2 |

|

1 0 1 |

|

Функция переходов для D-триггера имеет |

|||||||||||||||||||||||||

|

|

|

Q4 |

|

|

Q5 |

|

|

|

|

1 |

|

|

|

1 0 0 |

|

вид: Q(t+1)=D(t). Состояние, в которое переходит |

|||||||||||||||||||||||

|

|

|

Q5 |

|

|

Q6 |

|

|

|

|

1 |

|

|

|

1 1 0 |

|

триггер в (t+1)-м такте определяется входным сиг- |

|||||||||||||||||||||||

|

|

|

Q6 |

|

|

Q7 |

|

|

|

|

|

X3 |

|

1 1 1 |

|

налом в предыдущем (t) такте. |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

По графу составим описание микропрограммы в форме таблицы 1, где: Q(t) – исходное состояние автомата; Q(t+1) – следующее состояние автомата; X– условия перехода; D2 D1 D0 – двоичный код, подаваемый на входы

По графу составим описание микропрограммы в форме таблицы 1, где: Q(t) – исходное состояние автомата; Q(t+1) – следующее состояние автомата; X– условия перехода; D2 D1 D0 – двоичный код, подаваемый на входы

6

триггеров, равный коду состояния Q(t+1), в которое должен перейти автомат в следующем такте. Таблица 1 упорядочена по значениям Q(t+1).

Составим логические уравнения, описывающие формирование сигналов переходов триггеров D.

Каждому состоянию QJ, отображенному 3-разрядным двоичным кодом, однозначно соответствует сигнал YJ, представленный в виде 8-разрядного единичного кода «1 из N». При формировании функций переходов, подаваемых на входы D, целесообразно использовать сигналы Y. Анализируя столбцы таблицы для d0, d1, d2, составим функции переходов триггеров.

D0 Y0 Y6 X3 Y2 X1 Y2 X1 X2 Y3 X2 Y4 Y6 X3

D1 Y1 Y2 X1 Y5 Y6 X3

D2 Y2 X1 X2 Y3 X2 Y2 X1 X2 Y3 X2 Y4 Y5 Y6 X3

Выражения для D0 и D2 можно упростить, используя тождество A (B B) A. Уравнения для функций переходов триггеров, использованные при составлении схе-

мы, примут вид:

D0 Y2 X1 X2 Y0 Y4 Y6 Y2 X1 Y3 X2;

D1 Y2 X1 Y1 Y5 Y6 X3;

D2 Y2 X1 Y3 Y4 Y5 Y6 X3;

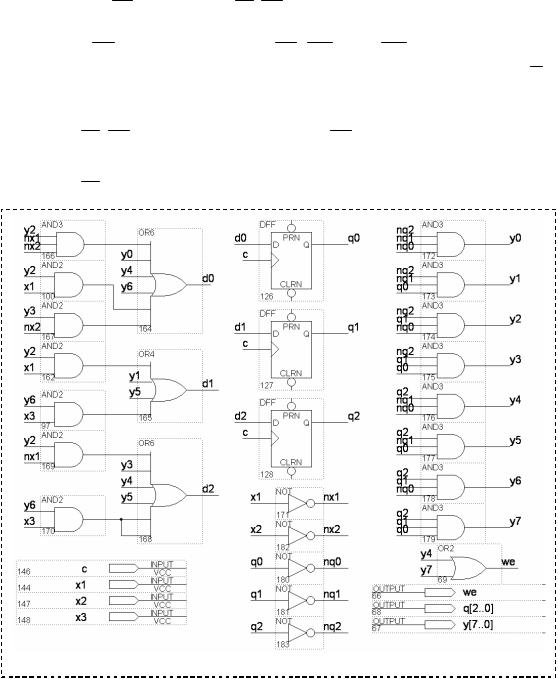

Рис. 8. Схема управляющего автомата

Кроме сигналов Y управляющий автомат должен выдать сигнал управления записью в память WE. В соответствии с алгоритмом этот сигнал соответствует дизъюнкции:

WE Y4 Y7

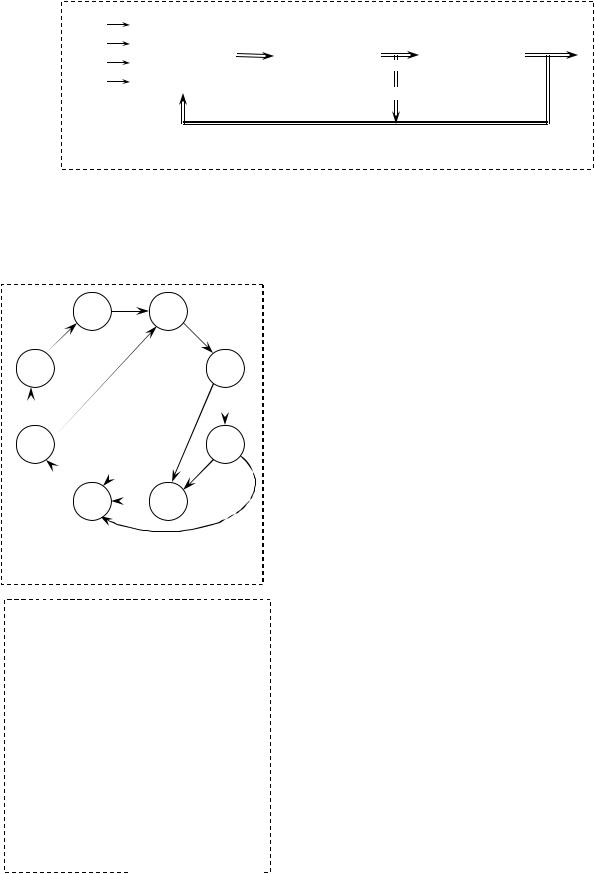

6. Тестирование управляющего автомата.

Для проверки правильности функционирования управляющего автомата по графу составим таблицу изменений состояний графа при всех возможных комбинациях управляющих

7

сигналов и проверяют чередование этих состояний по временным диаграммам (Рис. 9). Подчеркнуты состояния, повторяющиеся циклически. Последовательность состояний, формируемая при х1=1, х2=1 и х3=0 (строка выделена) соответствует основному циклу алгоритма, и будет использоваться при отладке операционного устройства

|

|

|

Таблица 2. |

х3 х2 |

х1 |

Q |

Y |

0 0 0 |

0-1-2-5-6-1-2-5-6-1 |

01-02-04-20-40-02-04-20-40- |

|

0 0 1 |

0-1-2-3-5-6-1-2-3-5-6-1 |

01-02-04-08-20-40-02-04-08-20-40- |

|

0 1 0 |

0-1-2-4-5-6-1-2-4-5-6-1 |

01-02-04-10-20-40-02-04-10-20-40- |

|

0 1 1 |

0-1-2-3-4-5-6-1-2-3-4-5-6-1 |

01-02-04-08-10-20-40-02-04-08-10-20-40- |

|

1 0 0 |

0-1-2-5-6-7-0-1-2-5-6-7- |

01-02-04-20-40-80-01-02-04-20-40-80 |

|

1 0 1 |

0-1-2-3-5-6-7-0-1-2-3-5-6-7- |

01-02-04-08-20-40-80-01-02-04-08-20-40-80 |

|

1 1 0 |

0-1-2-4-5-6-7-0-1-2-4-5-6-7- |

01-02-04-10-20-40-80-01-02-04-10-20-40-80 |

|

1 1 1 |

0-1-2-3-4-5-6-7-0-1-2-3-4-5-6-7 |

01-02-04-08-10-20-40-80-01-02-04-08-10-20-40- |

|

При моделировании схемы в программе имитатора значения сигналов Q и Y, объединенных в шины, удобно выводить в виде 16-ричных чисел. Представление этих сигналов будет различаться, так как сигналы Q представлены двоичными кодами, а сигналы Y – унарными (1 из «N»). Соответствие кодов приведено в таблице 2.

Необходимо также проверить правильность выработки сигнала WE.

На рис. 8 приведена схема управляющего автомата, полученного по логическим уравнениям без использования минимизации и результаты ее моделирования при х1=х2=х3=1.

Схему можно упростить, если использовать минимизацию, а также выполнить ряд условий при проектировании.

Рис. 9. Результаты моделирования управляющего автомата

1 При нумерации состояний графа вершинам, в которые входит несколько дуг, следует присваивать номера, двоичные коды которых содержат наименьшее количество единиц.

2 Логические уравнения следует минимизировать по картам Карно.

3. Логические элементы, формирующие повторяющиеся конъюнкции могут быть частично исключены.

7. Разработка схемы и моделирование устройства

Процесс разработки и моделирования сложных схем разбивают на отдельные этапы, наращивая сложность устройства. Для разрабатываемого устройства выполним 3 этапа.

1 этап – работа управляющего автомата совместно с памятью.

На первом этапе необходимо создать схему с именем, например «Device1», которая содержит управляющий автомат, счетчик адреса и блок памяти.

Управляющий автомат будет запускать устройства схемы посредством управляющих сигналов. Формирование признаков х1, х2, х3, которое пока не выполнено, не проверено, и может сопровождаться ошибками, необходимо временно исключить, подключая х1 и х2 к

8

метке V (что соответствует логической 1), а х3 к метке G (логический 0). Такое сочетание признаков соответствует основному циклу алгоритма (подчеркнут в таблице 3).

На схеме также следует поместить счетчик адреса и блок памяти.

Доступные типы счетчиков описаны в Help/Max+plus II Table of Contents/Graphic & Symbol Editors/macrofunctions/Counters. Для проекта выбираем 8-разрядный счетчик из биб-

лиотеки макрофункций (mf).

Для проектирования устройства, содержащего память необходимо выбрать ПЛИС, в которой необходимые модули физически существуют. Можно выбрать, например, из меню семейство: Assign/Device/Device Famili/FLEX10K.

Модули памяти размещены в библиотеке \mega_LPM (библиотека параметризируемых модулей мега-функций). При вводе символа параметризируемого модуля отображается диалоговое окно настройки модуля (Edit Ports/Parameters). Описание модуля можно получить, активизируя кнопку Help окна настройки.

Рис. 10. Первый этап моделирования устройства

В зависимости от того, включена или нет опция Show Parameters меню Options, символ параметризируемого модуля будет отображаться либо с окном введенных параметров (рис. 10), либо без него. Если символ отображается с окном параметров, то для редактирования параметров следует: поместить курсор в окно параметров; двойным щелчком по левой кнопке манипулятора активизировать диалоговое окно настройки модуля; осуществить редактирование и подтвердить внесенные изменения (кнопка ОК).

Если символ отображается без окна параметров, то для редактирования параметров следует: поместить курсор на тело модуля; щелчком правой кнопки манипулятора вызвать контекстно-зависимое меню; выбрать команду Parameters, активизирующую диалоговое окно настройки модуля; осуществить редактирование и подтвердить внесенные изменения (кнопка ОК).

9

В устройстве использован блок памяти LPM_RAM_DQ с организацией 256 х 8. Он имеет 8-разрядную шину адреса (address), 8-

разрядные шины входных данных (data) и выходных данных

(q). Блок имеет также сигнал разрешения записи we (Write Enable) и входной сигнал тактовой частоты inclock, который используется для синхронизации параметров, отмеченных

Рис. 11. Схема АЛУ как «Registered».

После ввода схемы, компиляции, создания файла вре-

Рис. 12 Второй этап моделирования устройства

менных диаграмм и вызова симулятора, следует, не нажимая вызвать из меню Initialize/Memory Initialize. В открывшемся окне следует ввести тестовый массив данных и записать его в файл кнопкой Export File. Будет создан текстовый файл с расширением .mif, его

10