- •Схемотехника эвм Методические указания к курсовому проектированию

- •1. Структура цифрового устройства обработки данных

- •2. Функциональная схема операционного устройства

- •3. Разработка алгоритма

- •4. Синтез управляющего автомата

- •5. Тестирование управляющего автомата

- •6. Разработка алу и счетчиков

- •6. Разработка принципиальной схемы устройства

- •7. Моделирование устройства

5. Тестирование управляющего автомата

П

Тест

автомата х3

х2 х1 Q 0

0 0 0

0 1 0

1 0 0

1 1 1

0 0 1

0 1 1

1 0 1

1 1 0-1-4-1-4-1-4 0-1-2-4-1-2-4 0-1-3-4-1-3-4 0-1-2-3-4-1-2-3-4- 0-1-4-5-0-1-4-5-0- 0-1-2-4-5-0-1-2-4-5-0- 0-1-3-4-5-0-1-3-4-5-0- 0-1-2-3-4-5-0-1-2-3-4-5-0-

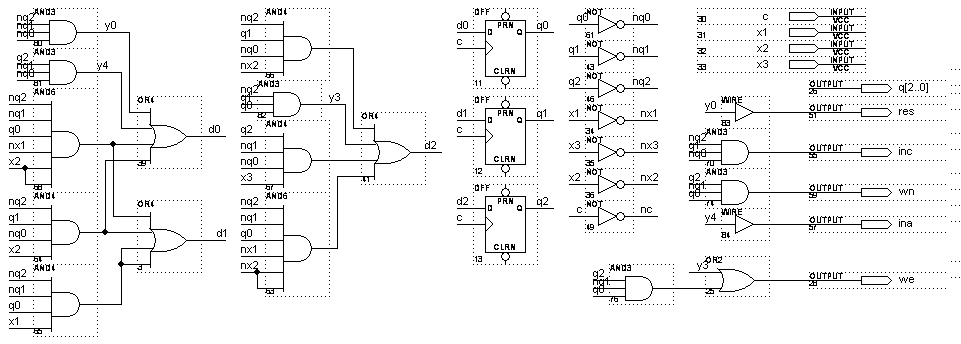

Рис.

7. Схема управляющего автомата

Для тестирования управляющего автомата необходимо по графу составить таблицу изменений состояний автомата при всех возможных комбинациях управляющих сигналов и выделить циклы повторяющихся состояний,. Последовательность состояний, формируемая при х1=1, х2=1 и х3=1 соответствует основному циклу алгоритма, в котором имеются все состояния. Такой цикли целесообразно использовать при отладке автомата и операционного устройства. Необходимо проверить формирование всех управляющих сигналов, соответствие алгоритму моментов их появления. После удачного тестирования автомата создайте символ.

В проекте необходимо представить иерархический проект управляющего автомата с вариантом описания на языке Verilog.

6. Разработка алу и счетчиков

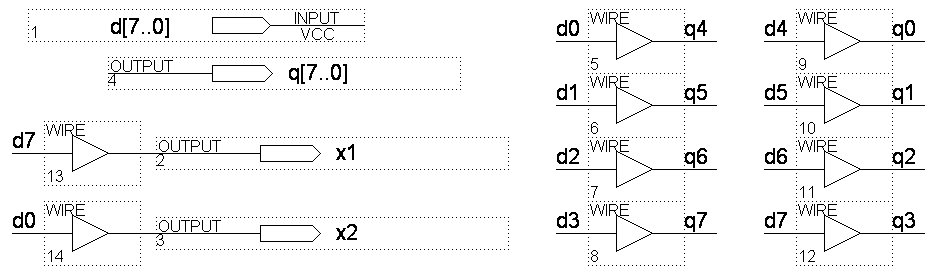

Рис

8. Схема АЛУ

//

5-разрядный счетчик module

count5 (c, en, clr, q); input

c, en, clr; output

[4:0] q; reg

[4:0] q; always

@(posedge c) if

(clr==0 & en==1) q=q+1'b1; else

if (clr==1) q=0; endmodule

В схеме АЛУ (Рис. 8) формируются признаки, и выполняется модификация данных. Ппризнак х1 = 1, если число отрицательное, признак х2 = 1, если число нечетно. Модификация данных - поменять местами тетрады в байте. Для АЛУ создан символ, который будет использован в схеме устройства.

Для построения счетчиков выбраны модули, описание на языке Verilog. В устройстве содержатся два счетчика, описания которых различаются разрядностью выходных сигналов. Счетчик адреса – 5-разрядный, а счетчик чисел – 8-разрядный. Счетчики должны срабатывать по фронту синхроимпульсов и иметь входы разрешения счета и синхронного сброса. Это необходимо для работы системы синхронизации. После компиляции каждого из описаний необходимо создать символы модулей «count5» и «count8».

6. Разработка принципиальной схемы устройства

Принципиальная схема устройства составляется по функциональной схеме (см. рис. 2), , в виде файла «device1.gdf». Вначале необходимо выбрать все модули устройства.

В качестве устройства памяти из библиотеки «mega_lpm» выбран параметризированный модуль «lpm_ram_dq», в котором имеются раздельные шины для входных и выходных данных. После выбора модуля открывается окно редактирования выводов и параметров модуля. В верхней части окна «Edit Ports/Parameters» необходимо для вывода «Outclock» выбрать «Unused – неиспользуемый», а для всех остальных выводов выбрать «Used».

Значения параметров «Parameter Value» необходимы следующие: «LPM_Address_Control» – «Registred» (синхронный, фиксируемый в регистре), «LPM_InData» – «none» (по умолчанию), «LPN_NumWords» – «none», «LPM_OutData» – «Unregistred» (асинхронный), «LPM_Width» – 8 (разрядность данных), «LPM_WidthAd» – 5 (разрядность адреса). В строке «LPM_File» впоследствии необходимо указать путь к файлу инициализации памяти. Выбранные сигналы определяют разрядность и емкость памяти, а также асинхронное чтение из памяти, при котором изменение данных на выходе происходит сразу же после смены адреса.

Мультиплексор для коммутации 8-разрядных шин на два направления выбран из библиотеки макрофункций «mf».

На схеме также содержится управляющий автомат, который будет запускать, и синхронизировать устройства схемы посредством управляющих сигналов.

Код адреса используется для формирования признака «x3» - конец массива. При х3 = 1 производится запись кода счетчика «n» в ячейку, адрес которой на 1 больше последнего адреса массива.

Шины на схеме имеют обозначения: q[2..0] – состояния автомата, a[4..0] – адрес памяти, do[7..0] данные с выхода памяти, d[7..0] – модифицированные данные с выхода АЛУ, n[7..0] – код счетчика чисел, удовлетворяющих условию х1, di[7..0] данные на входе памяти, предназначенные для записи.