- •Схемотехника эвм Методические указания к курсовому проектированию

- •1. Структура цифрового устройства обработки данных

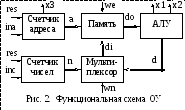

- •2. Функциональная схема операционного устройства

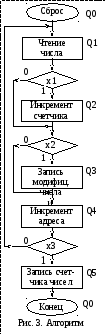

- •3. Разработка алгоритма

- •4. Синтез управляющего автомата

- •5. Тестирование управляющего автомата

- •6. Разработка алу и счетчиков

- •6. Разработка принципиальной схемы устройства

- •7. Моделирование устройства

1. Структура цифрового устройства обработки данных

Цифровое устройство обработки данных (процессор) при проектировании можно представить в виде системы, состоящей из операционного устройства (ОУ) и управляющего устройства (УУ) (Рис.1).

Операционное устройство содержит функциональные блоки, выполняющие обработку данных, предусмотренную заданным алгоритмом, и выдачу результата. Для хранения исходных данных и результатов используется память.

Управляющее устройство генерирует последовательность управляющих сигналов Y на основе анализа состояния устройства и признаков результатов X, поступающих из ОУ.

Моменты выдачи управляющих сигналов определяют импульсы частоты синхронизации C, период повторения которых называется тактом. При двухфазной синхронизации на ОУ и на.УУ подаются противофазные импульсы синхронизации. В этом случае моменты переключений элементов указанных устройств, определяемые фронтом импульсов, будут выполняться поочередно, совпадений импульсов не будет. Синхронизация должна обеспечить отсутствие ошибок, обусловленных гонками.

2. Функциональная схема операционного устройства

Функциональная схема операционного устройства (рис.2) отображает набор функциональных устройств, связи и управляющие сигналы.

П амять.

Для хранения массива исходных данных

необходимо оперативное запоминающее

устройство (ОЗУ), допускающее чтение и

запись, с разрядностью – 8 бит, емкостью

– не менее 17 ячеек. Емкость

может быть увеличена до 32 ячеек. Выбор

режима выполняет управляющий сигнал

«we»

(Write

Enable),

равный «0» для режима чтения и «1» – для

записи. ОЗУ имеет 8-разрядные шины данных

записи- «di»

(Data

Input)

и данных чтения- «do»

(Data

Output).

Шина адреса «a»

имеет 5 разрядов.

амять.

Для хранения массива исходных данных

необходимо оперативное запоминающее

устройство (ОЗУ), допускающее чтение и

запись, с разрядностью – 8 бит, емкостью

– не менее 17 ячеек. Емкость

может быть увеличена до 32 ячеек. Выбор

режима выполняет управляющий сигнал

«we»

(Write

Enable),

равный «0» для режима чтения и «1» – для

записи. ОЗУ имеет 8-разрядные шины данных

записи- «di»

(Data

Input)

и данных чтения- «do»

(Data

Output).

Шина адреса «a»

имеет 5 разрядов.

Счетчик адреса. Необходим для хранения адреса ячеек памяти. Его разрядность К должна соответствовать равенству 2К=N, где N – емкость памяти. При N=32 получим К=5. Счетчик должен обеспечивать режимы начального сброса сигналом res = 1 и инкремента адреса при сигнале ina = 1.

Счетчик чисел. По условию задачи в ОА необходимо выполнить подсчет количества чисел, удовлетворяющих заданному условию, при этом максимальное число равно 16. Учитывая, что результат подсчета будет записываться в память с байтовой организацией, выбираем счетчик с разрядностью 8 бит. Управляющие сигналы обеспечивают сброс при res = 1, и инкремент счетчика чисел при inc = 1.

Мультиплексор – комбинационная схема, управляемая сигналом wn. При сигнале wn = 0 в качестве данных для записи в память подключается выход АЛУ а при wn = 1 - код счетчика чисел N,

АЛУ – комбинационная схема, выполняющая модификацию данных, поступающих по шине «do» и выдачу результата на шину «d». В блоке АЛУ также содержится формирователь признаков числа «х1» и «х2», входами которого являются данные шины «do».

Преобразование данных в АЛУ выполняется постоянно и безусловно. На шине «d» всегда присутствуют модифицированные, которые записываются в память при х2=1, а при х2= 0 не используются.

3. Разработка алгоритма

Для решаемой задачи составлен алгоритм (рис. 3). Каждому исполняемому оператору алгоритма будет однозначно соответствовать состояние автомата (Q) и вершина графа. При определенных состояниях будут сформированы управляющие сигналы, обозначенные на функциональной схеме (Рис. 2).

Существуют различные системы кодирования состояний автомата. В примере рассмотрим простейший вариант, когда операторам алгоритма присваиваются номера из ряда чисел (012345).

Начальная состояние Q0 - сброс всех регистров и счетчиков устройства, для этого должен вырабатываться сигнал «res», который подается на счетчики.

При состоянии Q1 выполняется чтение кода числа из памяти в регистр данных. Если в устройстве памяти используется режим асинхронного вывода, то выходной сигнал для этого состояния не требуется.

П роверка

условия х1 определяет необходимость

инкремента счетчика чисел, если условие

выполняется.

роверка

условия х1 определяет необходимость

инкремента счетчика чисел, если условие

выполняется.

Состояние Q2 возникает при х1 = 1, если должен выполняьтся инкремент счетчика чисел, для этого формируется сигнал «inс».

Проверка условия х2 определяет необходимость записи модифицированного числа в память.

Такт Q3 необходим для выполнения модификации и записи числа в память, для этого необходим сигнал разрешения записи в память we = 1,

В такте Q4 содержимое счетчика адреса увеличивается на 1, для этого формируется сигнал инкремент адреса «ina». В результате выполняется подготовка к циклической обработке следующего числа.

Условие выхода из цикла обработки чисел x3 принимает значение 1, когда адрес, полученный после инкремента, выходит за диапазон адресов, в которых хранятся числа массива.

В такте q5 выполняется запись кода, полученного в счетчике чисел, в память. для этого необходимы сигналы we = 1 и wn = 1.

Конец алгоритма обозначен Q0, алгоритм допускает циклические повторения.