- •Микропроцессоры и микропроцессорные системы

- •Содержание

- •Введение

- •Успехи интегральной технологии и предпосылки появления микропроцессоров

- •Основные схемотехнологические направления производства микропроцессоров

- •Характеристики микропроцессоров

- •Поколения микропроцессоров.

- •Машина пользователя и система команд

- •Архитектура 16-разрядного микропроцессора

- •Система команд i8086

- •Общая структура мпс

- •Структура микропроцессора и интерфейсные операции

- •Внутренняя структура

- •Командный цикл микропроцессора.

- •Машинные циклы и их идентификация.

- •Реализация микропроцессорных модулей и состав линий системного интерфейса

- •Внутренняя структура

- •Машинные циклы i8086 в минимальном и максимальном режимах

- •Структура микропроцессорных модулей на базе микропроцессора i8086

- •Подсистема памяти мпс

- •Распределение адресного пространства

- •Регенерация динамической памяти

- •Подсистема ввода/вывода мпс

- •Подсистема параллельного обмена на базе буферных регистров

- •Контроллер параллельного обмена к580вв55

- •Последовательный обмен в мпс

- •Универсальныйпоследовательный приемопередатчик кр580вв51

- •Подсистема прерываний мпс

- •Внутренние и внешние прерывания

- •Функции подсистемы прерываний и их реализация

- •Контроллеры прерываний

- •Подсистема прямого доступа в память мпс

- •Контроллер прямого доступа в память к580вт57

- •Высокопроизводительный 32-разрядный контроллер пдп 82380

- •Архитектура контроллера 82380

- •Интерфейс с главным процессором.

- •Функции контроллера пдп

- •Программируемый контроллер прерываний

- •Программируемые интервальные таймеры

- •Контроллер регенерации динамического озу

- •Генератор с состоянием ожидания

- •Сброс центрального процессора

- •Размещение карты регистров

- •Интерфейс с микропроцессором

- •Сигналы сопряжения с микропроцессором 80386

- •Синхронизация шины контроллера 82380

- •Конвейеризация адресов

- •Организация мпс на базе секционированных бис

- •Арифметико-логические секции

- •Секции управления и устройства управления

- •Эволюция структур сфам.

- •Секции управления адресом микрокоманд серии к1804.

- •Организация управляющего автомата

- •Структура устройств обработки данных

- •Мпс с одно- и двухуровневым управлением

- •Расширение архитектурыAm2900

- •Базовый процессорный элемент к1804вм1

- •Организация основных блоков

- •Система инструкций

- •Однокристальные микроЭвм

- •Однокристальные микро-эвм к1816ве48/49/35

- •Структура омэвм

- •Элементы архитектуры омэвм

- •Порты ввода/вывода

- •Система команд омэвм

- •Расширение ресурсов омэвм

- •Однокристальная микроЭвм к1816ве51

- •Семейство однокристальных эвмmcs-51

- •Структура микро-эвм к1816ве51

- •Архитектурные особенности микро-эвм

- •Организация внутренней памяти данных.

- •Машинные циклы и синхронизация микро-эвм

- •Внешние устройства микро-эвм

- •Описание последовательного порта.

- •Таймеры-счетчики

- •Подсистема прерываний

- •Система команд

- •Системы проектирования и отладки мпс

- •Проблемы и особенности отладки мпс

- •Особенности отладки мпс на разных этапах ее существования.

- •Статические отладчики

- •Логические анализаторы

- •Сигнатурные анализаторы

- •Идея сигнатурного анализа

- •Оборудование сигнатурного анализа и требования к проверяемой схеме

- •Системы проектирования мпс

- •Внутрисхемные эмуляторы

- •Литература

Синхронизация шины контроллера 82380

Для организации внутренней синхронизации контроллера 82380 частота входного тактового сигнала CLK2 делится на два. Следовательно, для согласования работы контроллера 82380 и микропроцессора 80386 по времени требуется, чтобы частота CLK2 была равна удвоенной тактовой частоте микропроцессора. Во временной диаграмме внутреннего тактирования выделяются две фазы PHI1 и PHI2, причем длительность каждой этой фазы равна периоду сигнала CLK2. Фаза PHI1 используется для защелкивания внутренних данных; фаза PHI2 – для фиксации входных сигналов и установки внутренних сигналов. Контроллер 82380 формирует сигнал CPURST, гарантируя, что микропроцессор 80386 будет сброшен в фазе PHI1.

Такт шины характеризуется кратчайшим периодом времени какой-либо активности шины. Такту шины, иногда называемому Т-тактом, соответствует один период импульсов PHI1 в контроллере 82380 или эквивалентные по длительности два периода сигнала CLK2. Длительность цикла шины зависит от наличия на входе READY# сигнала низкого уровня. Каждый из шести типов циклов шины, определяемых комбинацией сигналов W/R#, D/C# и M/IO#, состоит из двух и более тактов шины.

Конвейеризация адресов

Конвейерная организация выдачи значений адресов на шину позволяет памяти и периферийным устройствам работать с ускорением на один такт ожидания по сравнению с обычным режимом работы шины. В основе такой организации лежит принцип формирования очередного значения адреса и сопутствующей ему комбинации управляющих сигналов в то время, когда ведущее устройство на шине ожидает подтверждения завершения текущего цикла шины. Если конвейерная организация выдачи адресов используется совместно с методом расслоения памяти, то могут быть получены обращения к памяти с нулевыми тактами ожидания. Контроллер 82380 поддерживает конвейеризацию адресов как в подчиненном режиме, так и в режиме ведущего устройства.

В зависимости от значения сигнала на входе NA# контроллер 82380 способен инициировать по поцикловому принципу либо конвейерную, либо неконвейерную работу в режиме ведущего устройства. Если уровень сигнала на линии NA# низкий, то это говорит о том, что запрашивается цикл шины конвейерного типа, и контроллер 82380 выставит адрес и сигналы, определяющие тип цикла шины, как только сформируется внутренний запрос шины. В подчиненном режиме по значениям сигналов на линиях READY# и ADS# локальной шины процессора контроллер 82380 определит запрос конвейеризации адресов и затребует от микропроцессора на один такт ожидания меньше (при этом предполагается, что функционирует генератор, управляющий формированием тактов ожидания). При обращении к внутренним регистрам 82380 в конвейерном режиме контроллер использует расширенную информацию о цикле адреса и о цикле шины вообще.

Организация мпс на базе секционированных бис

В развитие идеи микропроцессоров 3 поколения (см. раздел 1.4.3) достаточно широкое распространение получили т.н. комплекты секционированных микропроцессорных БИС, на базе которых разрабатываются МПС с разрядно-модульной организацией. Часто микропроцессоры такого типа называют многокристальными, имея в виду, что аппаратура МП располагается на нескольких связанных между собой кристаллах.

Однако, главной особенностью архитектуры многокристальных МП является раздельная организация операционного и управляющего автоматов и реализация операционной части в виде разрядных сечений.

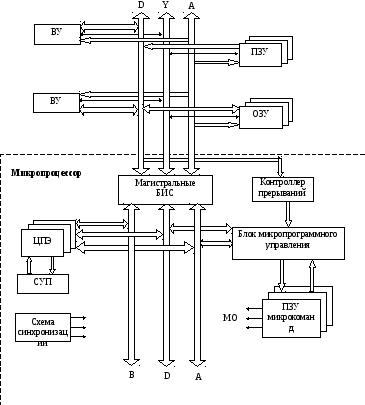

Р ис.10.63. Общая структура МПС

на секционированных БИС

ис.10.63. Общая структура МПС

на секционированных БИС

При этом пользователь (разработчик) получает две глобальные степени свободы:

возможность варьировать разрядность МПС за счет объединения различного числа БИС операционных устройств;

возможность реализации (почти) произвольной системы команд за счет изменения содержимого микропрограммного ПЗУ.

На Рис. 10 .63 приведена общая структура МПС с разрядно-модульной организацией. Процессор реализован на комплекте секционированных БИС, а память и ВУ - традиционным для однокристальных МП способом.

Для реализации МПС с разрядно-модульной организацией в составе комплектов микропроцессорных БИС выпускаются различные варианты арифметико-логических секций, секций управления и вспомогательных БИС (регистры, схемы ускоренного переноса, контроллеры прерываний и др.).