- •Особенности

- •Описание

- •Архитектура Virtex

- •Быстродействие

- •Описание архитектуры

- •Матрица Virtex

- •Блок ввода-вывода

- •Ввод сигнала

- •Вывод сигнала

- •Банки ввода-вывода

- •Конфигурируемый логический блок - КЛБ

- •Таблица Преобразования

- •Запоминающие элементы

- •Дополнительная логика

- •Арифметическая логика

- •Буферы с тремя состояниями

- •Блочная память (Block RAM)

- •Программируемая трассировочная матрица

- •Локальные связи

- •Трассировочные ресурсы общего назначения

- •Глобальные трассировочные ресурсы

- •Распределение сигналов синхронизации

- •Модули автоподстройки задержки (DLL)

- •Периферийное сканирование (ПС)

- •Регистры данных

- •Порядок бит регистра данных ПС

- •Идентификационные регистры

- •Включение ПС в проект

- •Система проектирования

- •Размещение проекта в кристалл

- •Верификация проекта

- •Конфигурирование кристалла в устройстве

- •Режимы конфигурирования

- •Подчиненный последовательный режим

- •Ведущий последовательный режим

- •Режим SelectMAP

- •Использование режима периферийного сканирования для конфигурирования Virtex

- •Последовательность конфигурации

- •Задержка конфигурирования

- •Последовательность вхождения в штатный режим работы

- •Формат потока конфигурационных данных

- •Обратное считывание

- •Характеристики семейства Virtex по постоянному току

- •Корпуса

- •Обозначение МС семейства Virtex

- •Содержание

Семейство VirtexTM

R

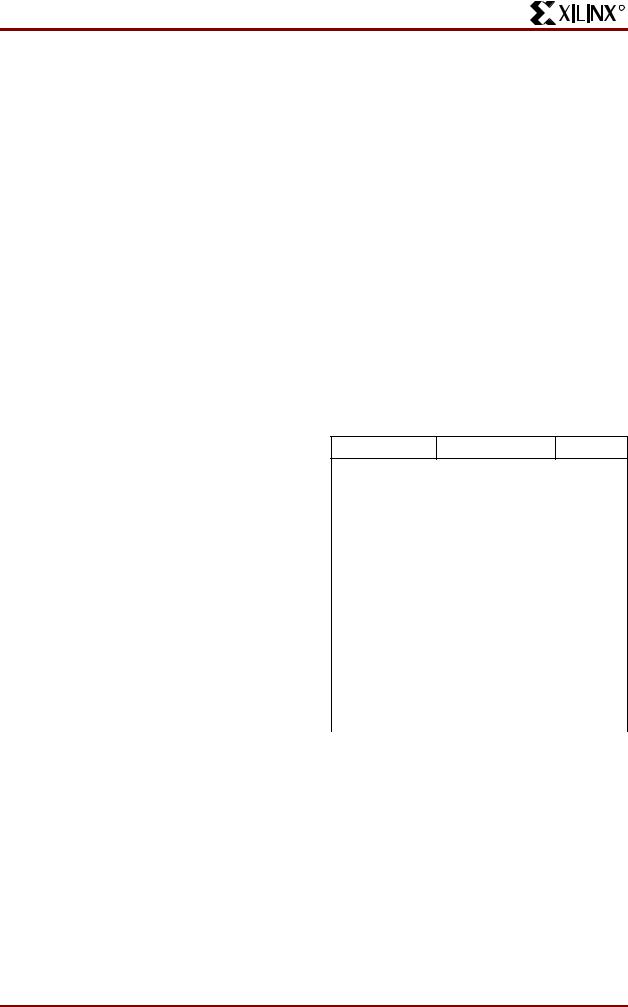

Табл. 1. Основные характеристики семейства Virtex

Тип МС |

Системные |

Матрица |

Логические |

Число доступных вхо- |

Блочная па- |

Память на ба- |

|

вентили |

КЛБ |

ячейки |

дов-выходов, макс. |

мять, Бит |

зе LUT, Бит |

XCV50 |

57 906 |

16x24 |

1 728 |

180 |

32 768 |

24 576 |

XCV100 |

108 904 |

20x30 |

2 700 |

180 |

40 960 |

38 400 |

XCV150 |

164 674 |

24x36 |

3 888 |

260 |

49 152 |

55 296 |

XCV200 |

236 666 |

28x42 |

5 292 |

284 |

57 344 |

75 264 |

XCV300 |

322 970 |

32x48 |

6 912 |

316 |

65 536 |

98 304 |

XCV400 |

468 252 |

40x60 |

10 800 |

404 |

81 920 |

153 600 |

XCV600 |

661 111 |

48x72 |

15 552 |

512 |

98 304 |

221 184 |

XCV800 |

888 439 |

56x84 |

21 168 |

512 |

114 688 |

301 056 |

XCV1000 |

1 124 022 |

64x96 |

27 648 |

512 |

131 072 |

393 216 |

Архитектура Virtex

Основными особенностями архитектуры кристаллов семейства Virtex являются гибкость и регулярность. Кристаллы состоят из матрицы КЛБ (Конфигурируемый Логический Блок), которая окружена программируемыми блоками ввода-вывода (БВВ). Все соединения между основными элемента (КЛБ, БВВ) осуществляются с помощью набора иерархических высокоскоростных программируемых трассировочных ресурсов. Изобилие таких ресурсов позволяет реализовывать на кристалле семейства Virtex даже самые громоздкие и сложные проекты.

Кристаллы семейства Virtex производятся на осно-

ве статического ОЗУ (Static Random Access Memory

– SRAM), поэтому функционирование кристаллов определяется загружаемыми во внутренние ячейки памяти конфигурационными данными. Конфигурационные данные могут загружаться в кристалл несколькими способами. В ведущем последовательном режиме (Master Serial) загрузка осуществляется из внешнего ПЗУ и полностью управляется самой FPGA Virtex. В других режимах управление загрузкой осуществляется внешними устройствами (режимы Select-MAPTM, подчиненный последова-

тельный (Slave Serial) и JTAG).

Конфигурационные данные создаются пользователем при помощи программного обеспечения проек-

тирования Xilinx FoundationTM и Alliance Series. Про-

граммное обеспечение включает в себя схемный и текстовый ввод, моделирование, автоматическое и ручное размещение и трассировку, создание, загрузку и верификацию загрузочных данных.

200 МГц. В Табл. 2 представлены производительности некоторых стандартных функций, реализованных на кристаллах с градацией быстродействия

‘6’.

В отличие от предыдущих семейств ПЛИС Xilinx, в сериях VirtexTM и SpartanTM градация по быстродействию обозначается классом, а не задержкой на логическую ячейку. Соответственно, в семействах VirtexTM и SpartanTM чем больше класс, тем выше быстродействие.

Табл. 2. Производительность стандартных функций.

Функция Разрядность, [Бит] Virtex-6

Внутрикристальная производительность

Сумматор |

16 |

5.0 нс. |

|

64 |

7.2 нс. |

||

|

|||

Конвейерный ум- |

8x8 |

5.1 нс. |

|

ножитель |

16x16 |

6.0 нс. |

|

Декодер адреса |

16 |

4.4 нс. |

|

64 |

6.4 нс. |

||

|

|||

Мультиплексор |

16:1 |

5.4 нс. |

|

Схема контроля |

9 |

4.1 нс. |

|

18 |

5.0 нс. |

||

по четности |

|||

36 |

6.9 нс. |

||

|

|||

Системная производительность |

|

||

Стандарт HSTL |

|

200 МГц |

|

Class IV |

|

||

|

|

||

Стандарт LVTTL |

|

180 МГц |

|

Быстродействие

Кристаллы Virtex обеспечивают более высокую производительность, чем предыдущие поколения FPGA. Проекты могут работать на системных частотах до 200 МГц, включая блоки ввода-вывода. Блоки ввода-вывода Virtex полностью соответствуют спецификациям PCI шины, поэтому кристалл позволяют реализовывать интерфейсные схемы, работающие на частоте 33 МГц или 66 МГц. В дополнение к этому кристаллы Virtex удовлетворяют требованию hot-swap для Compact PCI.

К настоящему времени кристаллы полностью протестированы на “эталонных” схемах. На основе тестов выявлено, что хотя производительность сильно зависит от конкретного проекта, большинство проектов работают на частотах превышающих 100 МГц и могут достигать системных частот до

Описание архитектуры

Матрица Virtex

Программируемая пользователем вентильная матрица серии Virtex показана на Рис.1. Соединение между КЛБ осуществляется с помощью главных трассировочных матриц - ГТМ. ГТМ - это матрица программируемых транзисторных двунаправленных переключателей, расположенных на пересечении горизонтальных и вертикальных линий связи. Каждый КЛБ окружен локальными линиями связи (VersaBlockTM), которые позволяют осуществить соединения с матрицей ГТМ.

Интерфейс ввода-вывода VersaRing создает дополнительные трассировочные ресурсы по пери-

2 |

1 февраля 2001 г. Краткое техническое описание |